IP

IP(intellectual property)指的是FPGA厂商具有知识产权的逻辑电路模块,这些模块往往很常用。工程师不需要在进行芯片设计时,额外重复设计出来的常用逻辑功能电路。每个厂商提供的IP核都不同,但是常用的模块大同小异。这一些逻辑电路模块,通过设置参数和例化被用户所用。

PLL锁相环

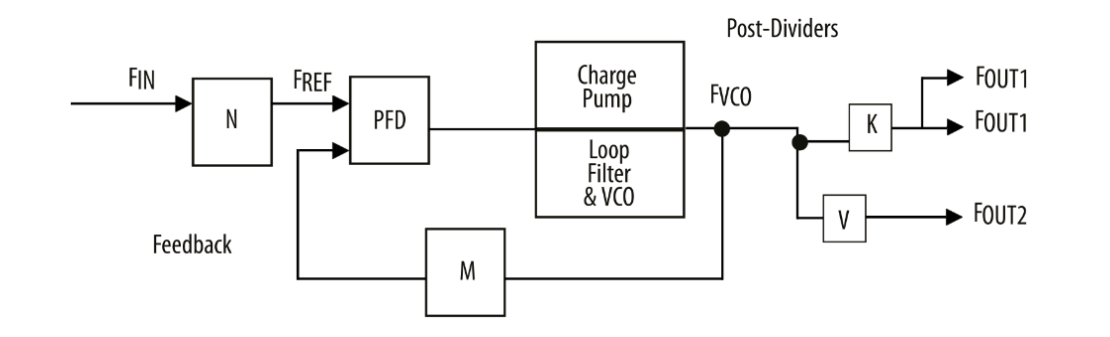

锁相环是一种带有反馈控制的电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。结构图如下:

基于EP4CE6E22C8N的PLL,通过在quartus里面添加和设定参数,即可添加到工程当中,这个PLL所产生的时钟信号,比自己设计出来的倍频或者分频逻辑电路更加准确,稳定。通常在一些工作频率比较高的系统,所需要的时钟频率也就越高。 电路板上的50Mhz明显不够,这时候就需要通过PLL把频率倍频出更加高的时钟信号。但是这个倍频并不是无限大的,若需要更大的时钟输出,则要求PLL输入的时钟不能太低。

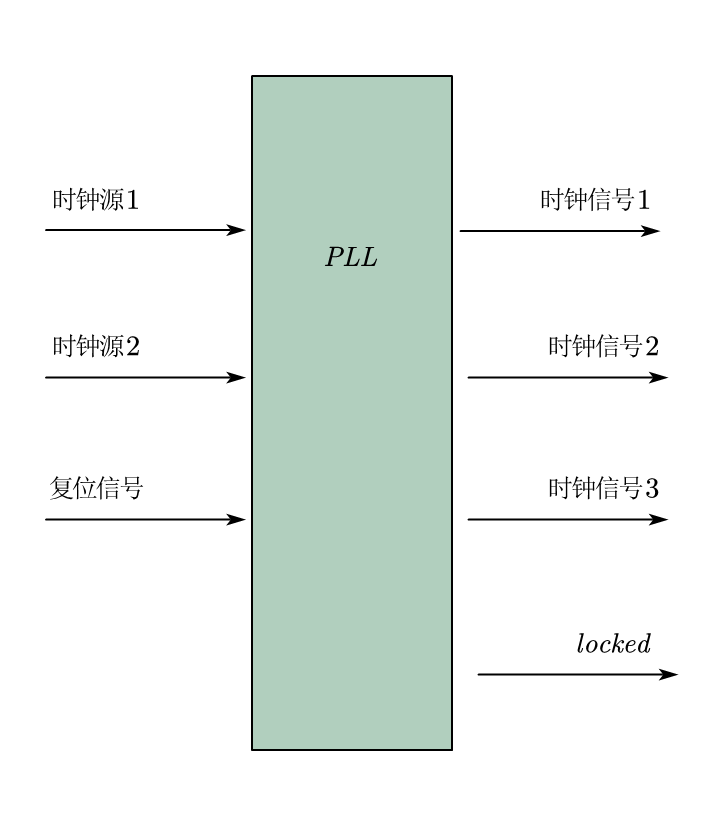

上图所示是一个PLL,可以有1~2个时钟源作为输入,带有一个复位信号输入。输出的时钟频率可以比输入时钟频率高(倍频)或者更低(分频),又或者将信号进行偏移处理。

仿真结果

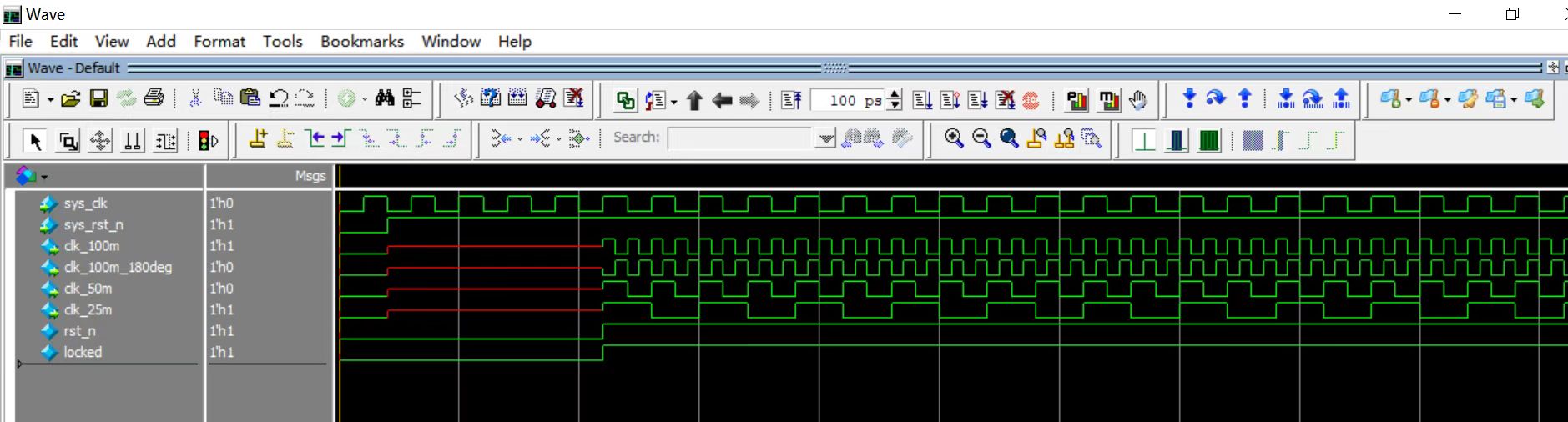

因为没有示波器,在quartus里面写好代码也没用。所以这里用了modelsim进行仿真。

注意:在仿真的时候,需要添加仿真文件:altera_mf.v,工程在生成时,里面还需要添加这个ip核的子文件。

这个PLL输入的是50Mhz,输出一个是100Mhz,一个偏移180°的100Mhz,一个输出50Mhz,一个25Mhz。由图中可以看到,输出的时钟源有一部分时间处于不定态。是因为PLL中多个门级电路组成产生的延时,后续根据输出时钟驱动的设备需要根据locked信号线是否拉高决定是否启动。 这个就是locked的用处。

IP核:PLL学习

IP核:PLL学习

浙公网安备 33010602011771号

浙公网安备 33010602011771号