Verilog代码中的标志位

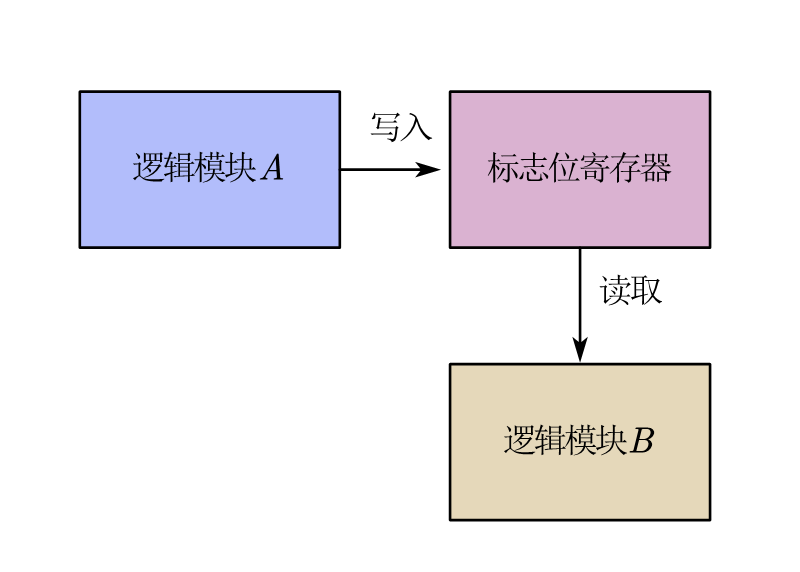

和软件语言一样,硬件描述语言也可以设置标志位。在HDL中,标志位被描述成寄存器。

一般地,标志位定义的数据类型是reg。可以根据实际需求,设置1~32位寄存器表示所需要表示的数数位。这一个功能被广泛应用在状态机场合。

“输入寄存器”

Verilog里面不存在输入寄存器这个概念。因为把输入信号定义成reg类型,发现会报错。 但是如果需要输入一个类似与寄存器信号的效果,可以定义成以下例子所示样子:

input [3:0] key, //按键输入信号

这里表示了4条信号线一并输入的效果,类似于并行的样子,可以理解为51单片机和LCD通信所用的并行通信原理一样。 在查询输入信号的时候,可以查询单独位,或者这些并行信号的组合。但是,输出寄存器在Verilog里面是存在的,可以编译出来。

“一切基于时钟信号”

在很多控制器,CPU,甚至一些芯片等,都是根据时钟信号工作的。很多教程里面讲到,时钟是芯片的心脏, 是因为无论裸机开发还是跑系统,都离不开最基本的滴答时钟。系统中断依靠时钟,端口工作频率依靠时钟分频或者倍频获得,系统时间片依靠时钟,连阻塞循环都需要时钟计时。只要有时序逻辑的工作要求,就需要时钟。(注:有的芯片最小系统板外面面没有时钟电路,是因为这些芯片内部集成了RC时钟。)

编程思想

同样,FPGA里面只要用到时序逻辑就需要时钟信号输入。因为FPGA是并行运行的,如果要实现软件语言里面的循环执行,就需要always语句的执行。 例子:

always @ (posedge sys_clk or negedge sys_rst_n) begin

......

end

时钟信号每次上升沿都会“激活”always语句的判断条件, 并且进入该语句执行对应的代码。因为时钟信号是固定频率的高低电平交替信号,相当于软件代码里面每次时间一到(时钟上升或者下降沿到达),就对循环体里面的代码跑一遍。

--时钟信号、“标志位寄存器”、“输入寄存器”

--时钟信号、“标志位寄存器”、“输入寄存器”

浙公网安备 33010602011771号

浙公网安备 33010602011771号