JESD204 介绍 接口介绍

1.高速数字接口标准:

目前,三个最高速使用的常见数字输出类型转换器是互补金属氧化物半导体(CMOS),低压差分信号(LVDS),和电流模式逻辑(CML)。

这些数字输出类型中的每一个在 ADC 中使用有其优点和缺点,取决于采样率和分辨率ADC、输出数据速率、功率要求系统设计等。

CMOS数字输出驱动:

在采样率低于 200 MSPS 的 ADC 中,这很常见。

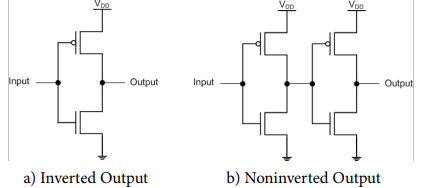

典型的 CMOS驱动器采用由两个晶体管,一个NMOS和一个PMOS,连接在电源(VDD)和

接地,如图 1a 所示。这种结构导致在输出中反转,因此作为替代方案,可以使用图 1b 中的背靠背结构以避免输出中的反转。

CMOS输出的输入驱动器为高阻抗,而输出为低阻抗。在驱动器的输入端,栅极的阻抗两个 CMOS 晶体管是相当高的。

输入端的阻抗范围可以从千欧到兆欧。在驱动器的输出端,阻抗由漏极电流 ID决定,通常很小。在这种情况下,阻抗通常小于几百欧姆。

CMOS 的电压电平从大约 VDD 摆动到地面,因此可以很大,具体取决于VDD的幅度。

由于输入阻抗高而输出阻抗相对较低,CMOS 的一个优点是输出通常可以驱动多个 CMOS 输入。CMOS静态电流低。

低压差分信号 (LVDS)

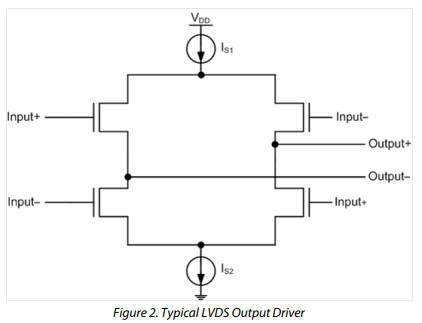

与 CMOS 技术相比,LVDS 提供了一些不错的优势。 它 以大约 350 mV 的低电压信号工作, 并且是差分。 较低的电压 swing 具有更快的开关时间并减少了 EMI 问题。 由于是差分的,还具有共模抑制的好处。

LVDS 中的阻抗需要更严格地控制。 在 LVDS,负载电阻需要大约 100 Ω 并且通常是通过一个并联端接电阻在 LVDS 接收器。 此外,LVDS信号需要 使用受控阻抗传输线进行路由。 这 所需的单端阻抗为 50 Ω,而差分 阻抗保持在 100 Ω。 图 2 显示了典型的 LVDS 输出驱动器

CML 输出驱动器

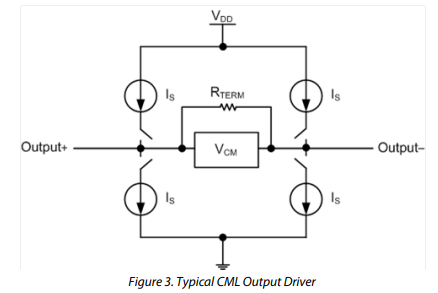

CML输出驱动器用于最新转换器上使用的 JESD204 接口。

使用带有序列化 JESD204 接口的 CML 驱动程序允许转换器输出上的数据速率高达 12 Gbps。

下图 显示用于带有 JESD204 的转换器的典型 CML 驱动器。源端接电阻和共模电压。电路的输入将开关驱动到电流将适当的逻辑值驱动到两个源输出端子。

Link parameters

| L | Lane Count |

| M | Converter Count |

| F | Octets per Frame per Lane |

| S | Samples per Converter per Frame |

| NP | Total Number of Bits per Sample |

| N | Converter Resolution |

| K | Frames per Multiframe |

| HD | High Density User Data Format |

| E | Number of multiblocks in an extended multiblock |

| L | lane数 |

| M | 转换器数量 |

| F | 每帧每通道八位字节 |

| S | 每个转换器每帧的点数 |

| NP | 每个样本的总位数 |

| N | 转换器分辨率 |

| K | 每多帧的帧数 |

| HD | 高密度用户数据格式 |

| E | 扩展多块中的多块数 |

浙公网安备 33010602011771号

浙公网安备 33010602011771号