usb工业相机之硬件设计-双缓冲-双端口sdram-fpga

usb工业相机之硬件设计-双缓冲-双端口sdram-fpga

在前期的产品设计中,采用cb提供的结构,68013直接操作摄像头,iic配置摄像头寄存器,板载晶振提供时钟,摄像头的pclk直接接ifclk。

这样的好处在于成本最低,

缺点是帧率有限,实测ov7725及ov7670 在raw格式下帧率最高在50fps左右,再高就有错位了。

因为fifo时钟有限值,最高是48Mhz,所以pclk不能高于48Mhz,其实在24Mhz以上就很难工作稳定了,因为无fpga控制,写入fifo数据,未按时读出,导致溢出,以至于数据丢失。。

所以像素也很难提高,目前实测最高像素为1280*1024 帧率约8fps。

于是不得不进行以下设计

1、fifo控制,写fifo的时候满判断,如果写满,则停止写入

2、而sensor是主动时钟,像素持续输出,如68013的fifo写满,则应把当前的数据缓存起来,

3、因为各自sensor像素尺寸不同,需要缓存的像素大小不确定,所以按照最大处理,不得不选择sdram,至少可以存1副完整图片

参考cb VGA—sdram例程

双端口sdram

coms写端口

68013读端口

68013 ifclk时钟=读时钟

68013的fifo满的时候,禁止读端口使能,即终止对68013发数据,待到满标志结束又继续开始

此模型实现的是异步读写,即摄像头的帧率不等于显示的帧率。显示的帧率与usb设备或电脑相关,性能好即帧率高

实测

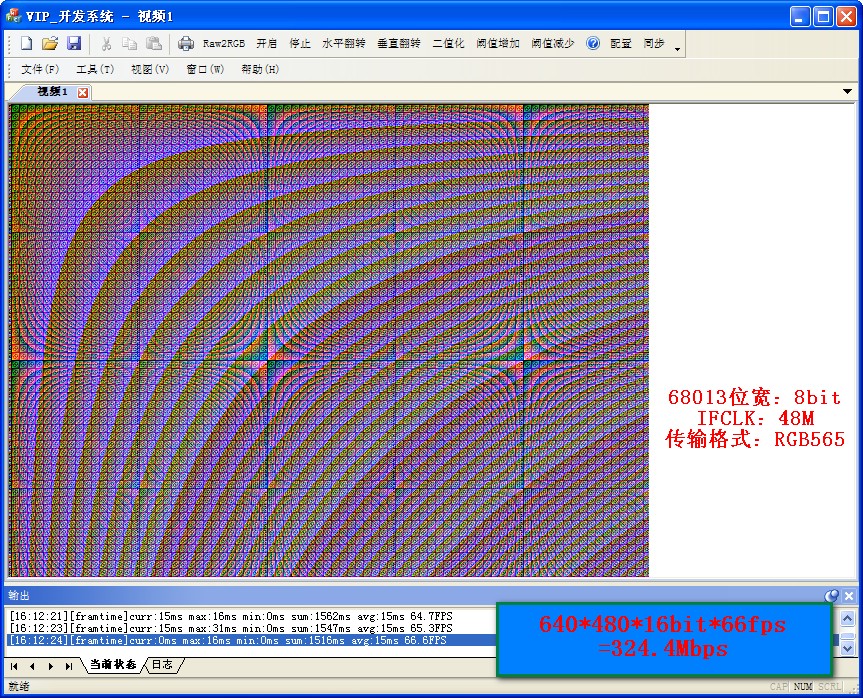

VGA模式 16bit rgb565 帧率可达 66fps raw格式即可达132fps,基本达到预期效果,上图为使用模拟数据测试效果。

昨天和老许折腾一天,终于搞定,感谢网友:许-sir 提供fpga程序支持!

参考硬件

http://item.taobao.com/item.htm?spm=a1z10.3-c.w4002-2707874652.27.fvFevQ&id=43769007820

下载资料:

链接:http://pan.baidu.com/s/1sjqhcoH 密码:i609 【手册】

浙公网安备 33010602011771号

浙公网安备 33010602011771号