使用fpga实现网络传输,phy芯片选型及适配,RMII,GRMII,MII等不同模式学习(dp83848,RTL8201,LAN8720)

PHY芯片 LAN8742A,LAN8720A(只支持RMII),DP83848(RMII/MII),RTL8201(MII)

使用RMII,时钟需要提供50Mhz

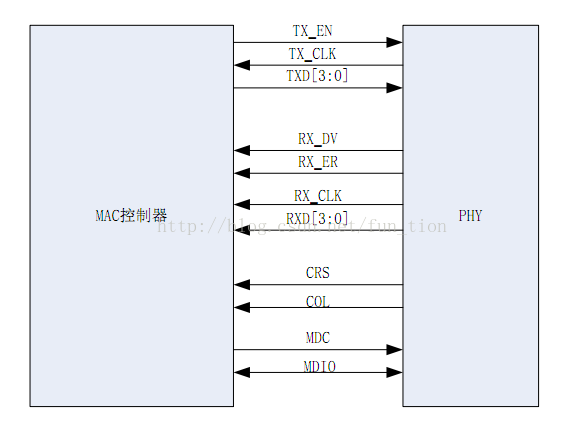

MII模式(10M或者100M)

MII_TX_CLK:发送数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

MII_RX_CLK:接收数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

MII_TX_EN:传输使能信号,此信号必需与数据前导符的起始位同步出现,并在传输完毕前一直保持。

MII_TXD[3:0]:发送数据线,每次传输4位数据,数据在MII_TX_EN信号有效时有效。MII_TXD[0]是数据的最低位,MII_TXD[3]是最高位。当MII_TX_EN信号无效时,PHY忽略传输的数据。

MII_CRS:载波侦听信号,仅工作在半双工模式下,由PHY控制,当发送或接收的介质非空闲时,使能此信号。 PHY必需保证MII_CRS信号在发生冲突的整个时间段内都保持有效,不需要此信号与发送/接收的时钟同步。

MII_COL:冲突检测信号,仅工作在半双工模式下,由PHY控制,当检测到介质发生冲突时,使能此信号,并且在整个冲突的持续时间内,保持此信号有效。此信号不需要和发送/接收的时钟同步。

MII_RXD[3:0]:接收数据线,每次接收4位数据,数据在MII_RX_DV信号有效时有效。MII_RXD[0]是数据的最低位,MII_RXD[3]是最高位。当MII_RX_EN无效,而MII_RX_ER有效时,MII_RXD[3:0]数据值代表特定的信息(请参考表194)。

MII_RX_DV:接收数据使能信号,由PHY控制,当PHY准备好数据供MAC接收时,使能该信号。此信号必需和帧数据的首位同步出现,并保持有效直到数据传输完成。在传送最后4位数据后的第一个时钟之前,此信号必需变为无效状态。为了正确的接收一个帧,有效电平不能滞后于数据线上的SFD位出现。

MII_RX_ER:接收出错信号,保持一个或多个时钟周期(MII_RX_CLK)的有效状态,表明MAC在接收过程中检测到错误。具体错误原因需配合MII_RX_DV的状态及MII_RXD[3:0]的数据值。

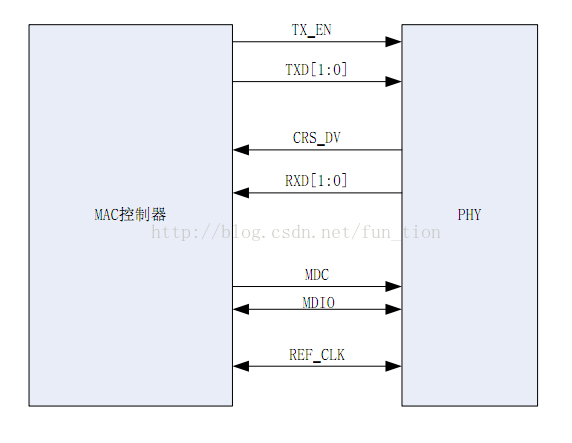

精简的独立于介质的接口(RMII)

精简的独立于介质接口(RMII)规范减少了以太网通信所需要的引脚数。根据IEEE802.3标准,MII接口需要16个数据和控制信号引脚,而RMII标准则将引脚数减少到了7个。RMII具有以下特性:

时钟信号需要提高到50MHz。

MAC和外部的以太网PHY需要使用同样的时钟源

使用2位宽度的数据收发

RMII的信号线如下图所示:

5.时钟源

1)MII时钟源

为了产生TX_CLK和RX_CLK时钟信号,外接的PHY模块必需有来自外部的25MHz时钟驱动。该时钟不需要与MAC时钟相同。可以使用外部的25MHz晶体或者微控制器的MCO引脚提供这一时钟。当时钟来源MCO引脚时需配置合适的PLL,保证MCO引脚输出的时钟为25MHZ。

2)RMII时钟源

通过将相同的时钟源接到MAC和以太网PHY的REF_CLK引脚保证两者时钟源的同步。可以通过外部的50MHZ信号或微控制器的MCO引脚提供这一时钟。当时钟来源MCO引脚时需配置合适的PLL,保证MCO引脚输出的时钟为50MHZ。

3)总结

采用MII接口,PYH的时钟频率要求25M,不需要与MAC层时钟一致。

采用RMII接口,PYH的时钟频率要求50M,需与MAC层时钟一致,通常从MAC层获取该时钟源。

RMII与MII的对比

| 特性 | RMII | MII |

|---|---|---|

| 引脚数量 | 7个(数据+控制) | 16个(数据+控制+时钟) |

| 时钟频率 | 50MHz(统一时钟) | 25MHz(100Mbps) / 2.5MHz(10M) |

| 数据位宽 | 2位(每个周期2比特) | 4位(每个周期4比特) |

| 功耗 | 较低(简化电路) | 较高 |

| 适用场景 | 低成本、嵌入式系统 | 传统网络设备 |

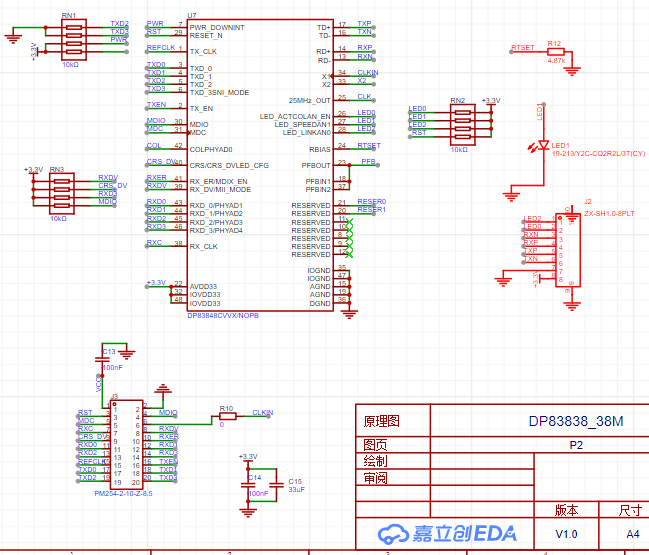

设计dp83848图纸

工作模式:由39号和7号引脚电平决定

| PIN39 | PIN7 | 模式 |

| 0 | X | MII |

| 1 | 0 | RMII |

| 1 | 1 | 10MB SNI MODE |

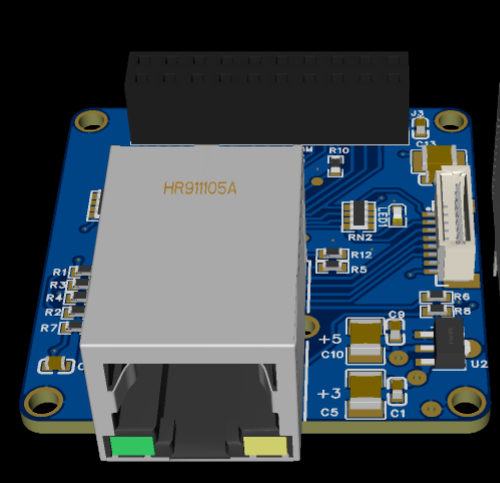

模块将所有io均引出,方便配置rmii和mii模式进行验证。

有兴趣的朋友可以去淘宝搜:图像专家采购,也可以自行制作 首页-层层惊涛设计室 柴草电子-淘宝网 (taobao.com)

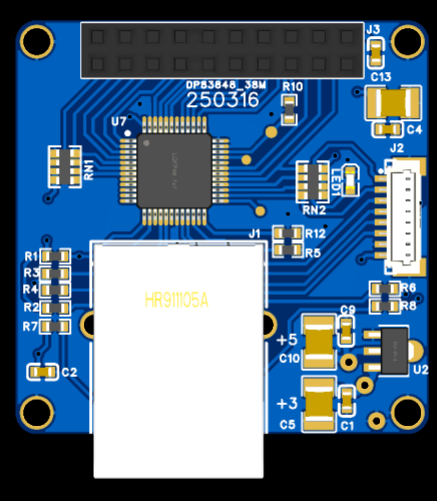

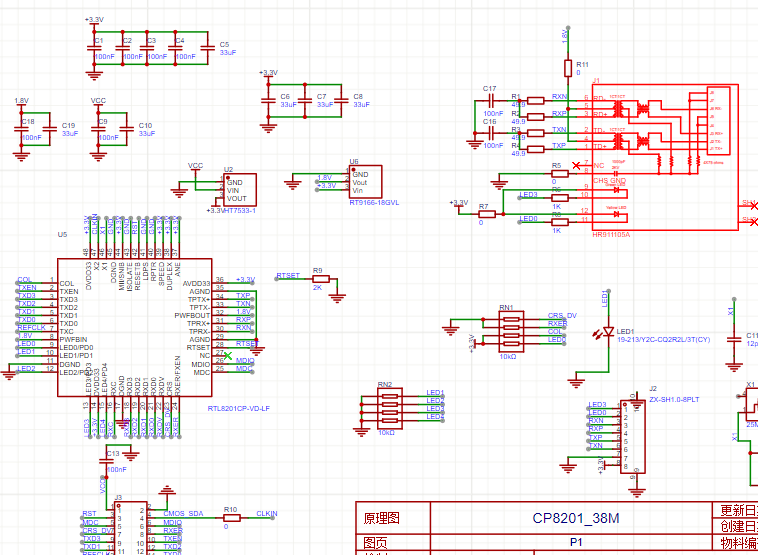

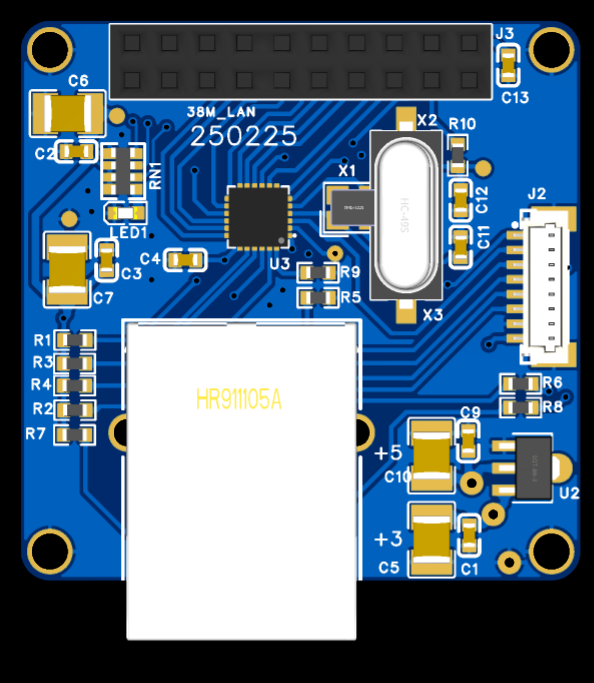

RTL8201芯片网络模块,仅支持MII,时钟25Mhz

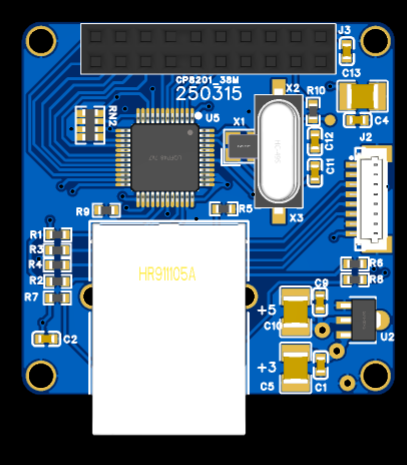

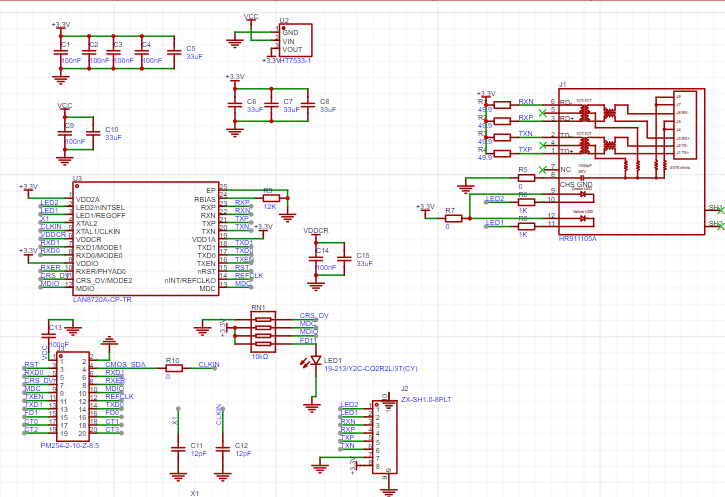

LAN8720模块,仅支持RMII,时钟为50Mhz,

编写fpga程序测试

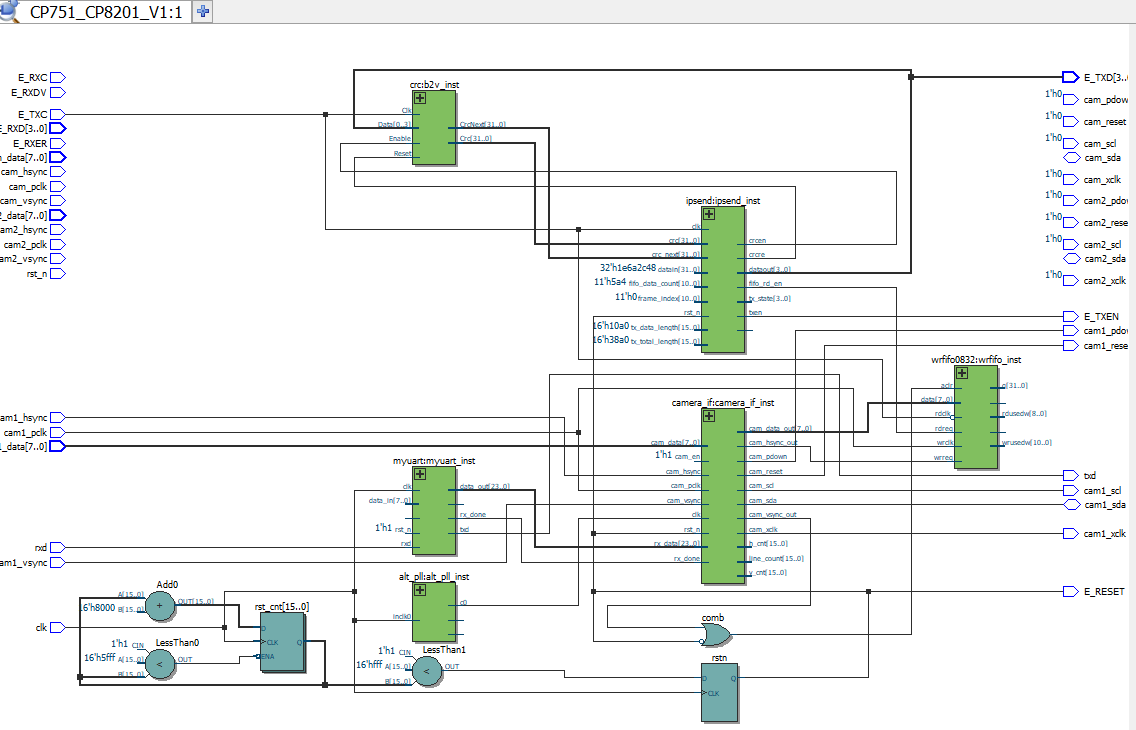

使用摄像头传输模块,摄像头的数据通过fifo缓冲,8bit转为32bit,由mii接口发出

当前没装摄像头,先将数据固定测试网口正常

ipsend ipsend_inst

(

.clk(E_TXC ) , // input clk

.txen(E_TXEN ) , // output txen

.txer() , // output txer

.dataout(E_TXD ) , // output [4:0] dataout

.rst_n(rstn ) , // input rst_n

.crc(crc ) , // input [31:0] crc

.crc_next(crc_next),

.crcen(crcen ) , // output crcen

.crcre(crcre ) , // output crcre

.datain(32'h12345678 ) , // input [31:0] datain

.fifo_data_count(301 ) , // input [10:0] fifo_data_count

.fifo_rd_en(fifo_rd_en ) , // output fifo_rd_en

.frame_index(frame_index ) , // input [10:0] frame_index

.tx_state(tx_state ) , // output [3:0] tx_state

.tx_data_length(tx_data_length ) , // input [15:0] tx_data_length

.tx_total_length(tx_total_length ) // input [15:0] tx_total_length

);

crc b2v_inst(

.Clk(E_TXC),

.Reset(crcre),

.Enable(crcen),

.Data(E_TXD),

.Crc(crc),

.CrcNext(crc_next)

);

assign E_RESET = rstn;

连续固定发送 0x12345678

因为没有做延时处理,网络调试助手收到大量的,重复的0x12345678数据。

如果需要做延时修改也非常简单,可以定时的给fifo填充数据,比如1秒填充10个

速度就能降低下来方便观察

当然也可以直接使用摄像头测试,

同时也需要写一个上位机软件方便观察视频

下一章节继续

浙公网安备 33010602011771号

浙公网安备 33010602011771号