Verilog (FPGA)板级实验—Quartus II

这是第一个例子将会在硬件实验板演示我们的设计。本节的目的不是给大家介绍复杂的设计工程,复杂的设计方法,而是借助一个简单的例子,介绍如何将整个设计流程介绍给大家。本节内容包括新建文件,编写Verilog 代码,将代码添加到工程中,编译,开发板相关硬件介绍,管脚锁定,编程下载,板级验证。我们将按照这套流程一步步教会FPGA(Verilog)的开发流程。

- 开发板 FII-PRA 006/010

- Quartus II 新建工程

- 新建文件,编写Verilog 代码

按照Quartus II 新建工程介绍,新建工程,工程名及顶层设计文件名都为fadd1 。

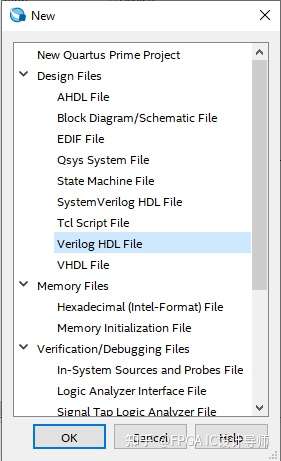

3.1新建verilog文件, 菜单File –> new, 打开对话框如图1,

图 1

在图1中选择Verilog HDL File, 点击OK。

在Quartus II 的编辑区,出现了待编辑的文件,文件名为 Verilog1.v,也可能verilog2.v 等,决定于之前操作过多少次新建文件。如图2,

图2

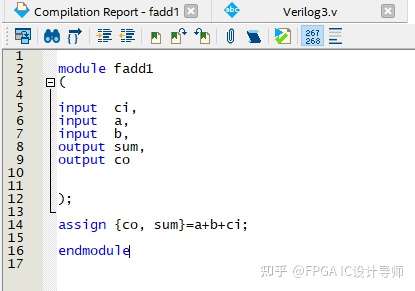

在图中编写 Verilog module 文件。如图3

图3

注:关键字module后的模块名称为 fadd1,这里要求模块名称,顶层文件名,顶层实体名,工程名要求一致,都为fadd1.

module fadd1

(

input ci,

input a,

input b,

output sum,

output co

);

assign {co, sum}=a+b+ci;

endmodule- 文件存储

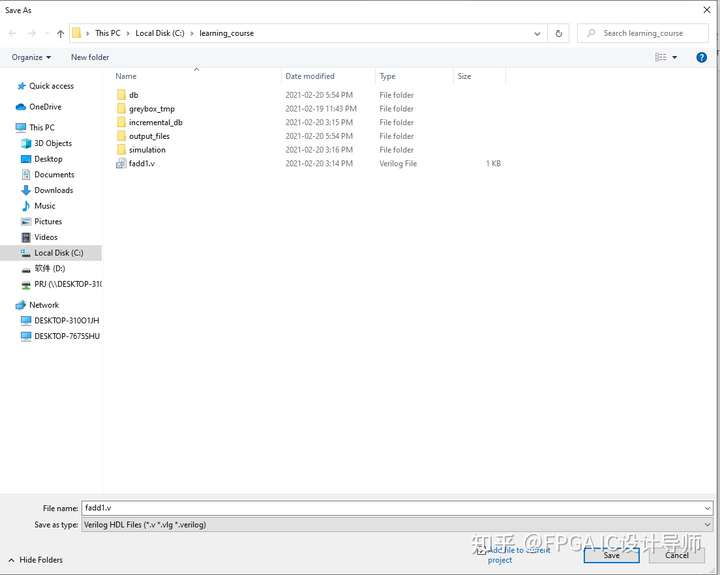

File–>save as… , 并存为fadd1.v , 如图4

图4

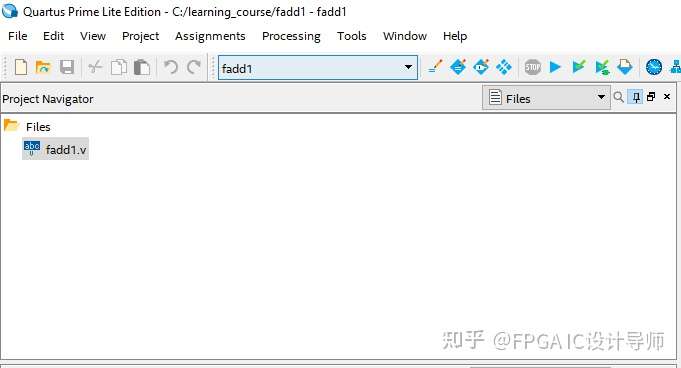

文件存储后,将会自动加入工程中。如图5,

图5

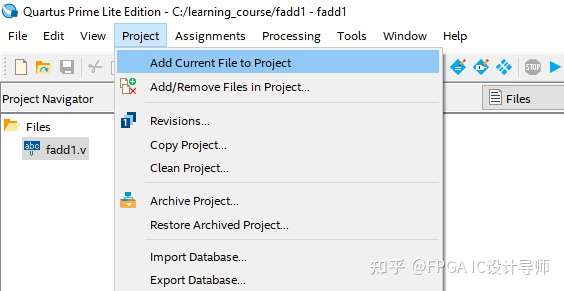

如果文件没有自动加入,也可以在菜单Project–>Add Current File to Project,将刚编辑的文件加入工程。也可以利用Project–> Add/Remove Files in Project…添加或移除文件。

图6

3.2编译过程

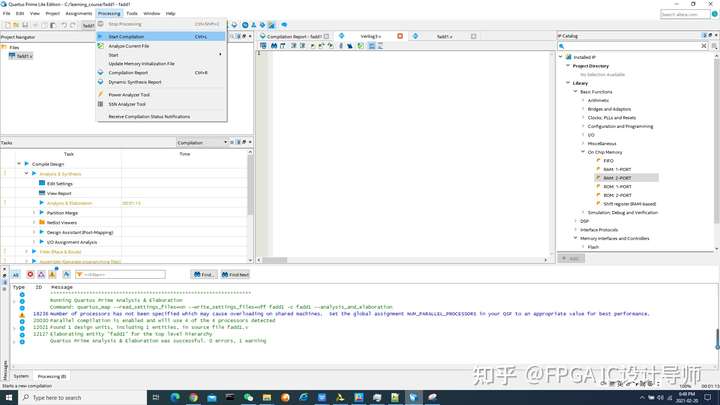

- 编译, 点击菜单Processing–>Start Compilation ,如图7

图7

或点击工具栏右箭头按钮,如图8

图8

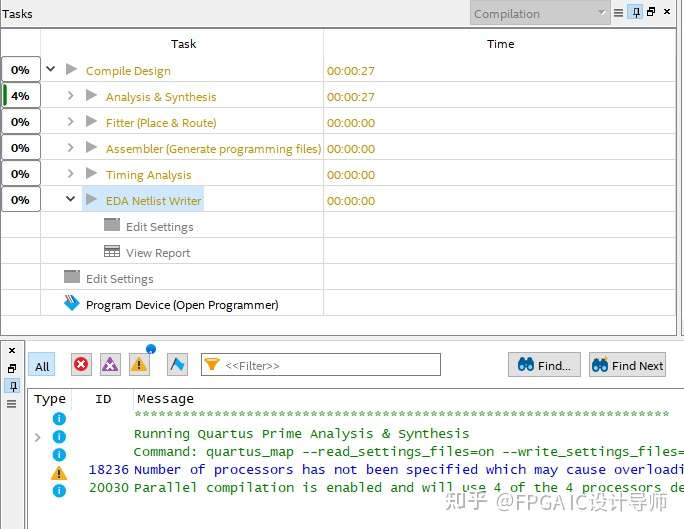

3.3编译进程,如图9

图9

- 开发板硬件相关部分介绍

- Quartus II 下 FPGA管脚锁定

- 重新编译

- 编程下载

- 板级验证

浙公网安备 33010602011771号

浙公网安备 33010602011771号