HDLbits的一点记录

4.Verification:Reading Simulations

4.1Finding bugs in code

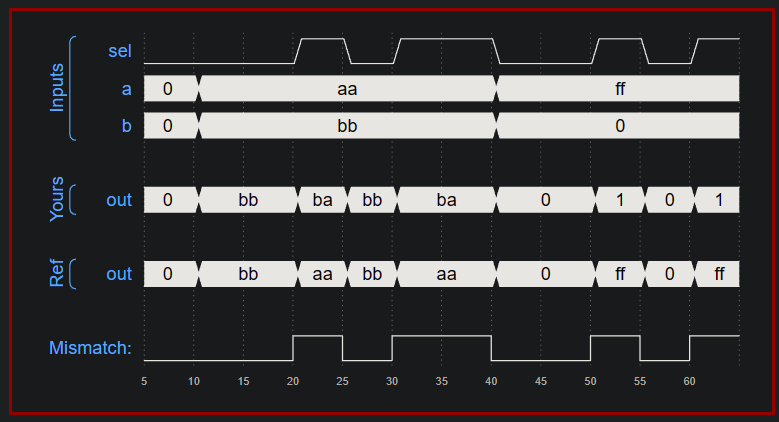

4.1.1Bugs Mux2

题目:

module top_module (

input sel,

input [7:0] a,

input [7:0] b,

output out ); //注:这里不要忘了修改为8bit

assign out = (~sel & a) | (sel & b);

endmodule

关于这题的解答比较简单。

assign out = sel?a:b; //Answer 1

//Answer 2

always @(*) begin

if(sel)

out = a;

else

out = b;

end

然而我就有了一种疑问——为什么assign out = (sel&a) | (~sel&b);不能用来描述8位2输入多路复用器?其实这牵涉到二进制码的补全/截短和取反谁优先级更高的问题。

这个对比表示问题出现于sel=1时。以a=8'h1010_1010,b=8'h1011_1011为例。

-

假设优先级:二进制码的补全/截短<取反,则~1=0000_0000,1=0000_0001。0000_0001&1010_1010=0000_0000,0000_0000&1011_1011=0000_0000,0000_0000|0000_0000=0000_0000。显然不对。

-

假设优先级:二进制码的补全/截短>取反,则~0000_0001=1111_1110,1=0000_0001。0000_0001&1010_1010=0000_0000,1111_1110&1011_1011=1011_1010,1011_1010|0000_0000=1011_1010。答案正确。

结论:优先级:二进制码的补全/截短>取反

如果改进一下,则会通过:

module top_module (

input sel,

input [7:0] a,

input [7:0] b,

output [7:0] out );

//该有的花括号不要少!!

assign out = ({8{sel}}&a) | (~{8{sel}}&b);

endmodule

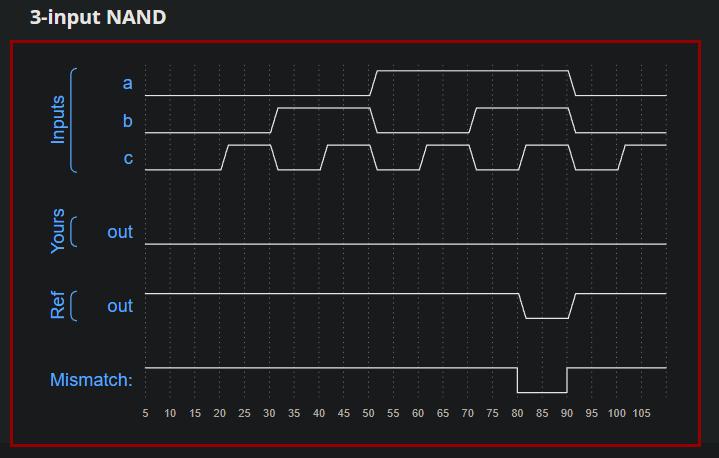

4.1.2Bugs nand3

题目:

module top_module (input a, input b, input c, output out);//

andgate inst1 ( a, b, c, out );

endmodule

解答:

module top_module (input a, input b, input c, output out);//

wire out_tmp;

assign out = ~out_tmp;

andgate inst1 ( out_tmp, a, b, c, 1, 1 );

endmodule

我的问题:

module top_module (input a, input b, input c, output out);//

andgate inst1 ( ~out, a, b, c, 1'b1, 1'b1 );

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号