【计组实验】实验f1 mux21a

一、实验目标

测试mux21a二选一多路选择器的功能,并做出仿真波形。

二、实验原理

用VHDL代码实现mux21a二选一多路选择器的功能,用Quartus Ⅱ编译代码并展示元件图,最后制造波形数据并进行波形仿真。

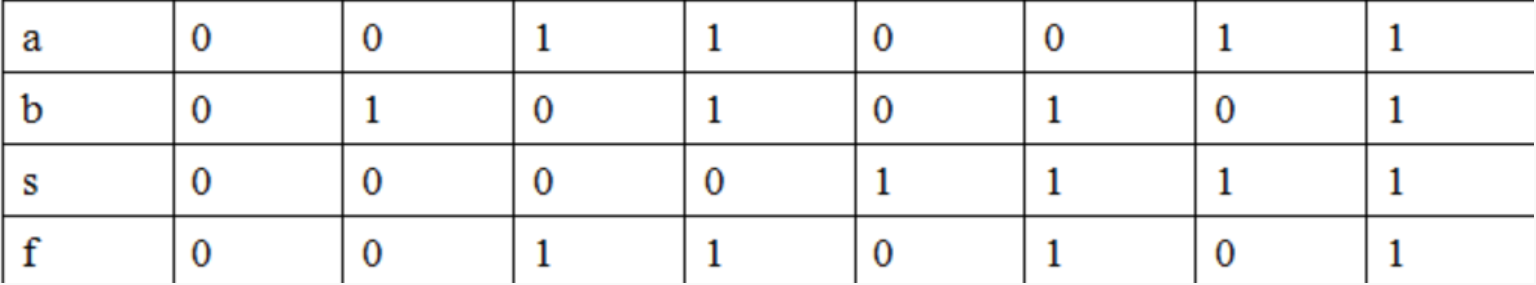

真值表

三、实验代码

mux21a二选一多路选择器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux21a IS

PORT ( a, b, s: IN STD_LOGIC;

y : OUT STD_LOGIC );

END ENTITY mux21a;

ARCHITECTURE one OF mux21a IS

BEGIN

PROCESS (a,b,s)

BEGIN

IF s = '0' THEN y <= a ; ELSE y <= b ;

END IF;

END PROCESS;

END ARCHITECTURE one ;

四、实验过程

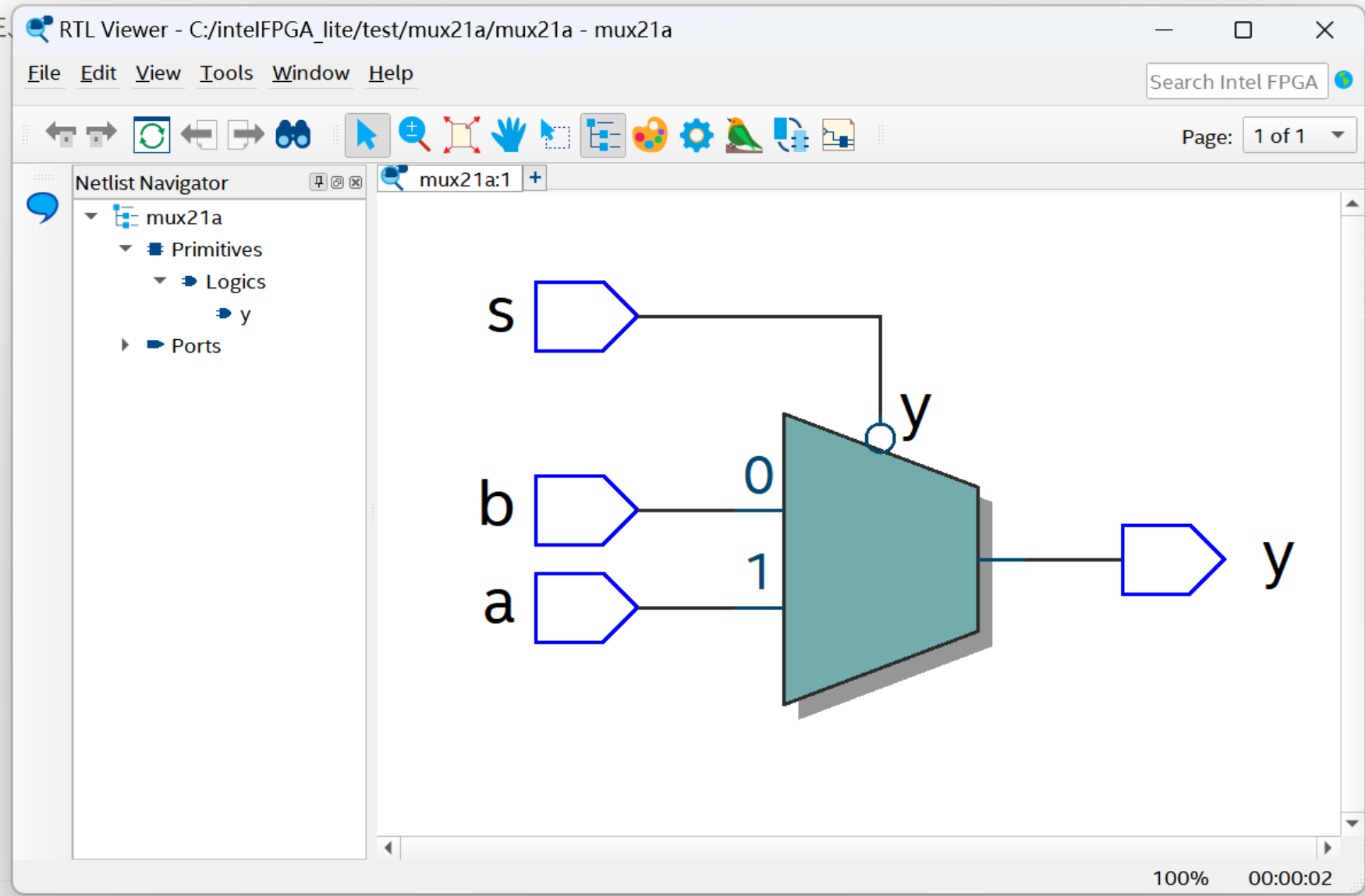

元件图

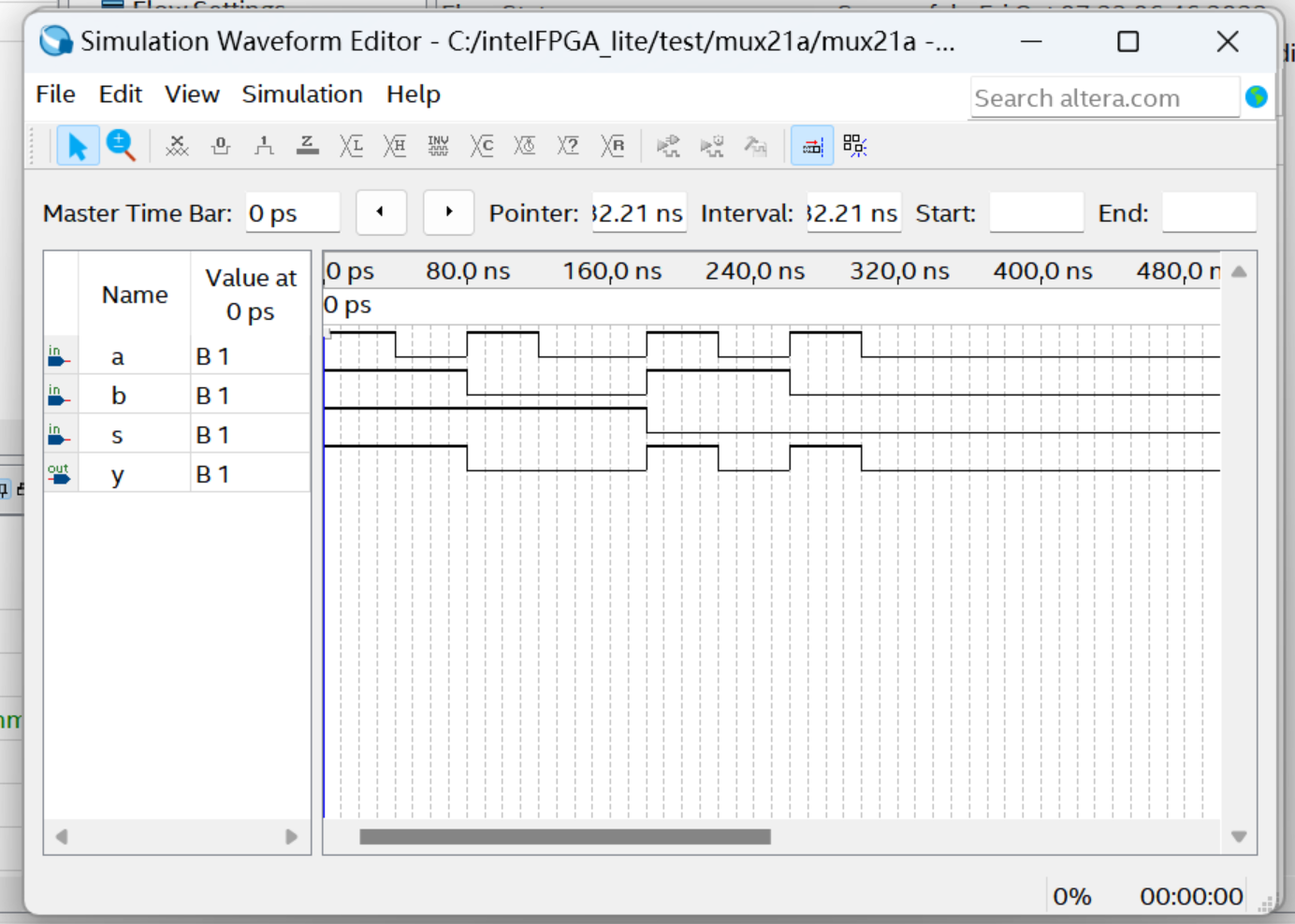

测试波形

测试:使用了8种不同高低电平组合,尽可能更清楚地得到无异议的实验结果。

测试结果:测试波形符合mux21a真值表。当输入端s为高电平时,输出端y输出的是输入端b的电平信号,反之则是输出输入端a的电平信号。

五、实验总结

此次是我第一次认识了vhdl这门语言,并学习使用vhdl编写实现mux21a二选一多路选择器的逻辑功能,同时学习使用了intel quartus设计测试平台对选择器的功能进行测试。在本次实验中,我学习到了设计逻辑电路的最基本流程,学习到了对波形进行调整的时序仿真的调试过程,也学习到了实验的规范流程,收获颇丰。在完成本次实验后,我对计组的兴趣越发浓郁,我切实感受到了来自计算机底层的逻辑魅力。

浙公网安备 33010602011771号

浙公网安备 33010602011771号