24.2 绘制原理图

File>New>Project>PCB Project对工程保存后

在File>New>Schematic新建原理图

在File>New>PCB新建PCB

设置交点:

DXP>Preferences>Schematic>Auto Junctions>Size

×意思是不进行规则检查

隐藏所有元器件名称:右键>Find Similar Objects

生成PCB:

先对原理图标号:Tools>annotate schmatics>Update Changes List>OK>Accept Changes>Validate Changes>Execute Changes

选择Design>Update PCB Document xxx.PcbDoc

点击Excute Changes

改变PCB板大小:

在Mechanical1设置原点Edit>Origin>SET然后画4000×4000的方框>Design>Board Shape>Define from selected objects

布线:

横平竖直:Top layer顶层平行走线;Bottom layer底层竖直走线,线越短越粗越好。

设计规则:

在*.PcbDoc中,设计布线规则,Design>Rule>

1.clearance线与过孔的距离>改大一点20mil(线在两个焊盘之间过不来可修改此数值)

2.Routing>Width>Min Width:10mil>Max width:50mil>Apply

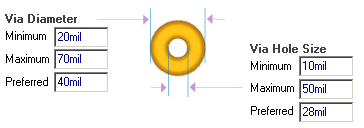

3.Routing Via Style>RoutingVias设置过孔大小

4.Manufacturing>SilkscreenOverComponentPads>0mil

5.Manufacturing>SilkToSilkClerance>0mil

6.Placement>Height>修改大小

在Top layer先画部分线再画过孔后切换到底层bottom layer

画完所有信号线后,修改线宽画VCC和GND,Routing>Width>Perferred Width:40mil>Apply或连接是按Tab设置线宽为40mil

Ctrl可以对线进行拖拽

铺铜:

Place>Ploygon Pour>Hatched(Tracks/Arcs)适用于只支持Protel的工厂,设置Track Width=Grid Size=10mil则可以将板子铺满>Net Options>Connect Net:GND>Pour Over All Same Net Objects>Layer(把底线和铜熔在一起)>Top Layer或Bottom Layer

规则检查:

Tools>Design Rule Check

Manufacturing> HoleSize>1000mil孔的直径改大即可

导出文件:

File>PCB 4.0Binary Files(Protel支持此格式)

书写版权:

在丝印层TopOverlay插入字串,Protel只识别stroke字体

Error Collection:

Processing Rule : Net Antennae (Tolerance=0mil) (All) Processing Rule : Silk to Silk (Clearance=0mil) (All),(All);修改元器件之间的距离 Processing Rule : Silkscreen Over Component Pads (Clearance=0mil) (All),(All);将顶层丝印与焊盘间的距离改小 Processing Rule : Minimum Solder Mask Sliver (Gap=0mil) (All),(All) Processing Rule : Hole To Hole Clearance (Gap=10mil) (All),(All) Processing Rule : Hole Size Constraint (Min=1mil) (Max=100mil) (All) Processing Rule:HeightConstraint(Min=0mil)(Max=1000mil)(Prefered=500mil) (All) Processing Rule : Width Constraint (Min=10mil) (Max=50mil) (Preferred=10mil) (All) Processing Rule : Power Plane Connect Rule(Relief Connect )(Expansion=20mil) (Conductor Width=10mil) (Air Gap=10mil) (Entries=4) (All) Processing Rule : Clearance Constraint (Gap=0mil) (All),(All) Processing Rule : Un-Routed Net Constraint ( (All) ) Processing Rule : Short-Circuit Constraint (Allowed=No) (All),(All);有未连接的元器件。

-------------------------------------------

文中所用软件在试用期内。若涉及商业用途或想有更好的用户体验,建议购买正版!

如果觉得这篇文章对您有小小帮助的话,记得在右下角点个“推荐”哦,博主在此万分感谢!

打赏请您扫下面二维码!谢谢!

|

|

浙公网安备 33010602011771号

浙公网安备 33010602011771号