Aurix 与DSP2000

对DSP2000 核 与 AURIX 核心的对比

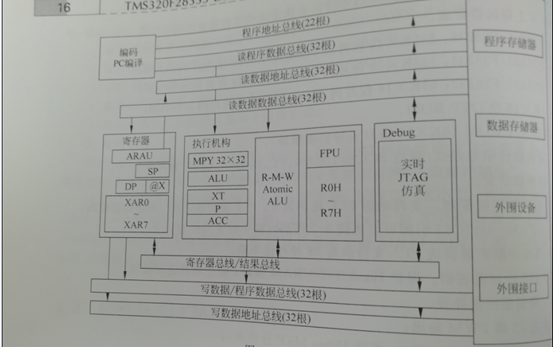

DSP总线的结构

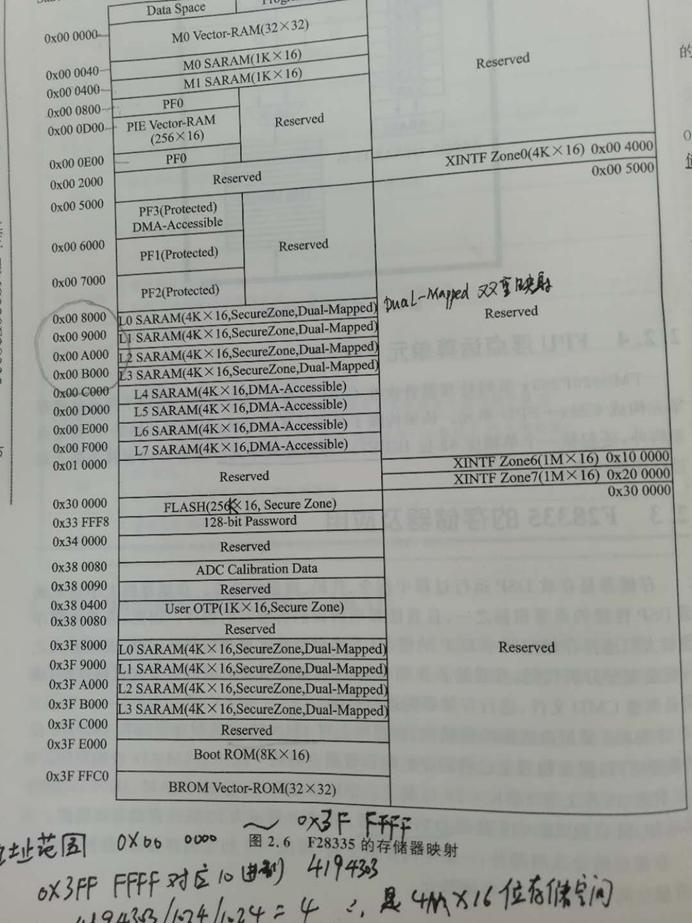

程序总线是22位 所以我看到的flash以及RAM的地址都是22位的

0X00 0000~ 0X3FFFF

0X3FFFFF 的 第20 位 21位 分别是 11

下图 显示程序地址总线是22位

注意到数据总线是32线的 但是我只用到了16位

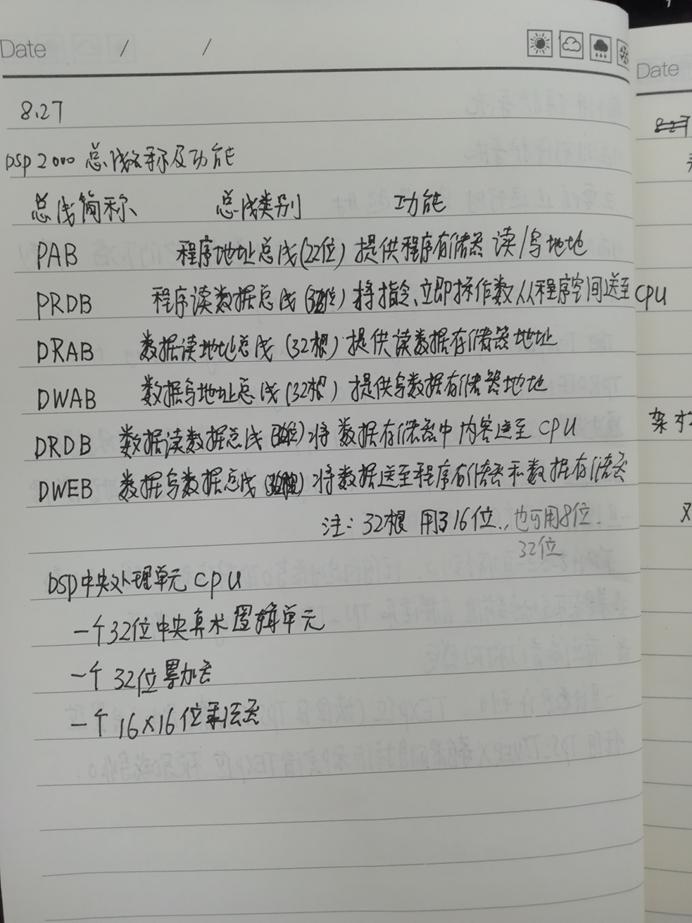

DSP的总线结构

DSP的中央处理单元是32位累加器 1个16 X 16 位乘法器

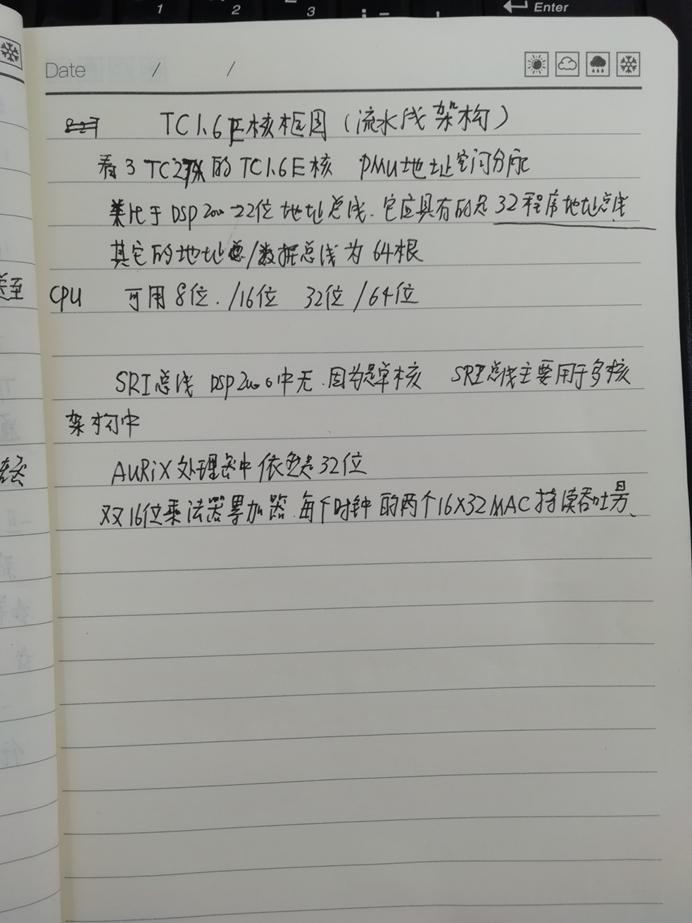

TRICORE 内核

从上图可知 AURIX的程序地址总线已经达到了 32位 而DSP 只用到22位

Aurix 的地址数据总线可以达到64根 。

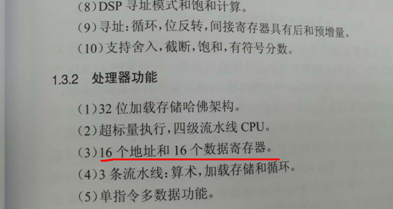

AURIX 的处理器功能中 提到16个地址寄存器 16个数据寄存器

这些寄存器都是64位宽的 ,可以两个组合成128位宽的,。

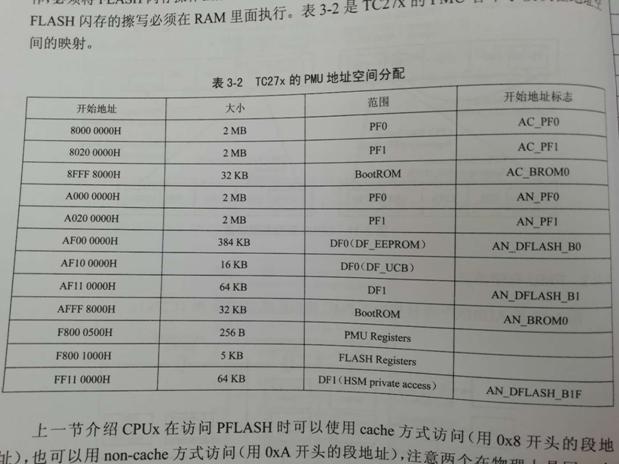

TC27X存储器地址的分布

SRI总线DS2000 中没有,因为 SRI总线主要是用在多核心的架构中

AURIX处理器中的核心依然是32位乘法器

双16位乘法器累加器 每个时钟的两个16X32MAC持续吞吐量

我想AURIX 与DSP 的FLASH 和RAM 的组成单元应该是相同 ,都是以16bit为基础

28335 中 是4 M X 16 bit 的寻址空间

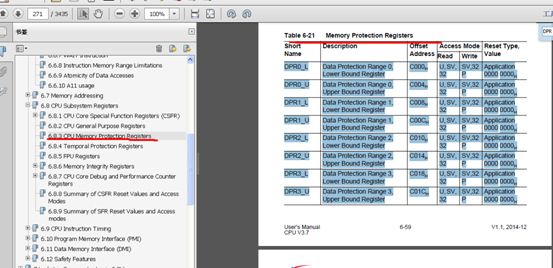

前面讲过 AURIX 存储器 可以分为SET0 SET1 SET2 SET3 4个域

而且这个4个域 每个域里面还可以 分为16个保护区间。

这个功能 有点像DSP2000 中的一些存储器受保护,必须用128位的密码进行打开那样

那我再指定任何一个保护域的范围区间的上限 与下限的时候

同DSP一样 内存是以16bit 为基本进行存放的,

所以一个保护区间范围 例如对SET0 中的某一区间 范围的上限的地址是64位

区间范围下限的地址 也是64位

所以偏移量就是4

DPR0_L 例如表示SET0 段 数据保护区间0范围的上限64位 (可以分为16个保护区间) 占用4个单元 | C000H |

C001H | |

C002H | |

C003H | |

DPR0_U 例如表示SET0 段 数据保护区间0范围的下限地址64位 (可以分为16个保护区间) 占用4个32位 4个单元 | C004h |

C005h | |

C006h | |

C007h |

DPR1_L 例如表示SET0 段 数据保护区间1范围的上限64位 (可以分为16个保护区间) 占用4个单元 | C008H |

C009H | |

C00AH | |

C00BH | |

DPR1_U 例如表示SET0 段 数据保护区间1范围的下限64位 (可以分为16个保护区间) 占用4个单元 | C00Ch |

C00Dh | |

C00Eh | |

C00Fh |

浙公网安备 33010602011771号

浙公网安备 33010602011771号