日常学习(1)

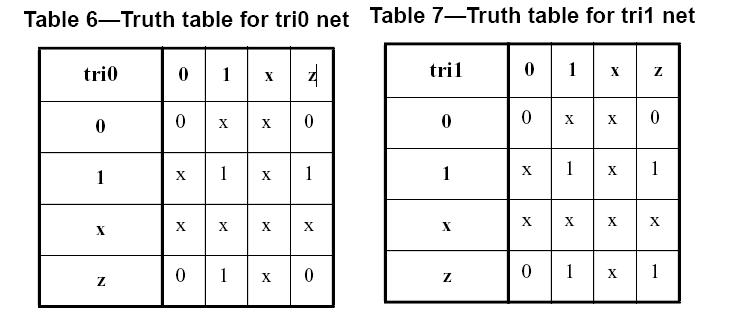

tri类型

有多个驱动源。tri0(tri1)线网的特征是,若无驱动源驱动,它的值为0(tri1的值为1)。

A tri0 net is equivalent to a wire net with a continuous 0 value of pull strength driving it.

A tri1 net is equivalent to a wire net with a continuous 1 value of pull strength driving it.

https://www.cnblogs.com/qiyuexin/p/6385846.html

信号强度

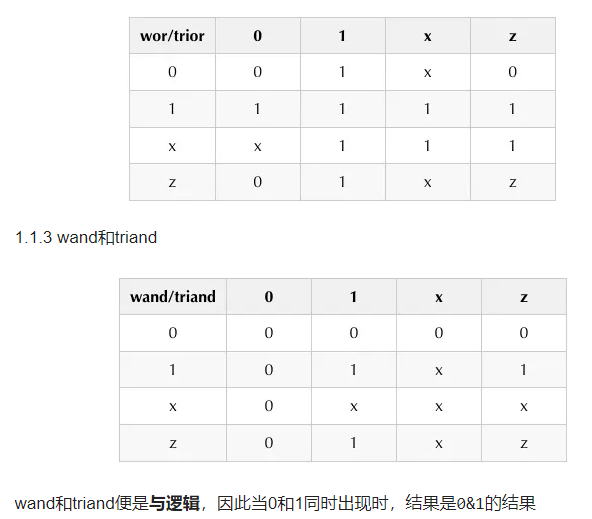

wor trior wand triand

wire or, tri or, wire and, tri and.

https://www.bilibili.com/read/cv14865354

trireg

https://www.bilibili.com/read/cv14865354

trireg线网型可以存储数值,类似于寄存器数据类型,用于电容节点的建模。

缓冲器、门

buf和not门可以具有多个输出端口,但只能具有一个输入端口,这个输入端口必须是实例端口列表的最后一个。

buf b1(OUT1,IN);

not n1(OUT1,IN);

buf b1_2out(OUT1,OUT2,IN);

not (OUT1,IN);

带控制端的缓冲器/非门(bufif/notif)

bufif1 bufif0 notif1 notif0

bufif1 b0(out,in,ctrl);

这四类门只有在控制信号有效的情况下才能传递数据;如果控制信号无效,则输出为高阻抗Z。

在控制信号有效的情况下,这些门才能传递信号。在某些情况下,例如当一个信号由多个驱动源驱动时,这样设计驱动源:

让它们的控制信号的有效时间相互错开,从而避免一条信号线同时被两个源驱动,这时就需要用带控制端的缓冲器/非门来搭建电路。

defparam

可以使用参数的分层名称在整个设计过程中的任何模块实例中更改参数值。

module top;

reg clk;

reg [0:4] in1;

reg [0:9] in2;

wire [0:4] o1;

wire [0:9] o2;

vdff m1 (o1, in1, clk);

vdff m2 (o2, in2, clk);

initial begin

$display("size:%0d, delay:%0d", m1.size, m1.delay);

$display("size:%0d, delay:%0d", m2.size, m2.delay);

end

endmodule

module vdff (out, in, clk);

parameter size = 1, delay = 1;

input [0:size-1] in;

input clk;

output [0:size-1] out;

reg [0:size-1] out;

always @(posedge clk)

# delay out = in;

endmodule

module annotate;

defparam

top.m1.size = 5,

top.m1.delay = 10,

top.m2.size = 10,

top.m2.delay = 20;

endmodule

输出:

size:5, delay:10

size:10, delay:20

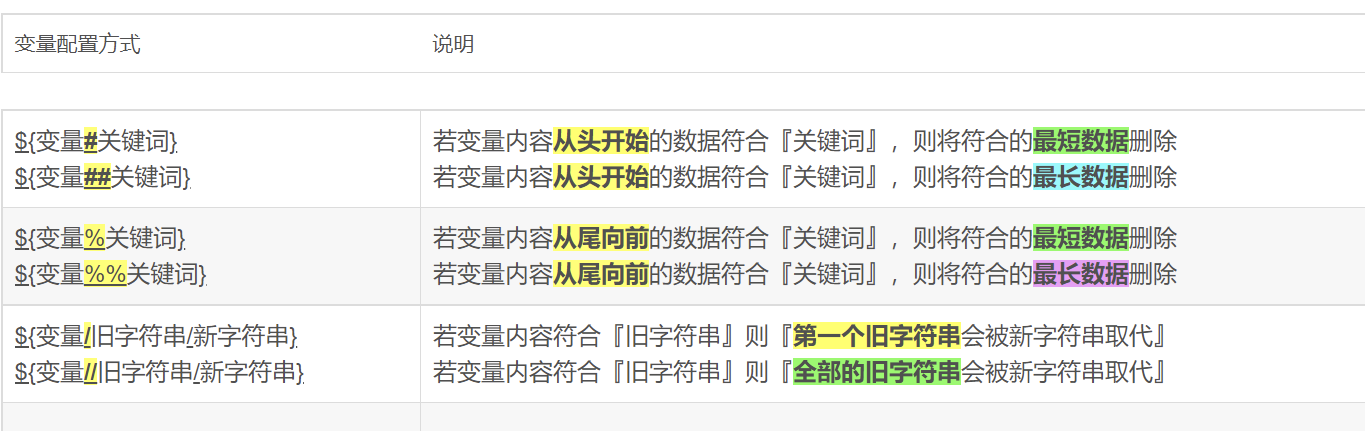

删除与替代

https://blog.csdn.net/xp18717351417/article/details/8460424

里面可用通配符的

字符串的截取

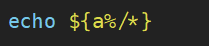

截取到变量a的路径位置的上一层

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号