日常记录(82)测试整理

默认声明

以下的taa中,b被默认声明为wire类型,a被默认声明为wire类型。(verilog语法)

c如果是input类型:Implicit wire 'b' does not have any driver

module taa ();

taax taax_inst(.c(b));

assign a=b;

endmodule

module taax (c);

output c;

// input c; // there is a warning.

endmodule

taa:

vcs -full64 -sverilog -R taa.sv

taa1:

vcs -full64 -R taa.sv

bins重复统计

以下的a1和a2,都统计了同一个数字1。100%的覆盖率。

module taa ();

bit [3:0] a;

covergroup test1;

coverpoint a{

bins a1 = {4'h1};

bins a2 = {4'h1};

}

endgroup: test1

initial begin

test1 tt=new();

a=1;

tt.sample();

$display("test");

end

endmodule

Makefile

taa:

vcs -full64 -sverilog -R taa.sv

dve:

dve -cov -dir simv.vdb

package的import

Makefile

tbb:

vcs -full64 -sverilog -R tbb_pkg.sv

- tbb_pkg的A和tcc_pkg的A不一样,无法赋值。

- tee_pkg的A和tdd_pkg的A一样,可以赋值。

- tee_pkg的A和tdd_pkg的A中,静态变量共享。

tbb_pkg.sv

package tbb_pkg;

`include "taa.svh";

endpackage: tbb_pkg

package tcc_pkg;

`include "taa.svh";

endpackage: tcc_pkg

package tdd_pkg;

//import, should be a package, should have :: operator

import tbb_pkg::A;

//The symbol 'A' is visible in this package, but need be export if used for outside.

export tbb_pkg::A;

endpackage: tdd_pkg

package tee_pkg;

export tbb_pkg::A;

endpackage: tee_pkg

module tbb_pkg_test ();

initial begin

tbb_pkg::A a_b = new();

tcc_pkg::A a_c = new();

tdd_pkg::A a_d = new();

tee_pkg::A a_e = new();

/* a_c = a_b; */ //error

// a_e = a_d; // pass

a_d.i = 1;

a_d.s_i = 2;

$display(a_e.i);

$display(a_e.s_i);

$display("test_ok");

end

endmodule

taa.svh

class A;

int i;

static int s_i;

function new();

endfunction: new

endclass: A

输出结果:

0

2

test_ok

是从program启动还是module启动testbench

结论:

- uvm不影响timeslot的采样。影响采样的是program和module

- 根据具体情况选用program或者module。后者可能更简洁?(一般是在nba区域对非阻塞赋值,此时刻不用立刻采样值,则用2好些)

- 针对一个从0到1的时隙瞬间:有clocking(默认值,input#1,output#0),使用program,得到0

- 针对一个从0到1的时隙瞬间:无clocking,使用module,得到0

- 针对一个从0到1的时隙瞬间:无clocking,使用program,得到1

Makefile文件

点击查看代码

taa:

vcs -full64 -sverilog -R taa.sv

tbb:

vcs -full64 -sverilog -R tbb.sv

tcc:

vcs -full64 -sverilog -R tcc.sv

tdd:

vcs -full64 -sverilog -R -ntb_opts uvm-1.2 tdd.sv

tee:

vcs -full64 -sverilog -R -ntb_opts uvm-1.2 tee.sv

tff:

vcs -full64 -sverilog -R -ntb_opts uvm-1.2 tff.sv

taa文件

查明。默认的timescale竟然是秒

bit [3:0] cnt;

always @(posedge clk) begin

cnt <= cnt + 1;

$display("@%0t DUT cnt = %0d",$time, cnt);

end

endmodule

module tb1;

bit clk;

bit [3:0] cnt;

initial begin

forever #5 clk <= !clk;

end

counter dut(clk);

always @(posedge clk) begin

$display("@%0t TB cnt = %0d", $time, dut.cnt);

end

initial begin

$printtimescale;

#50 $finish;

end

endmodule

输出:

TimeScale of tb1 is 1 s / 1 s

@5 TB cnt = 0

@5 DUT cnt = 0

@15 TB cnt = 1

@15 DUT cnt = 1

@25 TB cnt = 2

@25 DUT cnt = 2

@35 TB cnt = 3

@35 DUT cnt = 3

@45 TB cnt = 4

@45 DUT cnt = 4

$finish called from file "taa.sv", line 22.

$finish at simulation time 50

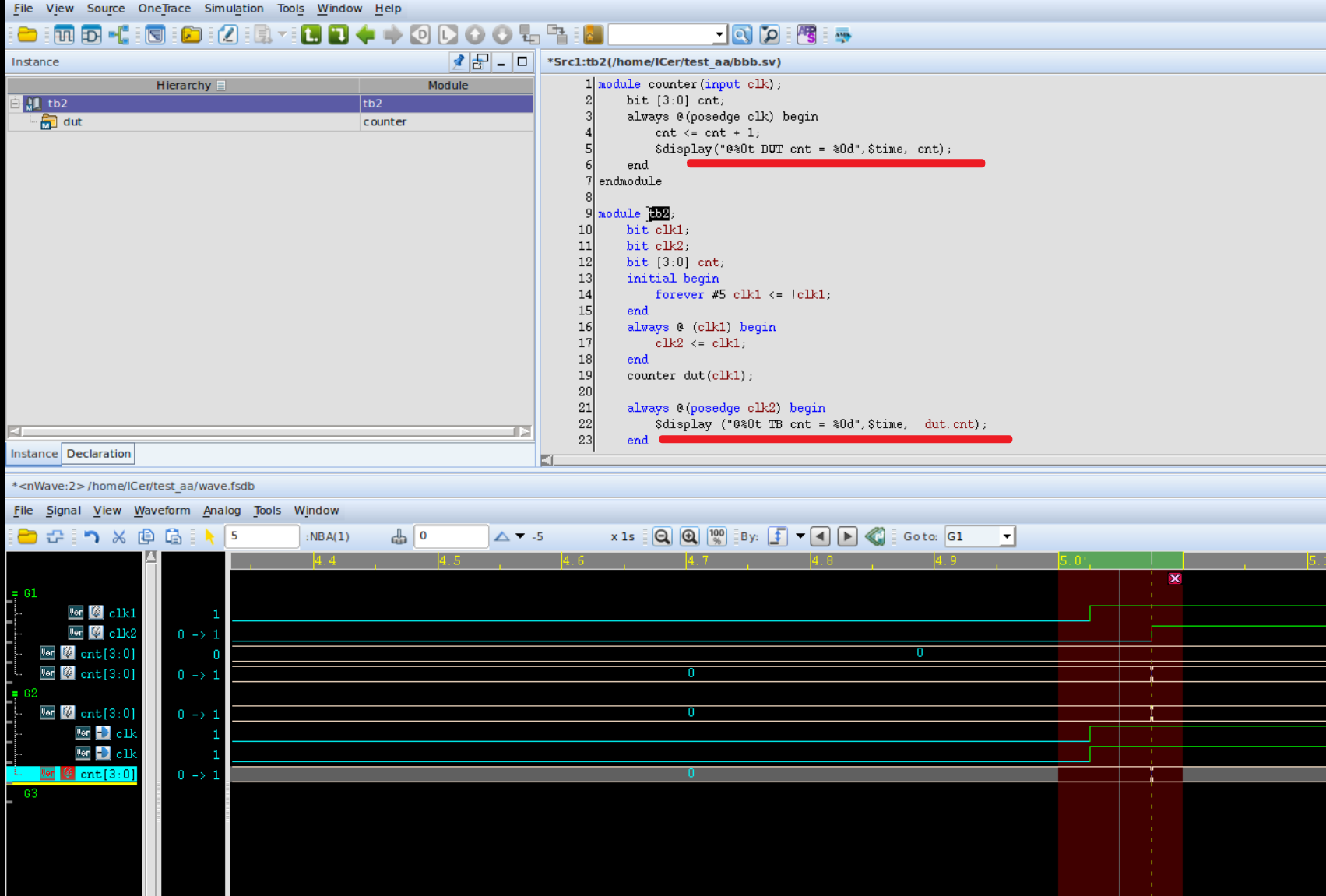

tbb文件

module counter(input clk);

bit [3:0] cnt;

always @(posedge clk) begin

cnt <= cnt + 1;

$display("@%0t DUT cnt = %0d",$time, cnt);

end

endmodule

module tb2;

bit clk1;

bit clk2;

bit [3:0] cnt;

initial begin

forever #5 clk1 <= !clk1;

end

always @ (clk1) begin

clk2 <= clk1;

end

counter dut(clk1);

always @(posedge clk2) begin

$display ("@%0t TB cnt = %0d",$time, dut.cnt);

end

initial begin

#50 $finish;

end

endmodule

输出:

@5 DUT cnt = 0

@5 TB cnt = 1

@15 DUT cnt = 1

@15 TB cnt = 2

@25 DUT cnt = 2

@25 TB cnt = 3

@35 DUT cnt = 3

@35 TB cnt = 4

@45 DUT cnt = 4

@45 TB cnt = 5

$finish called from file "tbb.sv", line 26.

$finish at simulation time 50

这个结果还是挺怪的,按道理cnt应该在clk1以后就发生变化

tcc文件

module counter(input clk);

bit [3:0] cnt;

always @(posedge clk) begin

cnt <= cnt + 1;

$display("@%0t DUT cnt = %0d",$time, cnt);

end

endmodule

program dsample(input clk);

initial begin

forever begin

@ (posedge clk);

$display("0%0t TB cnt = %0d", $time, dut.cnt);

end

end

endprogram

module tb;

bit clk1;

bit [3:0] cnt;

initial begin

forever #5 clk1 <= !clk1;

end

counter dut(clk1);

dsample spl(clk1);

initial begin

#50 $finish;

end

endmodule

输出

@5 DUT cnt = 0

05 TB cnt = 1

@15 DUT cnt = 1

015 TB cnt = 2

@25 DUT cnt = 2

025 TB cnt = 3

@35 DUT cnt = 3

035 TB cnt = 4

@45 DUT cnt = 4

045 TB cnt = 5

$finish called from file "tcc.sv", line 28.

$finish at simulation time 50

tdd文件

module counter(input clk);

bit [3:0] cnt;

always @(posedge clk) begin

cnt <= cnt + 1;

$display("@%0t DUT cnt = %0d",$time, cnt);

end

endmodule

import uvm_pkg::*;

class test_uvm extends uvm_test;

`uvm_component_utils(test_uvm)

function new(string name="test_uvm", uvm_component parent);

super.new(name, parent);

endfunction: new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

endfunction: build_phase

task run_phase(uvm_phase phase);

phase.raise_objection(this);

forever begin

@ (posedge tb.clk1);

$display("0%0t TB cnt = %0d", $time, tb.dut.cnt);

end

phase.drop_objection(this);

endtask: run_phase

endclass: test_uvm

module tb;

bit clk1;

bit [3:0] cnt;

initial begin

forever #5 clk1 <= !clk1;

end

counter dut(clk1);

initial begin

run_test("test_uvm");

end

initial begin

#50 $finish;

end

endmodule

输出:

UVM_INFO @ 0: reporter [RNTST] Running test test_uvm...

@5 DUT cnt = 0

05 TB cnt = 0

@15 DUT cnt = 1

015 TB cnt = 1

@25 DUT cnt = 2

025 TB cnt = 2

@35 DUT cnt = 3

035 TB cnt = 3

@45 DUT cnt = 4

045 TB cnt = 4

$finish called from file "tdd.sv", line 46.

$finish at simulation time 50

tee文件

module counter(input clk);

bit [3:0] cnt;

always @(posedge clk) begin

cnt <= cnt + 1;

$display("@%0t DUT cnt = %0d",$time, cnt);

end

endmodule

import uvm_pkg::*;

class test_uvm extends uvm_test;

`uvm_component_utils(test_uvm)

function new(string name="test_uvm", uvm_component parent);

super.new(name, parent);

endfunction: new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

endfunction: build_phase

task run_phase(uvm_phase phase);

phase.raise_objection(this);

forever begin

@ (posedge tb.clk1);

$display("0%0t TB cnt = %0d", $time, tb.dut.cnt);

end

phase.drop_objection(this);

endtask: run_phase

endclass: test_uvm

program test_uuu ();

initial begin

run_test("test_uvm");

end

endprogram: test_uuu

module tb;

bit clk1;

bit [3:0] cnt;

initial begin

forever #5 clk1 <= !clk1;

end

counter dut(clk1);

test_uuu uuu();

initial begin

#50 $finish;

end

endmodule

输出

UVM_INFO @ 0: reporter [RNTST] Running test test_uvm...

@5 DUT cnt = 0

05 TB cnt = 1

@15 DUT cnt = 1

015 TB cnt = 2

@25 DUT cnt = 2

025 TB cnt = 3

@35 DUT cnt = 3

035 TB cnt = 4

@45 DUT cnt = 4

045 TB cnt = 5

$finish called from file "tee.sv", line 49.

$finish at simulation time 50

tff文件

interface test_if (input bit clk);

logic [3:0] cnt;

initial begin

cnt = 0;

end

// nets

clocking test_if_cb @(posedge clk);

input cnt;

endclocking: test_if_cb

endinterface: test_if

module counter(test_if if_inst);

always @(posedge if_inst.clk) begin

if_inst.cnt <= if_inst.cnt + 1;

$display("@%0t DUT cnt = %0d",$time, if_inst.cnt);

end

endmodule

import uvm_pkg::*;

class test_uvm extends uvm_test;

`uvm_component_utils(test_uvm)

function new(string name="test_uvm", uvm_component parent);

super.new(name, parent);

endfunction: new

function void build_phase(uvm_phase phase);

super.build_phase(phase);

endfunction: build_phase

task run_phase(uvm_phase phase);

phase.raise_objection(this);

forever begin

@ (tb.if_inst.test_if_cb);

$display("0%0t TB cnt = %0d", $time, tb.if_inst.test_if_cb.cnt);

end

phase.drop_objection(this);

endtask: run_phase

endclass: test_uvm

program test_uuu ();

initial begin

run_test("test_uvm");

end

endprogram: test_uuu

module tb;

bit clk1;

test_if if_inst(clk1);

initial begin

forever #5 clk1 <= !clk1;

end

counter dut(if_inst);

test_uuu uuu();

initial begin

#50 $finish;

end

endmodule

输出:

UVM_INFO @ 0: reporter [RNTST] Running test test_uvm...

@5 DUT cnt = 0

05 TB cnt = 0

@15 DUT cnt = 1

015 TB cnt = 1

@25 DUT cnt = 2

025 TB cnt = 2

@35 DUT cnt = 3

035 TB cnt = 3

@45 DUT cnt = 4

045 TB cnt = 4

$finish called from file "tff.sv", line 62.

$finish at simulation time 50

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号