日常记录(65)通识

IC产业用语

https://zhuanlan.zhihu.com/p/403874080

IDM

Integrated Device Manufacture

集芯片设计、芯片制造、芯片封装和测试等多个产业链环节于一身

Fabless

无工厂模式,就是只做芯片设计和销售,其它环节全都使用外部资源

Foundry

代工厂模式,就是不负责芯片设计,只进行芯片生产的模式

亚稳态与处理

亚稳态产生的原因在于建立和保持时间的窗口内的信号,被时钟边沿采样。器件本身都有该窗口。窗口小则亚稳态更不容易影响电路工作。

又或者是电信号的动力不足,采样得到的结果又受到影响。

亚稳态的处理一般是通过同步器的设计实现,如两级的D触发器。多级的同步器虽然可以再次降低亚稳态出现的概率,但是系统性能也随之下降。

关于性能的下降,可以使用倍频的方式控制多级的触发器,使得结果在更短周期内获取。

https://blog.csdn.net/tristan_tian/article/details/105301175

简单总线协议

IIC

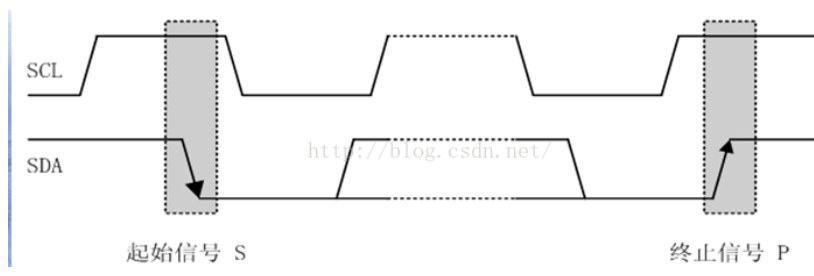

起始信号和终止信号

https://blog.csdn.net/zhanghuaichao/article/details/48266309

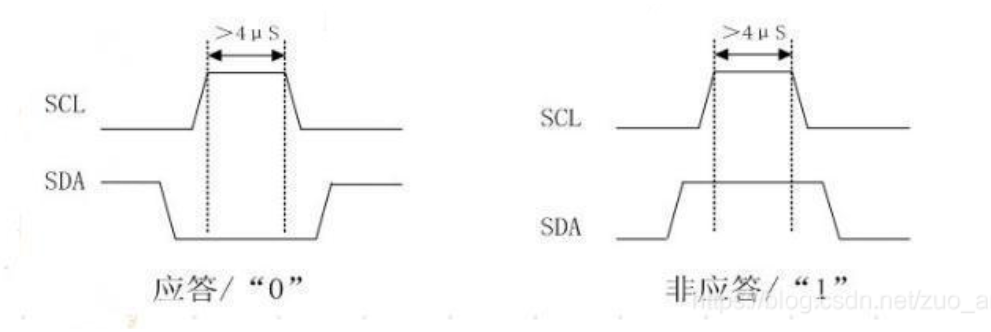

从机应答信号与01

https://blog.csdn.net/zuo_an/article/details/89139445

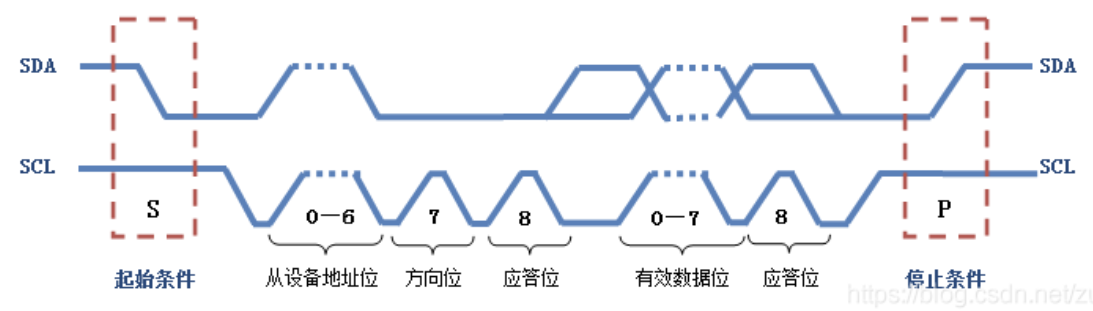

发送过程

先发地址7位,读写方向位,够8个就等应答,然后对对应的从机进行操作。

SPI

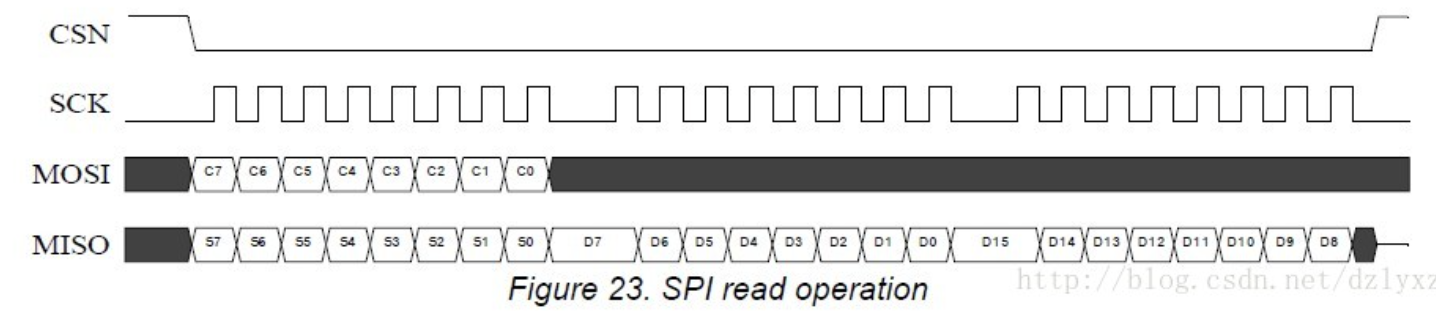

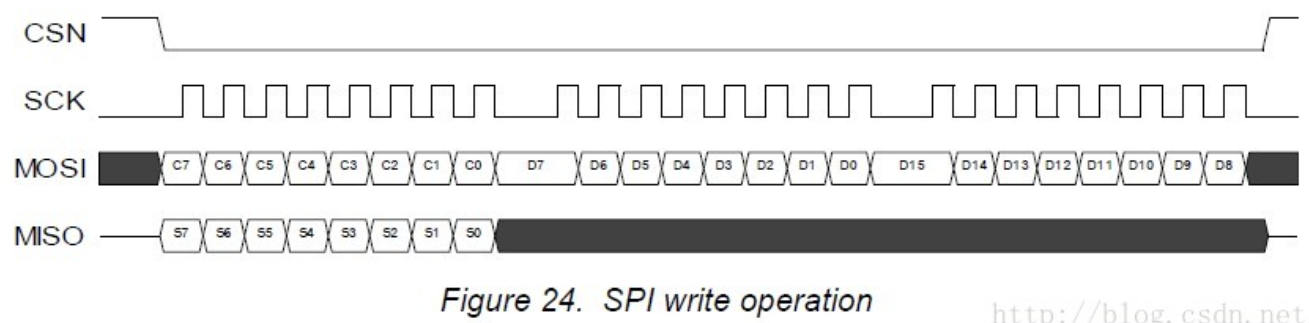

读写

有专门的片选信号。而读写没有标记位,全双工形式下,传递地址,就是在下一个周期完成又读又写的操作。

读操作

写操作

单总线

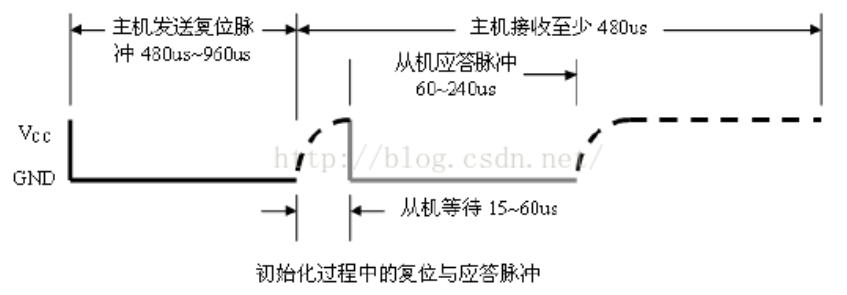

复位

主机拉低,然后释放,等从机拉低,然后主机检查是否拉低。

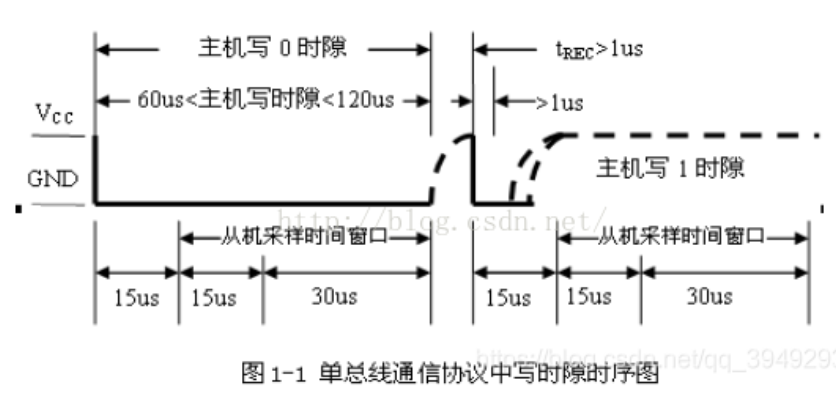

写操作

主机拉低,然后进行写0或者写1,然后拉高

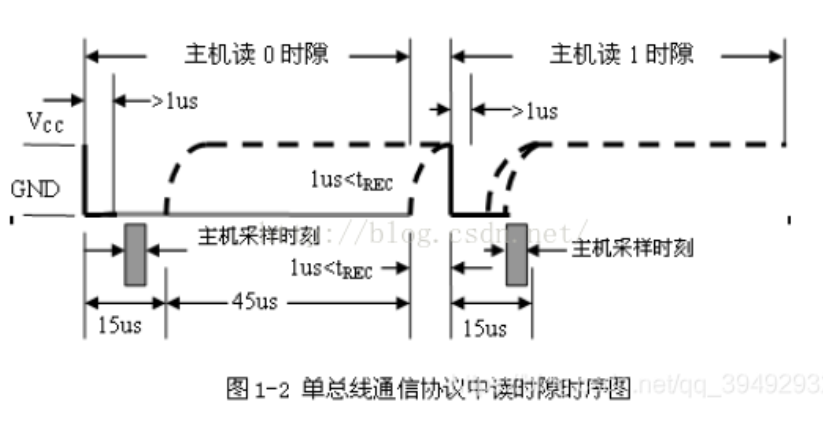

读操作

主机拉低,释放,然后采样读写

同步FIFO

端口

| 端口 | 长度 | 方向 | 功能 |

|---|---|---|---|

| data_in | 8 | input | 数据输入 |

| rd | 1 | input | 读 |

| wr | 1 | input | 写 |

| rst_n | 1 | input | 复位 |

| clk | 1 | input | 时钟 |

| data_out | 8 | output | 数据输出 |

| full | 1 | output | 满状态 |

| empty | 1 | output | 空状态 |

程序

分为6个部分,分别是:

数据写入、读取

写指针、读指针

满状态、空状态

设计了5个always结构,和1一个assign语句。

注意边界情况、状态改变情况等。

module my_sync_fifo (data_out, full, empty, data_in, rd, wr, rst_n, clk);

output wire [7:0] data_out;

output wire full, empty;

input wire [7:0] data_in;

input wire rd, wr, rst_n, clk;

reg [7:0] mem[0:15];

reg full_in, empty_in;

reg [3:0] wp, rp;

//read data

assign data_out = mem[rp];

//empty and full

assign empty = empty_in;

assign full = full_in;

//write data

always @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

;

end else if (wr && ~full_in) begin

mem[wp] <= data_in;

end

end

//change wp

always @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

wp <= 0;

end else if (wr && ~full) begin

wp <= wp + 1;

end

end

//change rp

always @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

rp <= 0;

end else if (rd && ~empty) begin

rp <= rp + 1;

end

end

//change empty

always @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

empty_in <= 1;

end else if ((rd && ~wr) && (rp == wp -1 || (rp==4'hf && wp ==0))) begin

empty_in <= 1;

end else if (empty_in && wr) begin

empty_in <= 0;

end

end

//change full

always @(posedge clk, negedge rst_n) begin

if (!rst_n) begin

full_in <= 0;

end else if ((wr && ~rd) && (wp == rp - 1 || (wp==4'hf && rp ==0))) begin

full_in <= 1;

end else if (full_in && rd) begin

full_in <= 0;

end

end

endmodule

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号