日常记录(27)功能覆盖率、duanyan

demo

-cm line+cond+fsm+tgl+branch

program automatic test ();

class Transaction;

// data or class properties

rand bit [3:0] data;

rand bit [4:0] addr;

endclass : Transaction

Transaction tr=new;

covergroup CovData;

coverpoint tr.data;

endgroup

initial begin

CovData cd=new;

repeat(32) begin

tr.data=$random;

cd.sample();

end

$display("finished!");

end

endprogram : test

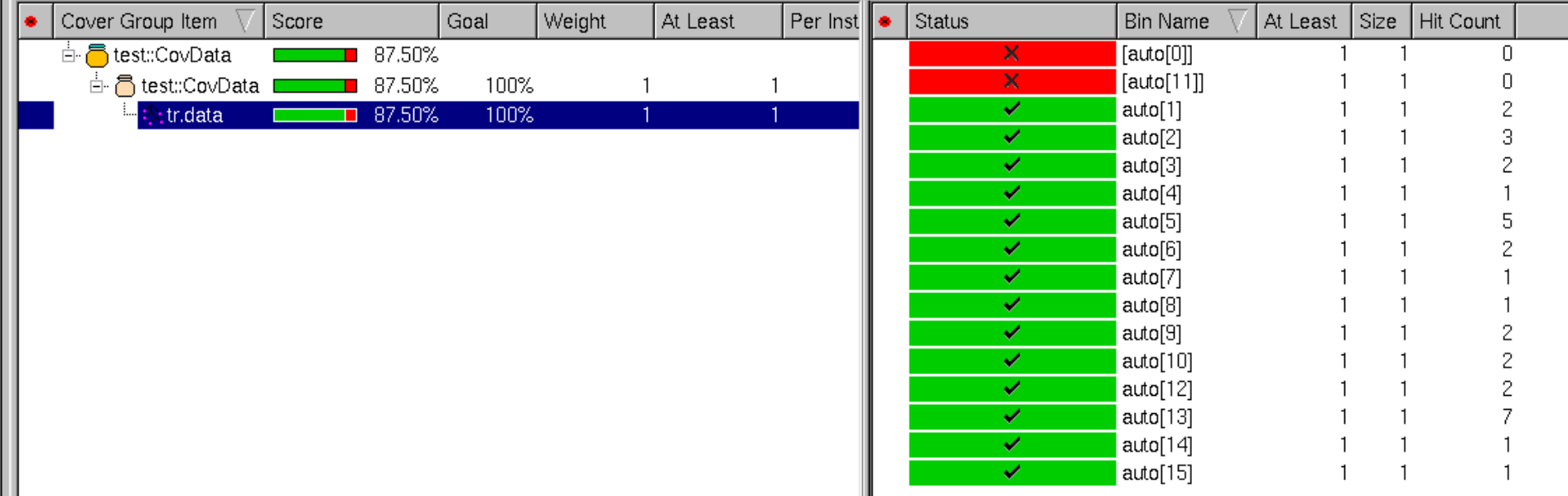

命令与输出

dve -cov -dir simv.vdb/

生成覆盖率的html

urg -dir simv.vdb/ -report report_dir

查看生成目录 的dashboard后的groups下的详细信息

功能覆盖率

program tbb ();

class Transactioin;

// data or class properties

bit [3:0] data;

bit [2:0] addr;

endclass : Transactioin

Transactioin t1;

event ct_e;

covergroup CovTest(Transactioin t2) @(ct_e);

//option.auto_bin_max=16; //default value is 64

cdata16: coverpoint (t1.data+t1.addr);

cdata32: coverpoint (t1.data+t1.addr+5'b0);

cdafault: coverpoint (t1.data+8'b0) {option.auto_bin_max=256;}

custom: coverpoint t1.data {bins zero={0}; bins one2four={[1:4]};

bins arr[5]={[7:$]}; bins misc=default;}

judge: coverpoint t1.data iff(t1.data<5);

process: coverpoint t1.data {bins t1=(1=>2),(1=>3),(1=>4);

bins t2=(1,2=>3,4);}

c1:coverpoint t1.addr {wildcard bins odd={5'b????1}; wildcard bins even={4'b???0};}

c2:cross t1.addr, t1.data;

c3: coverpoint(t2.data);

endgroup

initial begin

Transactioin t2=new;

CovTest ct=new(t2);

int cnt=0;

int cnt2=0;

t1=new;

repeat (1000) begin

t1.data=$random;

t1.addr=$random;

if (t1.data<1) begin

cnt++;

if (cnt>10) begin

ct.stop;

//ct.start;

break;

end

end

->ct_e;

cnt2++;

end

$display("finished, total cnt is %d", cnt2);

end

endprogram : tbb

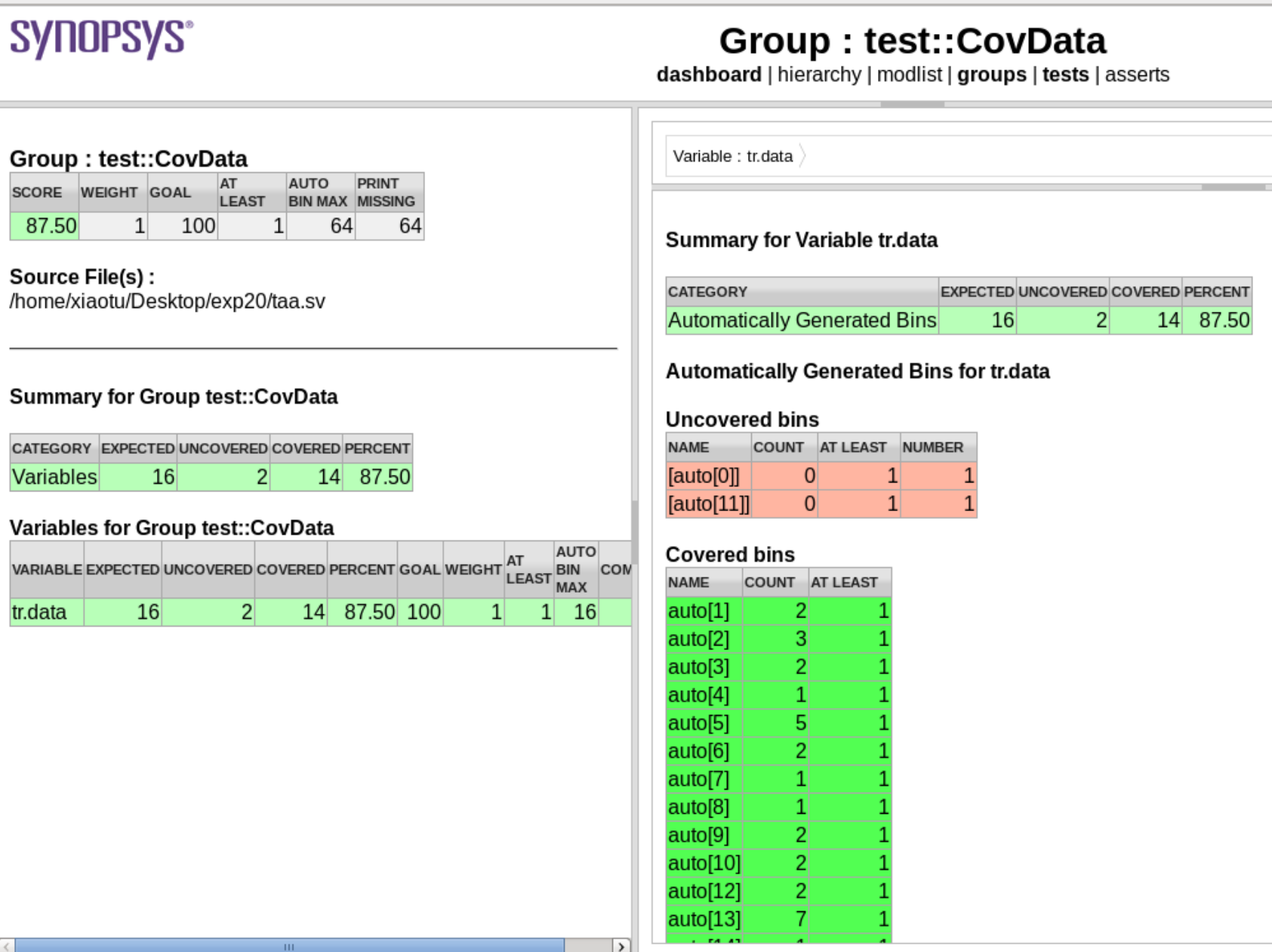

输出与网页

finished, total cnt is 286

1 Group : tbb::CovTest 2 dashboard | hierarchy | modlist | groups | tests | asserts 3 4 Group : tbb::CovTest 5 SCORE WEIGHT GOAL AT LEAST AUTO BIN MAX PRINT MISSING 6 73.22 1 100 1 64 64 7 8 9 Source File(s) : 10 /home/xiaotu/Desktop/exp20/tbb.sv 11 12 13 Summary for Group tbb::CovTest 14 15 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 16 Variables 371 275 96 71.56 17 Crosses 128 13 115 89.84 18 19 20 Variables for Group tbb::CovTest 21 VARIABLE EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT AT LEAST AUTO BIN MAX COMMENT 22 cdata16 16 0 16 100.00 100 1 1 16 23 cdata32 32 9 23 71.88 100 1 1 32 24 cdafault 256 240 16 6.25 100 1 1 256 25 custom 7 0 7 100.00 100 1 1 0 26 judge 16 11 5 31.25 100 1 1 16 27 process 2 0 2 100.00 100 1 1 0 28 c1 2 0 2 100.00 100 1 1 0 29 t1.addr 8 0 8 100.00 100 1 1 8 30 t1.data 16 0 16 100.00 100 1 1 16 31 c3 16 15 1 6.25 100 1 1 16 32 33 34 Crosses for Group tbb::CovTest 35 CROSS EXPECTED UNCOVERED COVERED PERCENT GOAL WEIGHT AT LEAST PRINT MISSING COMMENT 36 c2 128 13 115 89.84 100 1 1 0 37 38 39 Summary for Variable cdata16 40 41 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 42 Automatically Generated Bins 16 0 16 100.00 43 44 45 Automatically Generated Bins for cdata16 46 47 Bins 48 NAME COUNT AT LEAST 49 auto[0] 20 1 50 auto[1] 16 1 51 auto[2] 19 1 52 auto[3] 12 1 53 auto[4] 12 1 54 auto[5] 20 1 55 auto[6] 25 1 56 auto[7] 15 1 57 auto[8] 17 1 58 auto[9] 15 1 59 auto[10] 12 1 60 auto[11] 17 1 61 auto[12] 24 1 62 auto[13] 20 1 63 auto[14] 24 1 64 auto[15] 18 1 65 66 67 Summary for Variable cdata32 68 69 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 70 Automatically Generated Bins 32 9 23 71.88 71 72 73 Automatically Generated Bins for cdata32 74 75 Uncovered bins 76 NAME COUNT AT LEAST NUMBER 77 [auto[23] - auto[31]] -- -- 9 78 79 80 Covered bins 81 NAME COUNT AT LEAST 82 auto[0] 2 1 83 auto[1] 4 1 84 auto[2] 7 1 85 auto[3] 4 1 86 auto[4] 9 1 87 auto[5] 18 1 88 auto[6] 24 1 89 auto[7] 15 1 90 auto[8] 17 1 91 auto[9] 15 1 92 auto[10] 12 1 93 auto[11] 17 1 94 auto[12] 24 1 95 auto[13] 20 1 96 auto[14] 24 1 97 auto[15] 18 1 98 auto[16] 18 1 99 auto[17] 12 1 100 auto[18] 12 1 101 auto[19] 8 1 102 auto[20] 3 1 103 auto[21] 2 1 104 auto[22] 1 1 105 106 107 Summary for Variable cdafault 108 109 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 110 Automatically Generated Bins 256 240 16 6.25 111 112 113 Automatically Generated Bins for cdafault 114 115 Uncovered bins 116 NAME COUNT AT LEAST NUMBER 117 [auto[16] - auto[255]] -- -- 240 118 119 120 Covered bins 121 NAME COUNT AT LEAST 122 auto[0] 10 1 123 auto[1] 13 1 124 auto[2] 23 1 125 auto[3] 10 1 126 auto[4] 19 1 127 auto[5] 19 1 128 auto[6] 27 1 129 auto[7] 16 1 130 auto[8] 17 1 131 auto[9] 24 1 132 auto[10] 19 1 133 auto[11] 26 1 134 auto[12] 17 1 135 auto[13] 18 1 136 auto[14] 13 1 137 auto[15] 15 1 138 139 140 Summary for Variable custom 141 142 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 143 User Defined Bins 7 0 7 100.00 144 145 146 User Defined Bins for custom 147 148 Excluded/Illegal bins 149 NAME COUNT STATUS 150 misc 46 Excluded 151 152 153 Covered bins 154 NAME COUNT AT LEAST 155 arr[7] 16 1 156 arr[8] 17 1 157 arr[9] 24 1 158 arr[a] 19 1 159 arr[b:f] 89 1 160 one2four 65 1 161 zero 10 1 162 163 164 Summary for Variable judge 165 166 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 167 Automatically Generated Bins 16 11 5 31.25 168 169 170 Automatically Generated Bins for judge 171 172 Uncovered bins 173 NAME COUNT AT LEAST NUMBER 174 [auto[5] - auto[15]] -- -- 11 175 176 177 Covered bins 178 NAME COUNT AT LEAST 179 auto[0] 10 1 180 auto[1] 13 1 181 auto[2] 23 1 182 auto[3] 10 1 183 auto[4] 19 1 184 185 186 Summary for Variable process 187 188 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 189 User Defined Bins 2 0 2 100.00 190 191 192 User Defined Bins for process 193 194 Bins 195 NAME COUNT AT LEAST 196 t2 2 1 197 t1 1 1 198 199 200 Summary for Variable c1 201 202 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 203 User Defined Bins 2 0 2 100.00 204 205 206 User Defined Bins for c1 207 208 Bins 209 NAME COUNT AT LEAST 210 even 134 1 211 odd 152 1 212 213 214 Summary for Variable t1.addr 215 216 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 217 Automatically Generated Bins 8 0 8 100.00 218 219 220 Automatically Generated Bins for t1.addr 221 222 Bins 223 NAME COUNT AT LEAST 224 auto[0] 43 1 225 auto[1] 49 1 226 auto[2] 34 1 227 auto[3] 31 1 228 auto[4] 27 1 229 auto[5] 44 1 230 auto[6] 30 1 231 auto[7] 28 1 232 233 234 Summary for Variable t1.data 235 236 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 237 Automatically Generated Bins 16 0 16 100.00 238 239 240 Automatically Generated Bins for t1.data 241 242 Bins 243 NAME COUNT AT LEAST 244 auto[0] 10 1 245 auto[1] 13 1 246 auto[2] 23 1 247 auto[3] 10 1 248 auto[4] 19 1 249 auto[5] 19 1 250 auto[6] 27 1 251 auto[7] 16 1 252 auto[8] 17 1 253 auto[9] 24 1 254 auto[10] 19 1 255 auto[11] 26 1 256 auto[12] 17 1 257 auto[13] 18 1 258 auto[14] 13 1 259 auto[15] 15 1 260 261 262 Summary for Variable c3 263 264 CATEGORY EXPECTED UNCOVERED COVERED PERCENT 265 Automatically Generated Bins 16 15 1 6.25 266 267 268 Automatically Generated Bins for c3 269 270 Uncovered bins 271 NAME COUNT AT LEAST NUMBER 272 [auto[1] - auto[15]] -- -- 15 273 274 275 Covered bins 276 NAME COUNT AT LEAST 277 auto[0] 286 1 278 279 280 Summary for Cross c2 281 282 Samples crossed: t1.addr t1.data 283 CATEGORY EXPECTED UNCOVERED COVERED PERCENT MISSING 284 Automatically Generated Cross Bins 128 13 115 89.84 13 285 286 287 Automatically Generated Cross Bins for c2 288 289 Uncovered bins 290 t1.addr t1.data COUNT AT LEAST NUMBER 291 [auto[0]] [auto[7]] 0 1 1 292 [auto[2]] [auto[8] - auto[9]] -- -- 2 293 [auto[3]] [auto[2]] 0 1 1 294 [auto[3]] [auto[5]] 0 1 1 295 [auto[4]] [auto[1]] 0 1 1 296 [auto[4]] [auto[5]] 0 1 1 297 [auto[5]] [auto[3]] 0 1 1 298 [auto[5]] [auto[15]] 0 1 1 299 [auto[6]] [auto[3]] 0 1 1 300 [auto[7]] [auto[3]] 0 1 1 301 [auto[7]] [auto[7]] 0 1 1 302 [auto[7]] [auto[10]] 0 1 1 303 304 305 Covered bins 306 t1.addr t1.data COUNT AT LEAST 307 auto[0] auto[15] 1 1 308 auto[0] auto[10] 1 1 309 auto[0] auto[0] 2 1 310 auto[0] auto[5] 6 1 311 auto[0] auto[3] 1 1 312 auto[0] auto[12] 3 1 313 auto[0] auto[9] 6 1 314 auto[0] auto[6] 7 1 315 auto[0] auto[13] 1 1 316 auto[0] auto[8] 1 1 317 auto[0] auto[2] 4 1 318 auto[0] auto[11] 2 1 319 auto[0] auto[1] 3 1 320 auto[0] auto[4] 2 1 321 auto[0] auto[14] 3 1 322 auto[7] auto[0] 1 1 323 auto[7] auto[5] 4 1 324 auto[7] auto[15] 1 1 325 auto[7] auto[6] 2 1 326 auto[7] auto[12] 1 1 327 auto[7] auto[9] 4 1 328 auto[7] auto[2] 1 1 329 auto[7] auto[13] 2 1 330 auto[7] auto[8] 3 1 331 auto[7] auto[1] 2 1 332 auto[7] auto[14] 1 1 333 auto[7] auto[11] 3 1 334 auto[7] auto[4] 3 1 335 auto[2] auto[10] 2 1 336 auto[2] auto[5] 3 1 337 auto[2] auto[15] 2 1 338 auto[2] auto[0] 2 1 339 auto[2] auto[3] 4 1 340 auto[2] auto[12] 3 1 341 auto[2] auto[6] 3 1 342 auto[2] auto[13] 2 1 343 auto[2] auto[7] 3 1 344 auto[2] auto[2] 3 1 345 auto[2] auto[1] 1 1 346 auto[2] auto[4] 2 1 347 auto[2] auto[14] 1 1 348 auto[2] auto[11] 3 1 349 auto[5] auto[0] 1 1 350 auto[5] auto[5] 2 1 351 auto[5] auto[10] 6 1 352 auto[5] auto[9] 4 1 353 auto[5] auto[6] 4 1 354 auto[5] auto[12] 2 1 355 auto[5] auto[2] 4 1 356 auto[5] auto[7] 2 1 357 auto[5] auto[13] 3 1 358 auto[5] auto[8] 5 1 359 auto[5] auto[4] 2 1 360 auto[5] auto[1] 2 1 361 auto[5] auto[11] 4 1 362 auto[5] auto[14] 3 1 363 auto[6] auto[5] 1 1 364 auto[6] auto[0] 1 1 365 auto[6] auto[15] 1 1 366 auto[6] auto[10] 1 1 367 auto[6] auto[9] 2 1 368 auto[6] auto[6] 3 1 369 auto[6] auto[12] 2 1 370 auto[6] auto[13] 1 1 371 auto[6] auto[2] 4 1 372 auto[6] auto[8] 4 1 373 auto[6] auto[7] 2 1 374 auto[6] auto[4] 1 1 375 auto[6] auto[1] 2 1 376 auto[6] auto[14] 1 1 377 auto[6] auto[11] 4 1 378 auto[4] auto[0] 1 1 379 auto[4] auto[10] 3 1 380 auto[4] auto[15] 3 1 381 auto[4] auto[12] 1 1 382 auto[4] auto[3] 1 1 383 auto[4] auto[6] 3 1 384 auto[4] auto[9] 2 1 385 auto[4] auto[7] 1 1 386 auto[4] auto[13] 2 1 387 auto[4] auto[2] 6 1 388 auto[4] auto[8] 1 1 389 auto[4] auto[11] 1 1 390 auto[4] auto[4] 1 1 391 auto[4] auto[14] 1 1 392 auto[3] auto[0] 1 1 393 auto[3] auto[10] 2 1 394 auto[3] auto[15] 3 1 395 auto[3] auto[12] 2 1 396 auto[3] auto[9] 3 1 397 auto[3] auto[6] 2 1 398 auto[3] auto[3] 3 1 399 auto[3] auto[8] 2 1 400 auto[3] auto[13] 3 1 401 auto[3] auto[7] 2 1 402 auto[3] auto[1] 2 1 403 auto[3] auto[11] 3 1 404 auto[3] auto[4] 1 1 405 auto[3] auto[14] 2 1 406 auto[1] auto[0] 1 1 407 auto[1] auto[5] 3 1 408 auto[1] auto[15] 4 1 409 auto[1] auto[10] 4 1 410 auto[1] auto[3] 1 1 411 auto[1] auto[12] 3 1 412 auto[1] auto[6] 3 1 413 auto[1] auto[9] 3 1 414 auto[1] auto[2] 1 1 415 auto[1] auto[8] 1 1 416 auto[1] auto[7] 6 1 417 auto[1] auto[13] 4 1 418 auto[1] auto[14] 1 1 419 auto[1] auto[4] 7 1 420 auto[1] auto[11] 6 1 421 auto[1] auto[1] 1 1 422 423 Variable : cdata16 424 Variable : cdata32 425 Variable : cdafault 426 Variable : custom 427 Variable : judge 428 Variable : process 429 Variable : c1 430 Variable : t1.addr 431 Variable : t1.data 432 Variable : c3 433 Cross : c2 434 0% 10% 20% 30% 40% 50% 60% 70% 80% 90% 100%

断言资料

断言类型

assert立即断言

其中的\$fatal、\$error、\$warning、\$info,指示严重程度。如下:

time t;

always @(posedge clk)

if (state == REQ)

assert (req1 || req2)

else begin

t = $time;

#5 $error("assert failed at time %0t",t);

end

又如assert与else结合

assert (myfunc(a,b)) count1 = count + 1; else -> event1; assert (y == 0) else flag = 1;

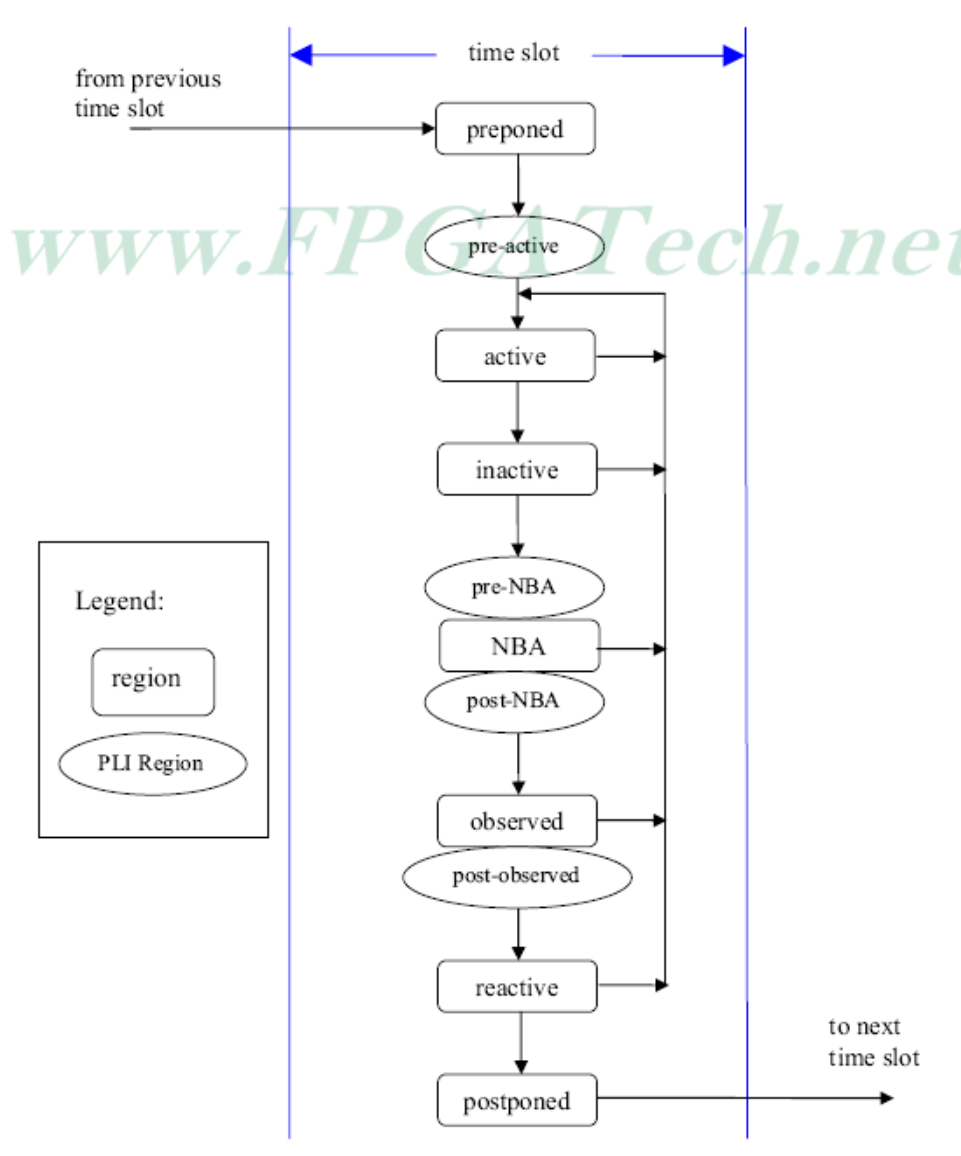

property并发断言

并发断言描述了贯穿时间的行为。与即时断言基于时钟的计算模型不同,仅在一个时钟标记出现的时候被计算。获得一个可预测的结果。

断言中使用的变量值在一个时隙的Preponed区域被采样,并且断言在Observe区域被计算。

验证设计意图,内部可包含sequence

sequence序列

将一个序列做出来,包含很多场景,比如reset等

延迟与不延迟

|=>下一周期的因果关系,

|->同下一周期的因果关系,

cover、assume、assert

断言相差一个时间单位。仿真时钟域在active后的assertion部分,随后是deactive、postpone。

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号