日常记录(4)硬件相关

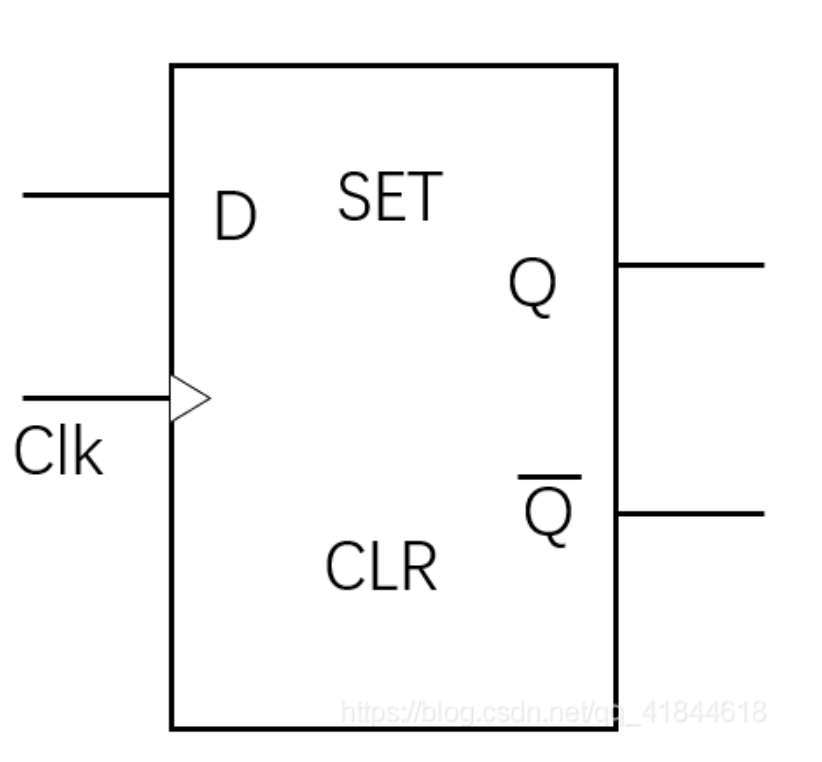

D触发器

https://blog.csdn.net/qq_41844618/article/details/104332949

在触发边沿到来时,将输入端D的值存入Q中.

在脉冲边沿到来之前,输入端D必须有足够的建立时间,保证信号稳定。

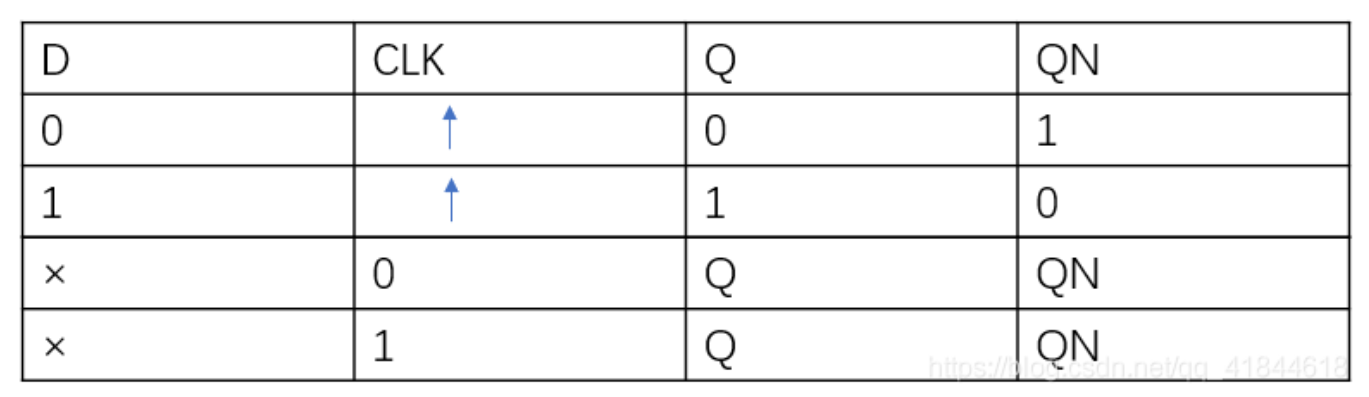

特性表,如上升沿

Verilog中“=”和“<=”的区别

http://www.51hei.com/mcu/3677.html

一般情况下使用<=,组合逻辑使用=赋值,时序逻辑使用<=赋值:

举个例子:初始化m=1,n=2,p=3;分别执行以下语句

1、begin

m=n;n=p;p=m;

end

2、begin

m<=n; n<=p; p<=m;

end

结果分别是:1、m=2,n=3,p=2;(在给p赋值时m=2已经生效)

2、m=2,n=3,p=1;(在begin-end过程中,m=2一直无效而是在整体执行完后才生效)

这两种赋值“=”用于阻塞式赋值;“<=”用于非阻塞式赋值中。

阻塞赋值:阻塞赋值语句是在这句之后所有语句执行之前执行的,即后边的语句必须在这句执行完毕才能执行,所以称为阻塞,实际上就是顺序执行。

非阻塞赋值:非阻塞赋值就是与后边相关语句同时执行,即就是并行执行。

所以一般时序电路使用非阻塞赋值,assign语句一般使用=阻塞赋值;

组合逻辑电路使用阻塞赋值;

always和initial顺序

https://blog.csdn.net/qq_29051107/article/details/119090263

结果一:1,2或者3,4对比可知在always和initial对同一个变量赋值起冲突的时候,并不是先执行initial,而是看代码书写的先后顺序。

结果二:通过1和3,我们可以知道always并不是在initial运行完之后才开始运行的,而是两个块并行执行的。

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号