【STM32H7教程】第3章 STM32H7整体把控

完整教程下载地址:http://www.armbbs.cn/forum.php?mod=viewthread&tid=86980

第3章 STM32H7整体把控

初学STM32H7一定要优先整体把控芯片的框架,不要急于了解单个外设的功能。

3.1 初学者重要提示

3.1 STM32H7框图

3.2 STM32H7各个型号的区别

3.2 STM32H7总线框图和时钟

3.3 STM32H7的AXI 总线

3.4 STM32H7的FLASH

3.5 STM32H7的RAM

3.6 总结

3.1 初学者重要提示

- 学习一款新的芯片,优先掌握系统框架是比较重要的,建议逐渐养成这种学习习惯,然后各个击破即可。

- 本章节提供了多张STM32H7的框图,这些框图都非常具有代表性。很多时候记忆知识点比较费脑子,记录这些框图是一种非常好的方式。

- 对于本章节提供的部分知识点,无法理解透彻,暂时没有关系。随着后面的深入学习,基本都可以掌握。

- 重要的MPU和Cache知识分别放在了第23章和第24章。

3.2 STM32H7硬件框图

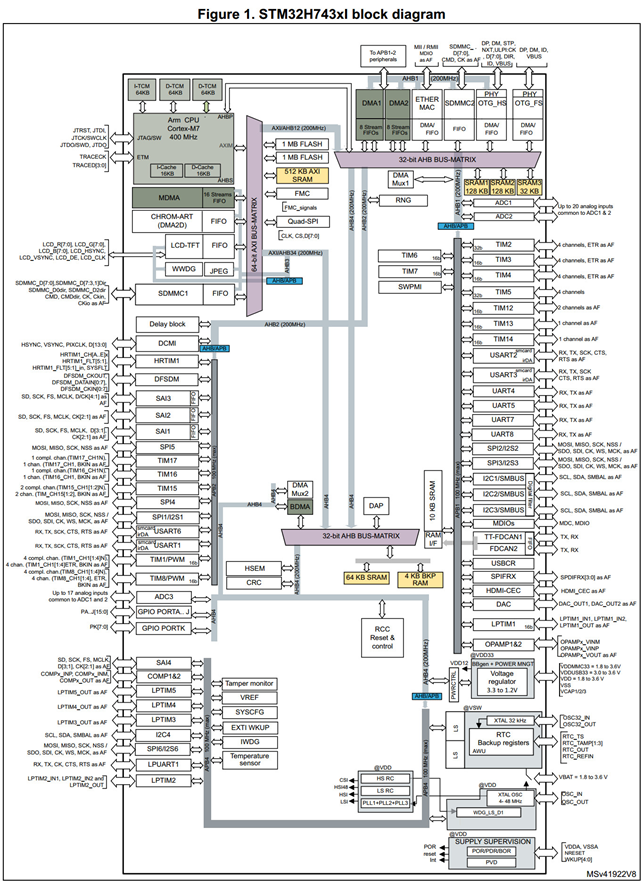

学习一款新的芯片,需要优先了解一下它的整体功能设计。需要的资料主要是来自官网和数据手册,比如我们V7开发板使用的STM32H743XIH6,直接在官方地址:链接(这是超链接)就可以看到对此芯片所做的介绍,页面中有一个如下的框图,对于了解STM32H7整体设计非常方便。

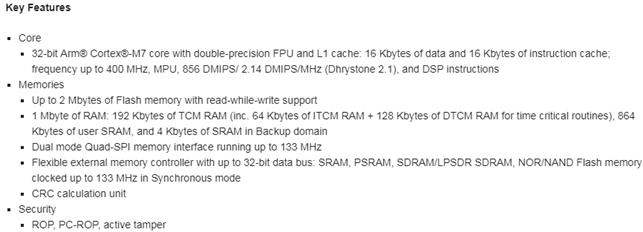

再稍微详细点,就需要大家读页面上的”Key Features”,就是下图所示的内容:

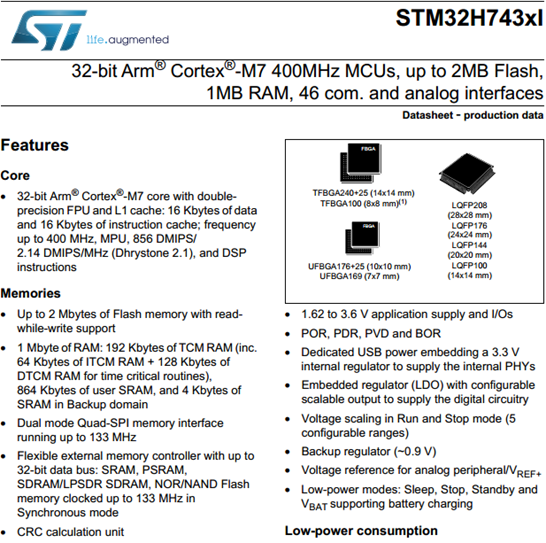

或者直接看数据手册开头的章节即可,也进行了介绍,内容基本都是差不多的,如下图所示(部分截图):

通过框图和Key Features,大家可以方便地了解STM32H7的FLASH、RAM大小以及各种自带外设的信息。

3.3 STM32H7各个型号的区别

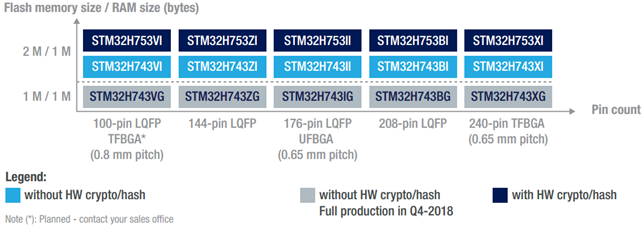

涉及到芯片选型的时候,需要大家了解各个型号的区别。对此ST有一个专门的文件STM32H7x3 MCUs High-performance line,在链接(这是一个超链接)里面可以找到。此文件里面有简单的对比,只是内容比较简单,仅两页,不过也言简意赅。最主要的是下面的这个截图:

通过这个截图可以方便地了解不同型号的引脚数、封装、FLASH大小、RAM大小以及是否带HW CRYPTO硬件加密的区别。

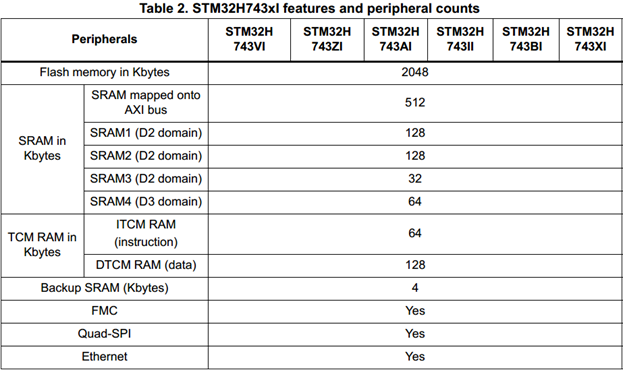

需要了解更详细的对比信息,可以看数据手册。任意下载一个型号的数据手册,在数据手册的的Table 2里面有详细的对比,如下图所示(部分截图):

使用ST提供的软件STMCUFinder或者STM32CubeMX也可以做对比,只是没有上面的表格这么方便,可以一目了然。

3.4 STM32H7总线框图和时钟

STM32H7的数据手册里面提供了一张非常棒的框图,大家可以方便地查看每个总线的时钟速度和这个总线所挂的外设。这个在大家配置外设时钟分频的时候还是非常有用的,因为外设的时钟分频就是建立在所挂的总线速度(大家直接在数据手册里面检索Figure 1就可以找到)。

比如我们想得到不同定时器的主频,通过上面的框图,可以方便地获得如下信息:

SYSCLK(Hz) = 400000000 (CPU Clock)

HCLK(Hz) = 200000000 (AXI and AHBs Clock)

AHB Prescaler = 2

D1 APB3 Prescaler = 2 (APB3 Clock 100MHz)

D2 APB1 Prescaler = 2 (APB1 Clock 100MHz)

D2 APB2 Prescaler = 2 (APB2 Clock 100MHz)

D3 APB4 Prescaler = 2 (APB4 Clock 100MHz)

因为APB1 prescaler != 1, 所以 APB1上的TIMxCLK = APB1 x 2 = 200MHz;

因为APB2 prescaler != 1, 所以 APB2上的TIMxCLK = APB2 x 2 = 200MHz;

APB4上面的TIMxCLK没有分频,所以就是100MHz;

APB1 定时器有 TIM2, TIM3 ,TIM4, TIM5, TIM6, TIM7, TIM12, TIM13, TIM14,LPTIM1

APB2 定时器有 TIM1, TIM8 , TIM15, TIM16,TIM17

APB4 定时器有 LPTIM2,LPTIM3,LPTIM4,LPTIM5

3.5 STM32H7的AXI总线

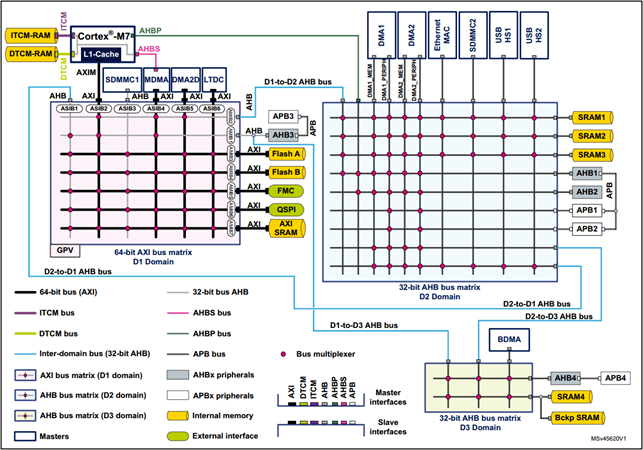

AXI总线在STM32H7中有着举足轻重的作用。高并发性全靠这个总线了,先来看下AXI总线的框架:

3.5.1 总线系统框架

下面这个截图比较有代表性,可以帮助大家理解STM32H7总线系统。

这个图可以方便识别总线所外挂的外设,共分为三个域:D1 Domain,D2 Domain和D3 Domain。

D1 Domain

D1域中的各个外设是挂在64位AXI总线组成6*7的矩阵上。

- 6个从接口端ASIB1到ASIB6

外接的主控是LTDC,DMA2D,MDMA,SDMMC1,AXIM和D2-to-D1 AHB 总线。

- 7个主接口端AMIB1到AMIB7

外接的从设备是AHB3总线,Flash A,Flash B,FMC总线,QSPI和AXI SRAM。另外AHB3也是由AXI总线分支出来的,然后再由AHB3分支出APB3总线。

D2 Domain

D2域的各个外设是挂在32位AHB总线组成10*9的矩阵上。

- 10个从接口

外接的主控是D1-to-D2 AHB 总线,AHBP总线,DMA1,DMA2,Ethernet MAC,SDMMC2,USB HS1和USB HS2。

- 9个主接口

外接的从设备是SRAM1,SRMA2,SRAM3,AHB1,AHB2,APB2,APB3,D2-to-D1 AHB总线和D2-to-D3 AHB总线。

D3 Domain

D3域的各个外设是挂在32位AHB总线组成3*2的矩阵上。

- 3个从接口

外接的主控D1-to-D3 AHB总线,D2-to-D3 AHB总线和BDMA。

- 2个主接口

外接的从设备是AHB4,SRAM4和Bckp SRAM。另外AHB4也是这个总线矩阵分支出来的,然后再由AHB4分支出APB4总线。

这三个域之间也是有互联的,可以是:

- D1域到D2域的D1-to-D2 AHB bus

允许D1域中的主接口外设访问D2域里面的从接口外设。比如D1域里面的DMA2D访问D2域里面的SRAM1。

- D2域到D1域的D2-to-D1 AHB bus

允许D2域中的主接口外设访问D1域里面的从接口外设。比如D2域里面的DMA2访问D1域里面的AXI SRAM。

- D1域到D3域的D1-to-D3 AHB bus

允许D1域中的主接口外设访问D3域里面的从接口外设。比如D1域里面的DMA2D访问D3域里面的SRAM4。

- D2域到D3域的D2-to-D3 AHB bus。

允许D1域中的主接口外设访问D2域里面的从接口外设。比如D2域里面的DMA2访问D3域里面的SRAM4。

有了这些知识后,下面我们重点了解AXI总线矩阵。

3.5.2 AXI总线特色

AXI支持高频率、高性能的系统设计:

- 支持高带宽,低延迟设计。

- 提供高频操作,无需复杂的总线桥。

- 满足各种组件的接口需求。

- 适用于具有高初始访问延迟的内存控制器。

- 为互连架构的实现提供了灵活性。

- 与现有的AHB和APB接口向后兼容。

AXI总线的关键特性:

- 独立的地址、控制和数据线。

- 支持非字节对齐方式传输。

- 基于起始地址的突发传输。

- 分开的读和写数据通道,且提供DMA传输。

- 支持发起多个地址。

- 支持无序传输。

- 允许添加寄存器,以提供时序收敛。

- AXI总线

关于AXI总线,ARM有一篇古文观止级文档《AXI4_specification》,已经将其放在了论坛:http://www.armbbs.cn/forum.php?mod=viewthread&tid=87340

3.5.3 AXI总线简介

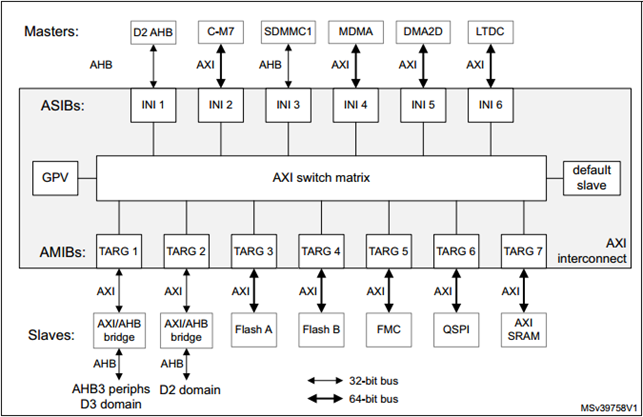

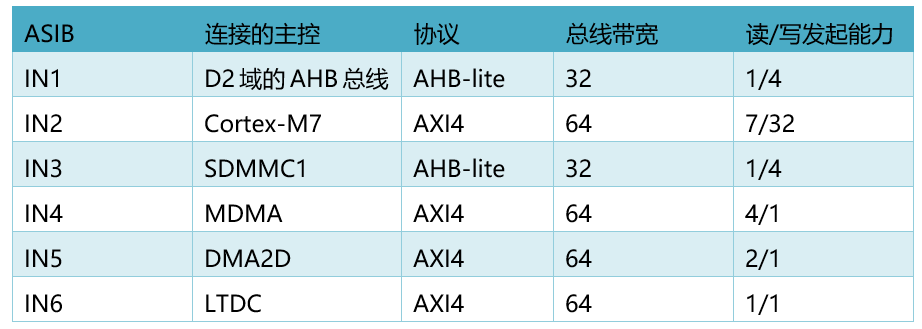

通过下面的框图,我们再进一步的认识一下AXI总线。

通过上面的截图,我们可以看到,AXI总线有6个从接口ASIBs(AMBA slave interface blocks)和7个主控接口AMIBs(AMBA master interface blocks)。

针对从接口ASIBs,描述如下:

重点注意最后一列,STM32H7参考手册里面原始的描述是R/W issuing,这里将其翻译为读/写发起能力。比如输入通道IN5连接的主控DMA2D,支持的读发起能力是2,写发起能力是1。读发起能力是2该如何理解呢?这里的含义是存在两路读信号同时进行(因为AXI接口有一个FIFO的功能,可供同时进行,更深入的认识有待研究),反映到DMA2D的实际应用中,就是DMA2D同时读取前景色和背景色的缓存区做Alpha融合之类的操作。写操作同理,DMA2D的写发起能力仅支持一路。

针对主控接口AMIBs,描述如下:

跟上面表格的含义是一样的,同样重点注意最后一列,这里多了一个总接收能力(Total acceptance),也就是读发起能力和写发起能力同时执行的情况。

3.5.4 AXI总线优先级编程

由于存在多个ASIB从接口访问AMIB主控的问题,这就涉及到谁先谁后等问题。所以AXI总线矩阵就做了一个基于优先级的仲裁方案。每个ASIB接口支持读通道和写通道分别设置,优先级从0到15。数值越大,优先级越高,默认情况都是优先级0。如果有两个传输同时到达AMIB主控接口,那么优先级高的ASIB接口传输优先处理;如果优先级相同的话,根据LUR方案选择(least recently-used最近最少使用情况)。

大家在实际应用中,可以根据实际情况进行设置,一般情况下使用默认值即可。

3.6 STM32H7的总线互联

STM32H7的总线矩阵四通八达,但不是任意Bus Master总线主控端和Bus Slave设备端都可以相互通信的:

黑色加粗字体是64位总线(ITCM,DTCM,Flash A,Flash,AXI SRAM,FMC等),普通字体是32位总线。

访问通路(每个小方块里面的字符)

任何有数字的表示有访问通路。

短横杠“-”表示不可访问。

有灰色阴影的表示有实用价值的访问通路。

表格中具体数值所代表的含义

D=direct

1=via AXI bus matrix

2=via AHB bus matrix in D2

3=via AHB bus matrix in D3

4=via AHB/APB bridge in D1

5=via AHB/APB bridge in D2

6=via AHB/APB bridge in D3

7=via AHBS bus of Cortex-M7

多个数值组合 = 互连路径以数字的顺序经过多个矩阵或/和桥。

总线访问类型

普通字体表示32位总线。

斜体表示32位总线主机端/ 64位总线从机端。

粗体表示64位总线。

当前要对这个图有个了解,后面章节讲解各个外设的时候要用到,比如DTCM和ITCM不支持DMA1,DMA2和BDMA,仅支持MDMA。

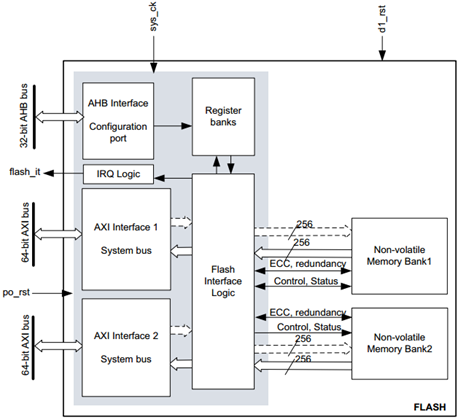

3.7 STM32H7的FLASH

首次学习STM32H7,要掌握以下几点认识即可:

1、双BANK,每个BANK的带宽都是64bits,如下图所示:

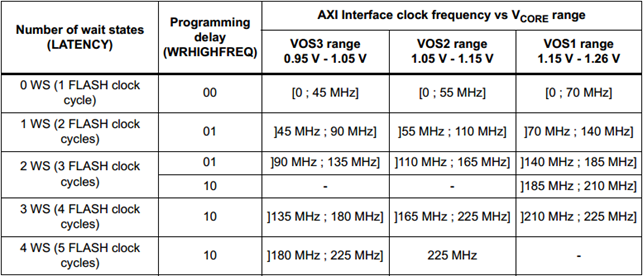

2、H7中Flash的延迟和主频关系。

H7中已经没有F1和F4系列中的ART Chrome加速,通过H7中的Cache加速即可。具体延迟数值和主频关系如下:

对于上面的表格,大家可以看到,当延迟等待设置为0的时候,即无等待,单周期访问,速度可以做到70MHz。增加1个Flash周期后,访问速度可以做到140MHz。当增加到3个或4个Flash周期后,最高速度可以做到225MHz。

3、Flash编程操作(写)最好以256bits为单位进行,应用中也可以小于256bits,但是容易造成ECC校验出问题,所以不推荐。Flash读操作支持64bits,32bits,16bits和8bits。

4、Flash支持ECC校验,每256bits配10bit的ECC位,可以检测到1个bit并纠正或者检测2个bit。随着芯片的制造工艺水平越高,带电粒子能产生的位翻转就越多,此时的ECC是必须要有的,一般可以纠正1-2个bit。安全等级高的Flash类存储器和RAM类都是必须要带ECC的。

- ECC相关知识

关于ECC方面的知识,专门整理了一个帖子:

http://www.armbbs.cn/forum.php?mod=viewthread&tid=86777。

3.8 STM32H7的RAM

(注,学习本小节,优先回顾本章节3.5.1小节的框图,另外H7的RAM区也是支持硬件ECC的)

STM32H7的RAM区分为好几个部分,下面分别进行说明:

TCM区

TCM : Tightly-Coupled Memory 紧密耦合内存 。ITCM用于运行指令,也就是程序代码,DTCM用于数据存取,特点是跟内核速度一样,而片上RAM的速度基本都达不到这个速度,所以有降频处理。

速度:400MHz。

DTCM地址:0x2000 0000,大小128KB。

ITCM地址:0x0000 0000,大小64KB。

AXI SRAM区

位于D1域,数据带宽是64bit,挂在AXI总线上。除了D3域中的BDMB主控不能访问,其它都可以访问此RAM区。

速度:200MHz。

地址:0x2400 0000,大小512KB。

用途:用途不限,可以用于用户应用数据存储或者LCD显存。

SRAM1,SRAM2和SRAM3区

位于D2域,数据带宽是32bit,挂在AHB总线上。除了D3域中的BDMB主控不能访问这三块SRAM,其它都可以访问这几个RAM区。

速度:200MHz。

SRAM1:地址0x3000 0000,大小128KB,用途不限,可用于D2域中的DMA缓冲,也可以当D1域断电后用于运行程序代码。

SRAM2:地址0x3002 0000,大小128KB,用途不限,可用于D2域中的DMA缓冲,也可以用于用户数据存取。

SRAM3:地址0x3004 0000,大小32KB,用途不限,主要用于以太网和USB的缓冲。

SRAM4区

位于D3域,数据带宽是32bit,挂在AHB总线上,大部分主控都能访这块SRAM区。

速度:200MHz。

地址:0x3800 0000,大小64KB。

用途:用途不限,可以用于D3域中的DMA缓冲,也可以当D1和D2域进入DStandby待机方式后,继续保存用户数据。

Backup SRAM区

备份RAM区,位于D3域,数据带宽是32bit,挂在AHB总线上,大部分主控都能访问这块SRAM区。

速度:200MHz。

地址:0x3880 0000,大小4KB。

用途:用途不限,主要用于系统进入低功耗模式后,继续保存数据(Vbat引脚外接电池)。

3.9 总结

本章节就为大家讲解这么多,让大家对STM32H7有个整体的认识,后面章节将逐个进行学习。

浙公网安备 33010602011771号

浙公网安备 33010602011771号