【FPGA学习】- FPGA实验篇(PLL/MMCM)

正常情况下,FPGA板子上往往只有一个时钟。如果需要器件工作在其它频率上,则需要使用PLL/MMCM来进行倍频分频操作。

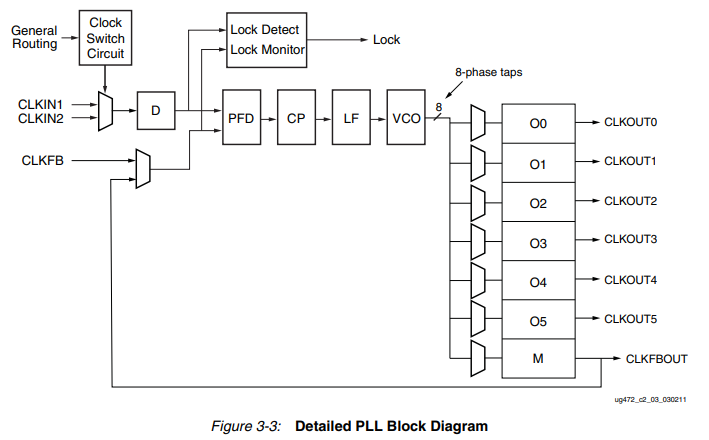

PLL:phase-locked loop,锁相环。锁相环路是一种反馈控制电路,特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,故名为锁相环。常用于有时钟倍频、分频、相位偏移和可编程占空比的功能。

MMCM:Mixed-Mode Clock Manager,混合模式时钟管理器。PLL功能是MMCM的子集,它是在PLL的基础上加了相位动态调整功能,PLL是模拟的,而动态调相是数字电路,所以称为混合模式。其相对于PLL的优势是相位可以动态调整,占用面积较大。

MMCM主要用于驱动器件逻辑(CLB、DSP、RAM等)的时钟。PLL是和IO资源紧密绑定的,占用面积小,常用于为内存接口生成所需的时钟信号,但也具有与其他器件逻辑的连接,因此如果需要额外的功能,它们可以用作额外的时钟资源。

在XILINX 7系列的FPGA中,具有时钟管理单元CMT(clock management tile)时钟资源,xc7z020 芯片内部有4个CMT,xc7z010芯片内部有2个CMT,为设备提供强大的系统时钟管理以及高速I/O通信的能力。时钟管理单元CMT的总体框图如下图所示,包括一个混合模式时钟管理器(MMCM)和一个锁相环(PLL)。

MMCM/PLL 的参考时钟输入可以是IBUFG(CC)即具有时钟能力的IO输入、区域时钟BUFR、全局时钟BUFG、GT收发器输出时钟、行时钟BUFH以及本地布线(不推荐使用本地布线来驱动时钟资源)。在本实验中,可以简单地理解为:外部时钟连接到具有时钟能力的输入引脚CCIO(Clock-Capable Input),进入MMCM/PLL,产生不同频率和不同相位的时钟信号,然后驱动全局时钟资源BUFG。

PLL/MMCM产生其它频率时钟实验

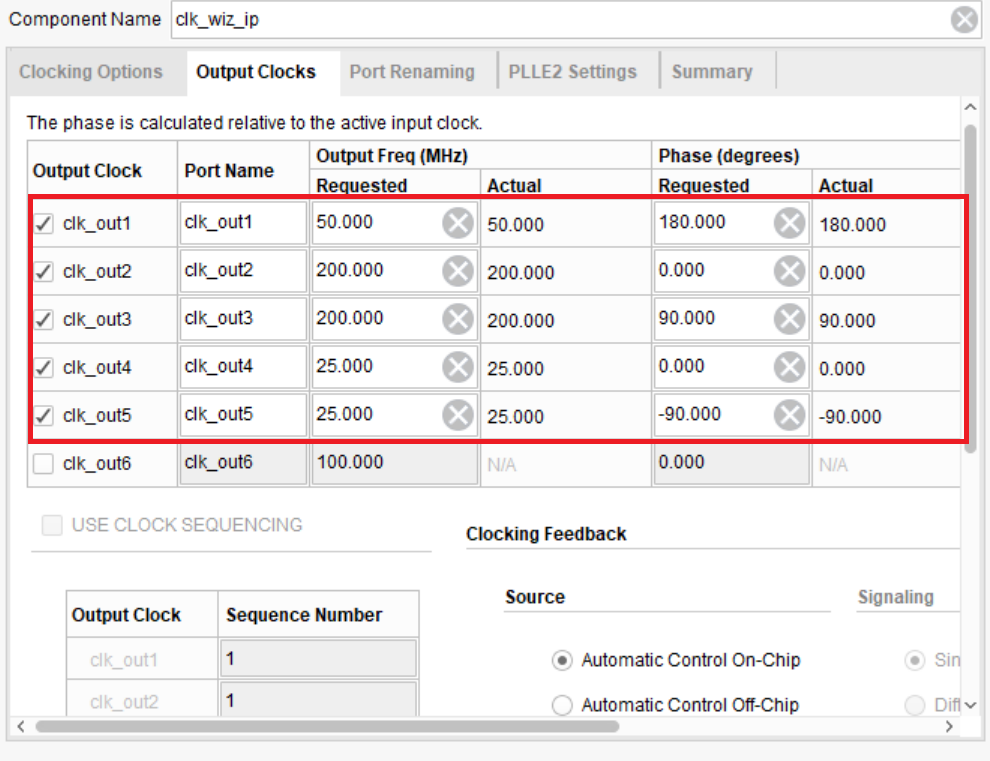

打开vivado,创建工程,在IP catalog中选择clock wizard,将IP核命名为clk_wiz_ip,选择Primitive为PLL,并将输入频率设定为50MHZ。

转到Output Clocks选项卡下,设定输出频率以及相位。

之后编写测试代码和仿真代码

module pll( input sys_clk, //系统时钟50MHZ input rst, output clkout1, output clkout2, output clkout3, output clkout4, output clkout5 ); wire locked; clk_wiz_ip instance_name ( // Clock out ports .clk_out1(clkout1), // output clk_out1-50MHZ_180DEG .clk_out2(clkout2), // output clk_out2-200MHZ .clk_out3(clkout3), // output clk_out3-200MHZ_90DEG .clk_out4(clkout4), // output clk_out4_25MHZ .clk_out5(clkout5), // output clk_out5-25MHZ_-90DEG // Status and control signals .reset(rst), // input reset .locked(locked), // output locked // Clock in ports .clk_in1(sys_clk)); // input clk_in1-50MHZ // INST_TAG_END ------ End INSTANTIATION Template --------- endmodule

testbench如下。

module pll_testbench; reg sys_clk, rst; wire clk_out1, clk_out2,clk_out3,clk_out4,clk_out5; wire locked; pll p1(sys_clk, rst, clk_out1, clk_out2,clk_out3,clk_out4,clk_out5); initial sys_clk = 0; always #2 sys_clk = ~sys_clk; initial begin rst = 1; #2 rst = 0; #1000 #50 $stop; end endmodule

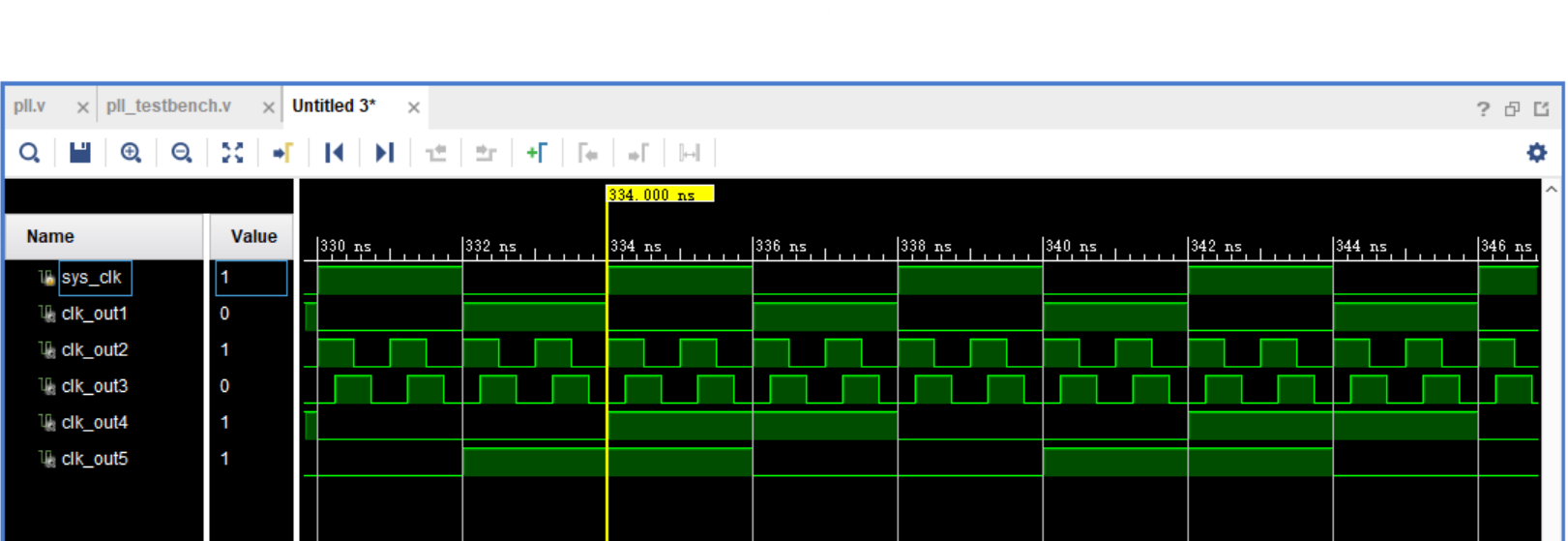

仿真结果如下。我们可以看到,输出与预想的输出保持一致,包括频率以及时钟的相位。板上验证由于需要示波器来测量引脚的输出,所以此实验不进行板上验证。

参考资料

[1] 黑金FPGA开发教程

[2] 正点原子FPGA开发教程

[3] XILINX官方开发文档

浙公网安备 33010602011771号

浙公网安备 33010602011771号