【FPGA学习】- ModelSim仿真软件的使用

ModelSim简介

Verilog仿真的常用软件有VCS,NC-Verilog和ModelSim,但是VCS,NC-Verilog都工作在Linux环境下,为了方便仿真,所以使用可以在Windows环境下使用ModelSim来进行仿真。ModelSim软件是由Mentor进行开发,速度相较于前两款软件略慢,但日常学习使用是足够的。

ModelSim安装地址

FPGA Software Download Center (intel.com)

下载地址:https://www.intel.com/content/www/us/en/collections/products/fpga/software/downloads.html?edition=pr

ModelSim使用流程

1.建立工程

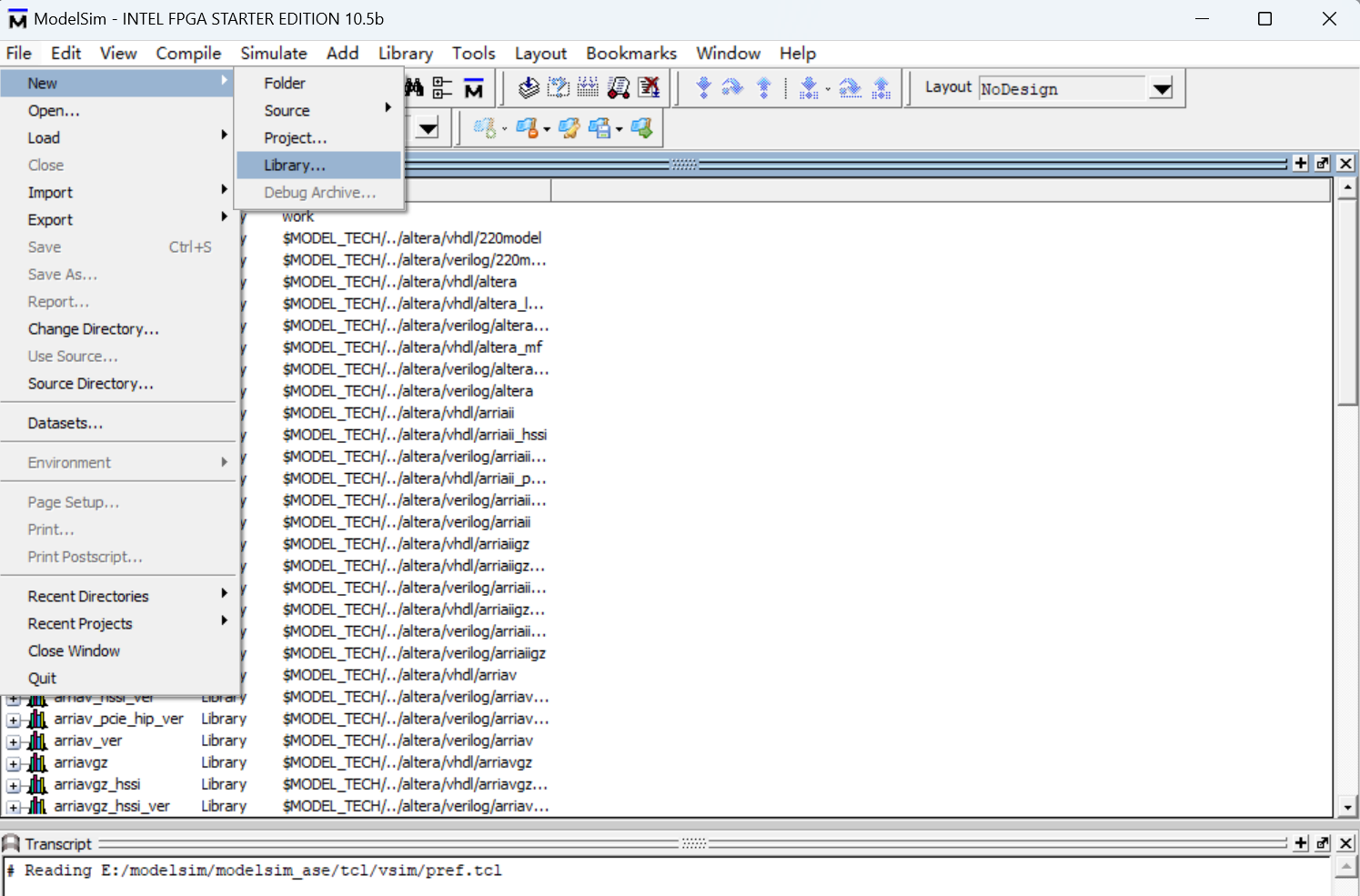

在建立工程(project)之前,一般先建立一个工作库(library),将这个工作库命名位work。首次使用ModelSim时,通过File->new->library来建立工作库work。

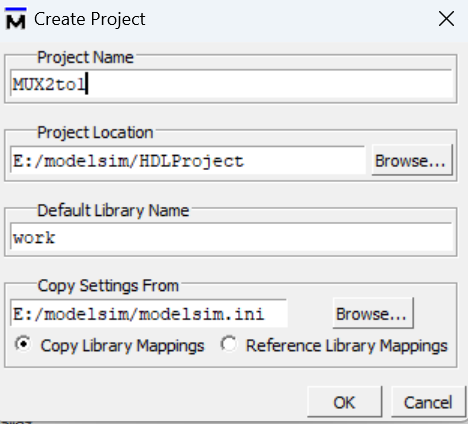

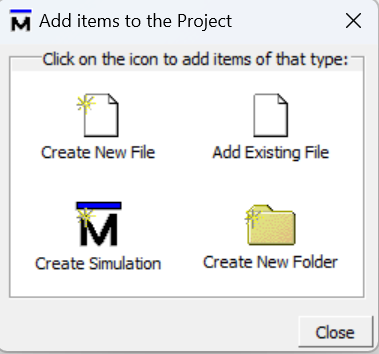

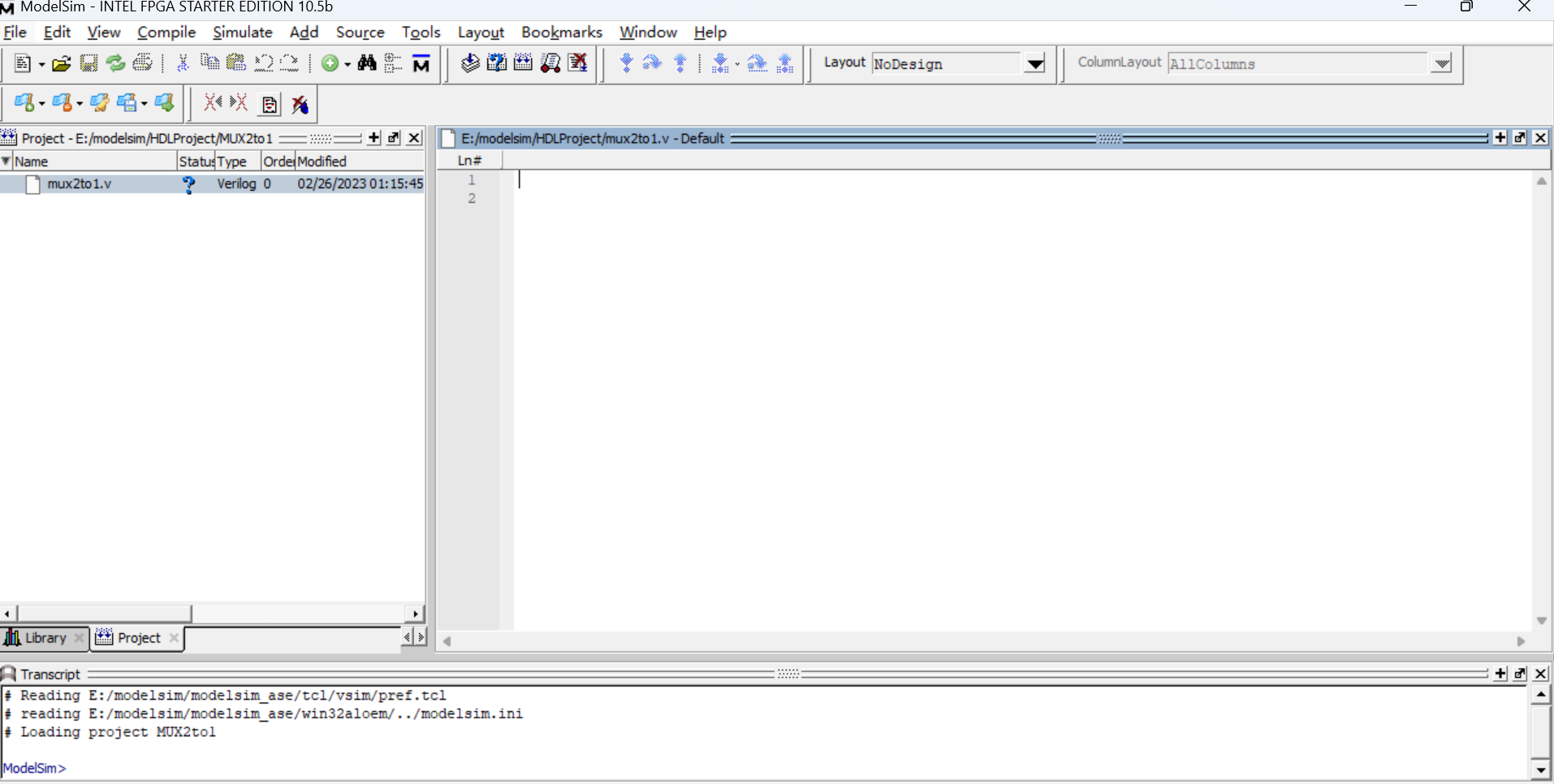

通过File->new->project来建立新工程,指定自己的项目名称,项目位置,默认的工作库等。本示例中使用一个2选1数据选择器电路作为演示,命名为MUX2to1,之后选择create new file。

2.添加文件

在新建文件之后,开始进行设计文件的编写。

2选1数据选择器的Verilog码如下:

//二选一数据选择器 module mux2to1(D0, D1, S); //模块端口定义 input D0, D1, Y; output Y; reg Y; always @(*) begin:mux //此处采用命名块的方式,调用时直接使用层次名引用的方式,如mux2to1.mux.(...) if(S == 1) Y = D1; else Y = D0; end endmodule

编写设计代码并且保存完成之后,保存并编写2选1数据选择器的激励模块,代码如下。

`timescale 1ns/1ns module testbench_mux2to1; reg P0, P1, PS; wire PY; //实例引用 mux2to1 m1(P0, P1, PS, PY); initial begin PS = 0; P1 = 0; P0 = 0; #1 PS = 0; P1 = 0; P0 = 1; #1 PS = 0; P1 = 1; P0 = 0; #1 PS = 0; P1 = 1; P0 = 1; #1 PS = 1; P1 = 0; P0 = 0; #1 PS = 1; P1 = 0; P0 = 1; #1 PS = 1; P1 = 1; P0 = 0; #1 PS = 1; P1 = 1; P0 = 1; #1 PS = 0; P1 = 0; P0 = 0; $stop; end initial begin $monitor($time, "\tS = %b\t\tD1 = %b\t\tD0 = %b\t\tY = %b\t", PS, P1, P0, PY); end endmodule

3.编译与调试

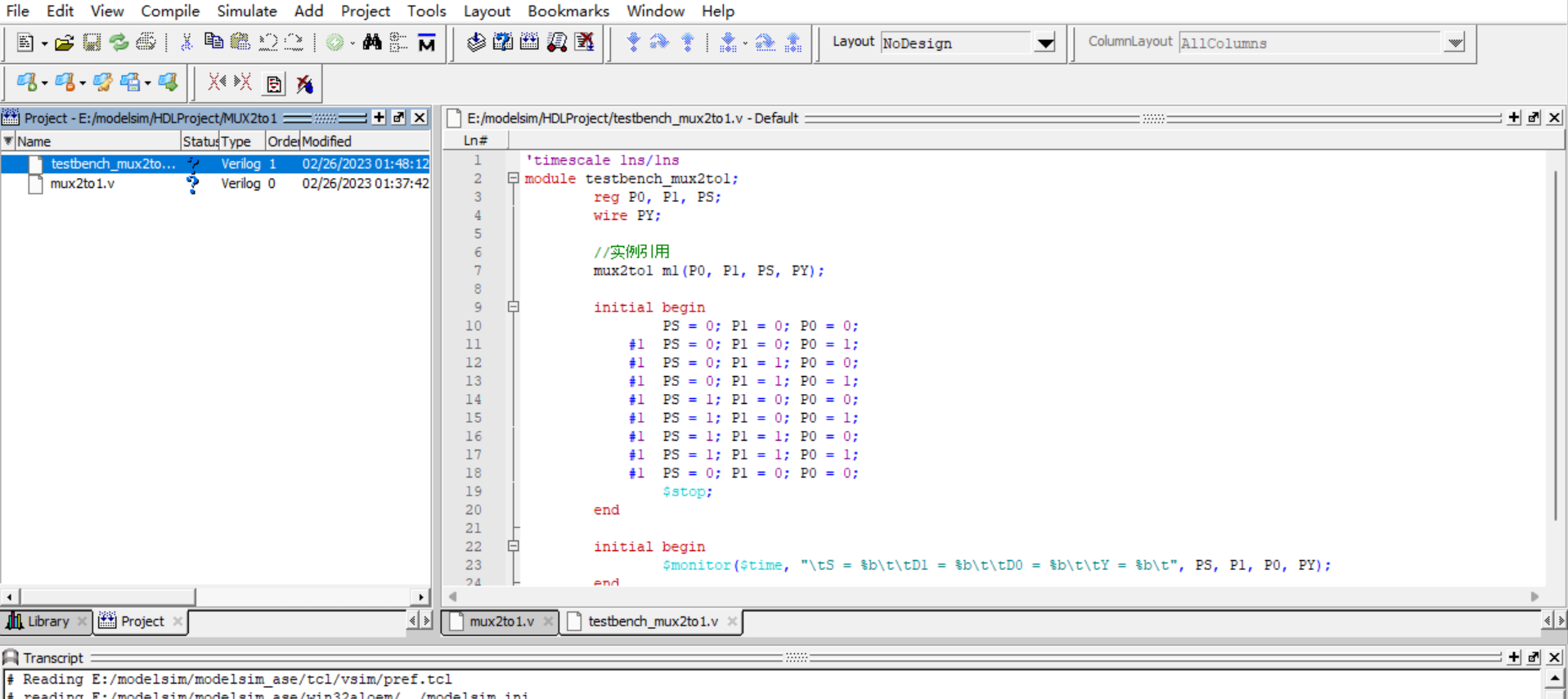

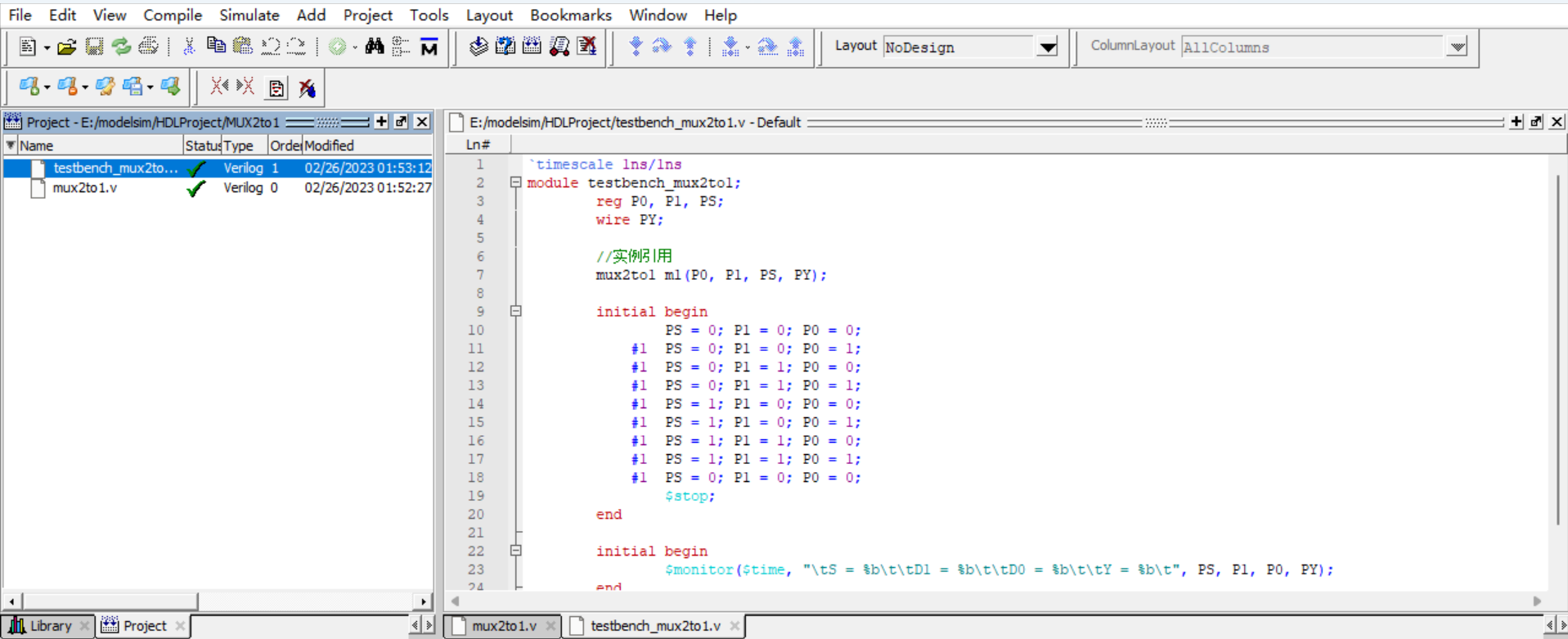

此时保存按钮变灰,但是文件名后面都有“?”,说明保存成功但尚未编译,此时选中其中一个文件,右键->compile->compile all,编译成功之后,文件名后面都变成绿色的“√”。(注意:编译报错修改后,必须先保存再编译。)

4.启动仿真

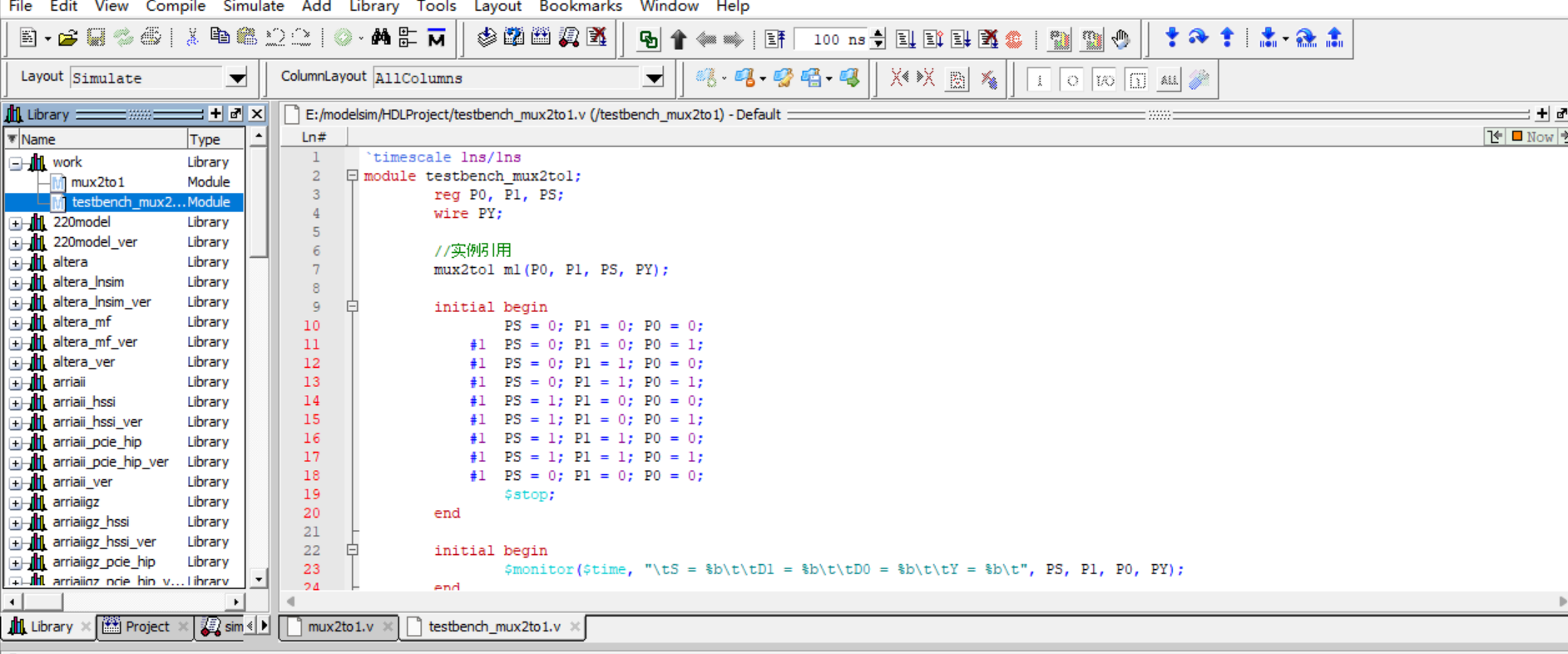

点击左下角的library,打开work,双击编写好的激励文件,将其载入仿真器。

运行之前,需要打开Wave窗口。选择主菜单中的View->Wave,打开Wave波形窗口。

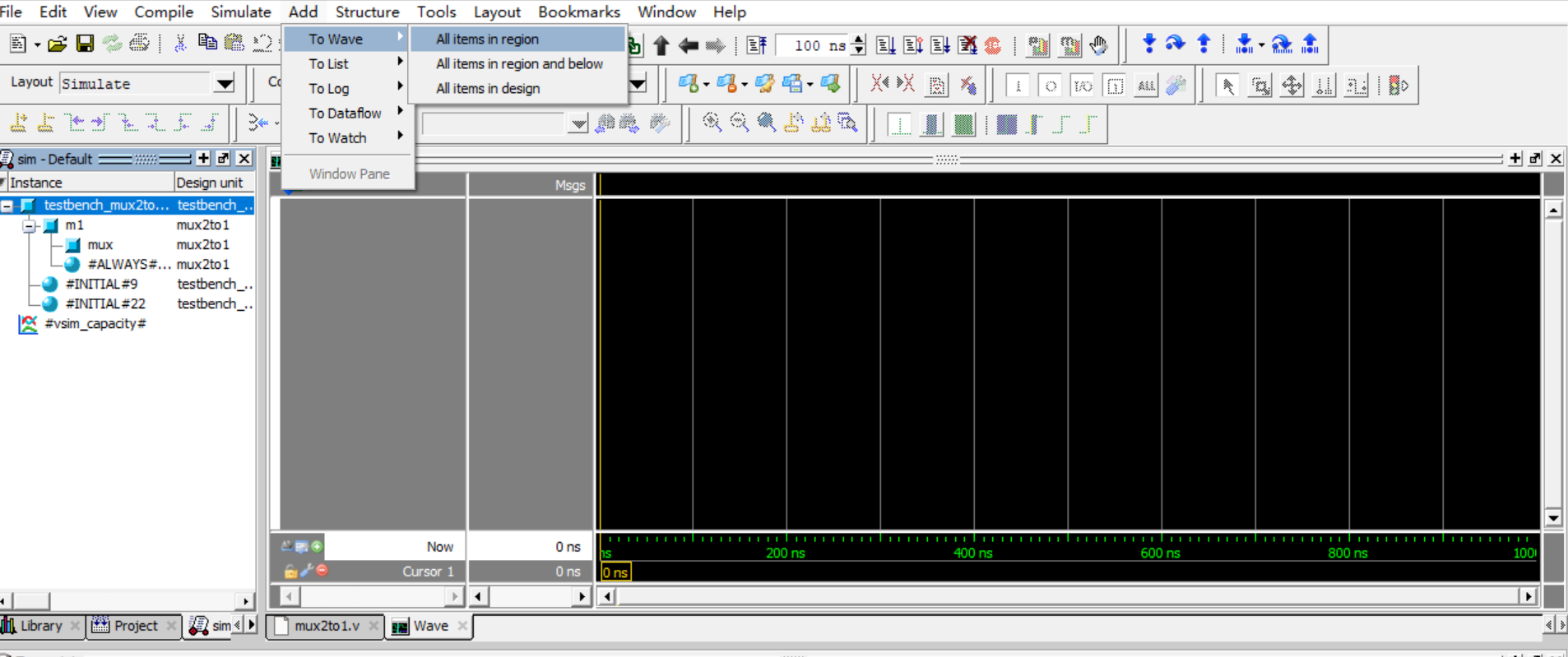

选择主菜单中Add->To Wave->All items in region,添加信号到Wave窗口。(需要选中整个文件,如图中蓝色部分)

选择主菜单中的Simulate->Run->All命令开始仿真。

5.观察结果

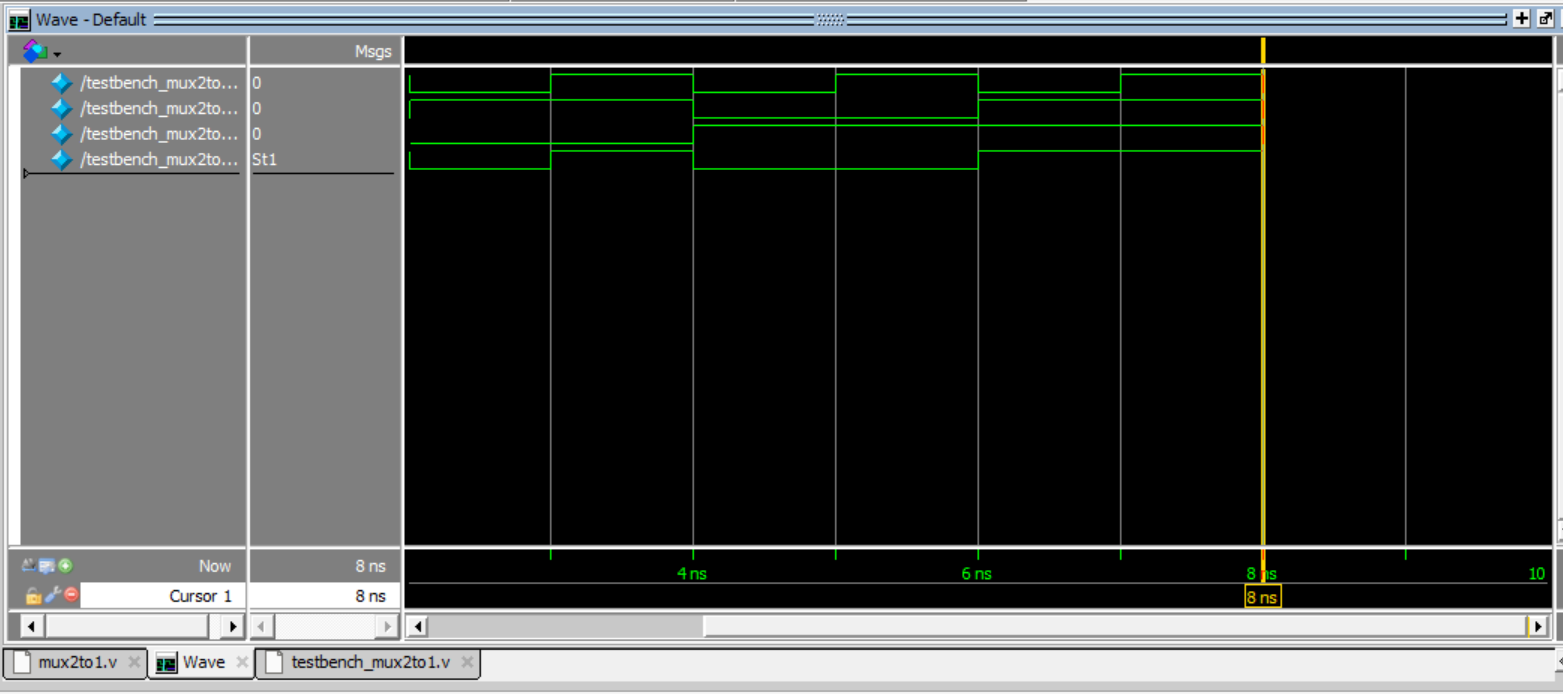

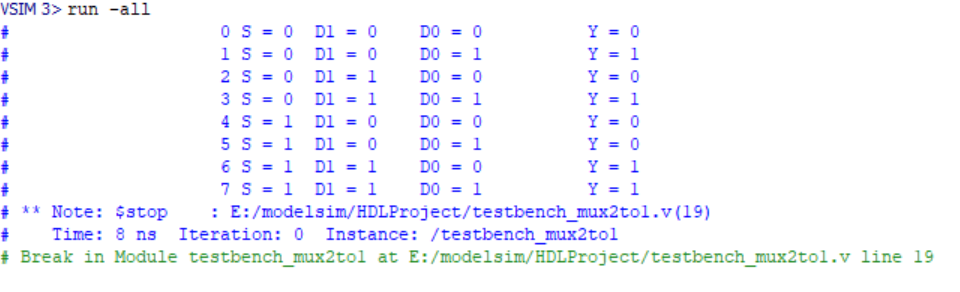

得到的结果波形图和文本方式显示结果如下图。观察结果与预期一致,所以设计实现。(文本结果显示在最底下的Transcript中)

浙公网安备 33010602011771号

浙公网安备 33010602011771号