关于IIC总线上的毛刺?

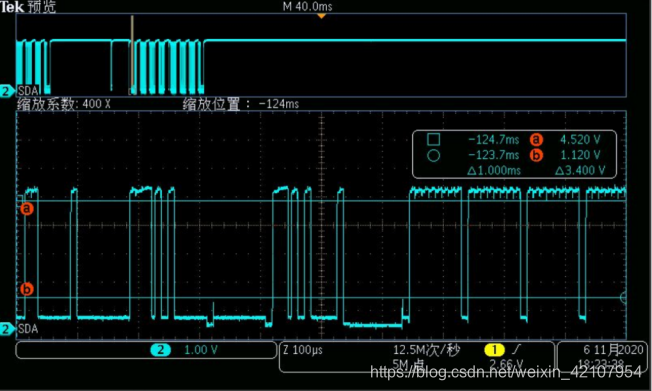

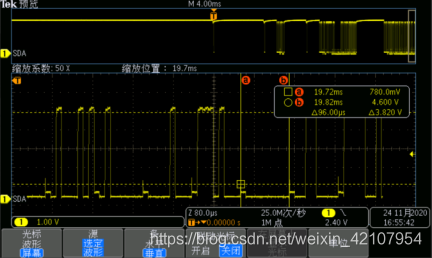

实际工程应用中,我们发现,用示波器测量IIC信号会发现总会有一些毛刺,而且仔细观察还可以发现这个毛刺是周期性的,这是为什么呢?

如图:

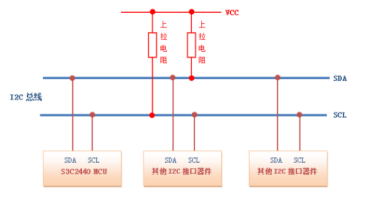

我们知道IIC是一种总线协议,如下:

之所以需要上拉电阻,源于IIC设计的开漏输出模式,设计上本身不支持高电平,只有低电平或者高阻态,其实这也跟总线协议相关,具体就不详细概述了。

每一个IIC设备都有不同的设备地址,主机根据不同的地址与不同的设备进行通信。

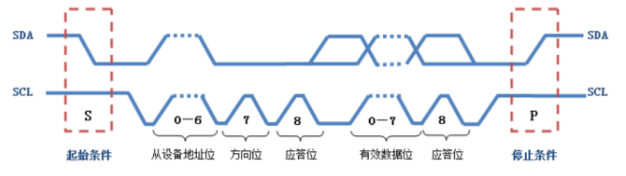

IIC的握手时序如下:

包含了起始条件,从设别地址,方向位,应答位,有效数据位,停止条件。

毛刺出现的原因,就在于IIC时钟传输的第九位:

主机发送了八个字节以后,需要放弃IIC控制权,将控制权交给从机,需要从机响应应答位;

主机放弃控制权的过程:

1.释放SDA,

2.由于SDA存在上拉电阻,此时SDA被拉高

3.这是从机响应了第九个时钟,开始获取SDA控制,将SDA拉低

以上只是一瞬间,表现为SDA会出现毛刺,且是周期性的。

以上,就是IIC会周期性出现毛刺的原因,当然,这个毛刺是可以解决的,使用模拟IIC的办法。

应答位之后会有一个尖峰,然后又恢复正常。如果是hi2c1.Init.ClockSpeed = 10000;,那么就是2.5us的尖峰

参考:https://blog.csdn.net/dajunzhi/article/details/109217049

I2C sda毛刺

在master向slave传输8bit数据之后,sda控制权由master交由slave,此时slave控制sda发送一个ack反馈信号,sda为低电平信号,在经过sclk为高时接收到sda的低电平信号,在sclk变为低电平时,sda控制权由slave交回到master,在交回过程中有一小段时间sda处于既不由master又不为slave控制的空闲阶段,在空闲阶段sda默认为高电位(因为有上拉电阻),如果master要马上传输低电平,sda将由高电平转为低电平,会存在一个小的毛刺。

所以这属于正常现象,不会影响iic通讯。

浙公网安备 33010602011771号

浙公网安备 33010602011771号