DDR3学习笔记一

- 从SDRAM到DDR3

- DDR3硬件设计

- DDR3操作时序及IP核设计

- DDR3读写程序设计

- 从SDRAM到DDR3

- SDRAM概念

SDRAM:(synchronous dynamic random access memory),同步动态随机存储器。同步,时钟频率和CPU总线时钟一致。内部的命令的发送和数据的传输都以此时钟为基准;动态:需要不断刷新保持数据不丢失;随机:数据不是线性一次存储,而是自由指定地址进行数据的读写。

物理Bank (Physical Bank):

传统内存系统为了保证CPU的正常工作,必须一次传输完CPU在一个传输周期内所需要的数据。而CPU在一个周期内能接收的数据容量就是CPU数据总线的位宽(bit)。

芯片位宽:

每一片SDRAM缓存芯片本身的位宽。

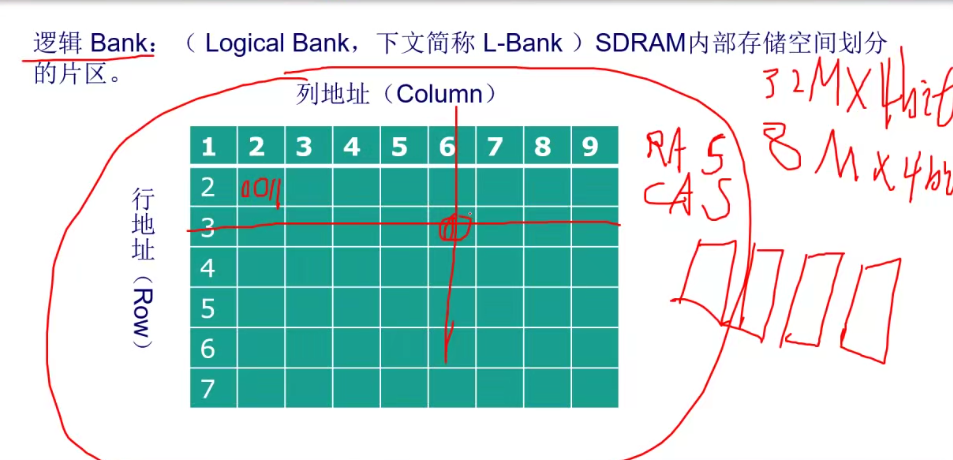

逻辑Bank:![]()

一片SDRAM分成4个逻辑Bank。

芯片位宽等于逻辑Bank中每一个存储体的数据位宽。SDRAM不仅有行地址和列地址,还有Bank地址。

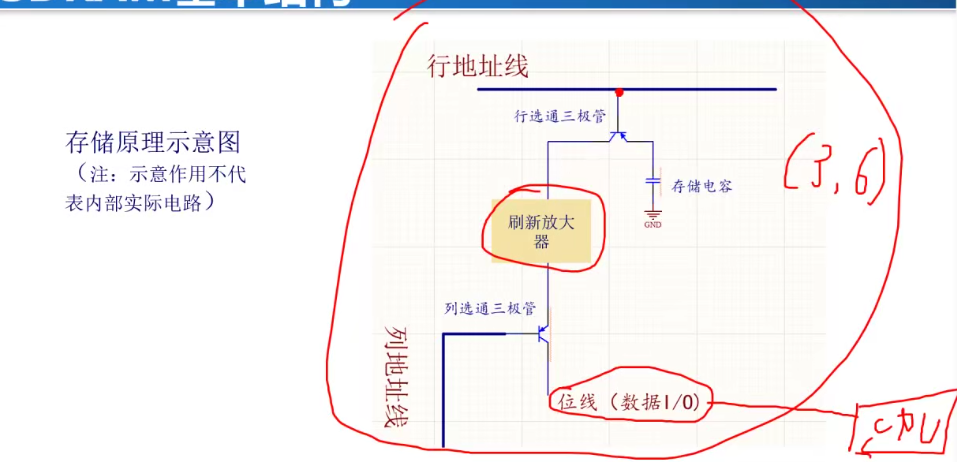

如何实现选中第3行第6列?![]() 刷新放大器可以实现数据回写。存储电容充电为写入,放电为读出。

刷新放大器可以实现数据回写。存储电容充电为写入,放电为读出。

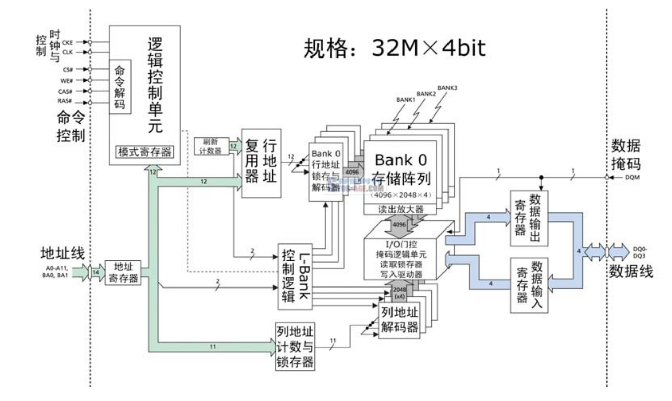

SDRAM基本结构:

![]()

- SDRAM的操作时序

- 从SDRAM到DDR SDRAM

- DDR的进一步发展

- SDRAM概念

刷新放大器可以实现数据回写。存储电容充电为写入,放电为读出。

刷新放大器可以实现数据回写。存储电容充电为写入,放电为读出。

浙公网安备 33010602011771号

浙公网安备 33010602011771号