FPGA基本结构之FF

仅初学触发器,而且仅上了一节课。所以以下内容不一定正确,请多指错。

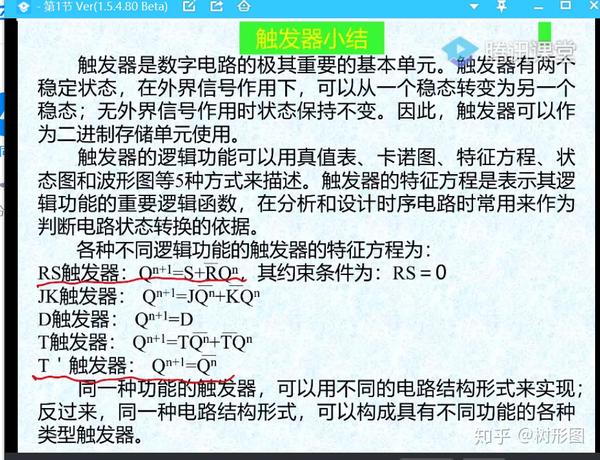

R-S触发器(Set/Reset trigger)

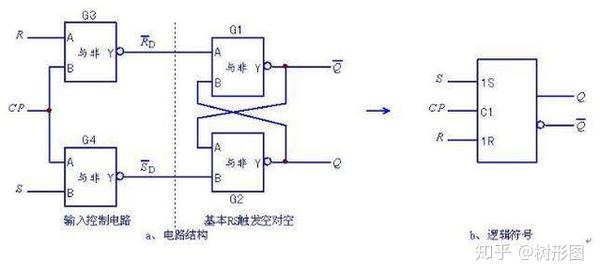

1. 基本R-S触发器(与非)

这个讲的很好。

特征方程

特征方程的直观理解:输入向量(S,R),输出向量(Q, )在CP=1时

即只在输入为(0,0)时不变,其余时候输入什么输出什么。

直观理解为一个信息通道的开关,只在(0,0)时关闭。

即:二维向量 二维向量 , K是开关,在(0,0)时关闭。

对于从CP来的两条输入线和S,R两条线地位相同,由对称性,所以CP=(0,0)(即CP=0)时也使输出不变。

但是R-S触发器还存在空翻现象,所以发明了主从R-S触发器。

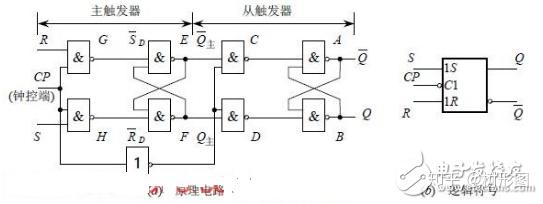

2.主从R-S触发器(与非)

先摆一张最教科书式的图。

接下来按之前的理解我们可以把一个R-S触发器理解成一个开关k,那么主从R-S触发器就是两个不同时开或同时关的开关。用箭头代表信息的管道。

则主从R-S触发器就是这样:输入二维向量 输出二维向量。其中

由于CP控制不会同时开或关。

是不是比起图片简明多了。

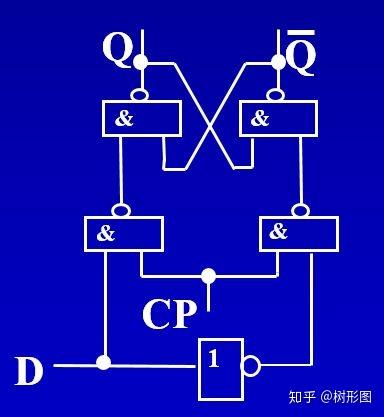

D触发器

在R-S触发器中有输入为(1,1)的非法态。之所以非法是因为仔细分析可以发现从输入(0,0)转到(1,1)时会出现输出循环震荡的现象。D触发器就是为了解决这个问题而诞生。

很自然想到加个非门这样就一定不会出现输入为(1,1)的情况了,这个很容易理解。如下图。

不过为了生产,使用的门种类和数量越少越好,所以再进一步想。

我们可以发现只有在CP=1且输入为(1,1)时R-S触发器才可能有混乱。

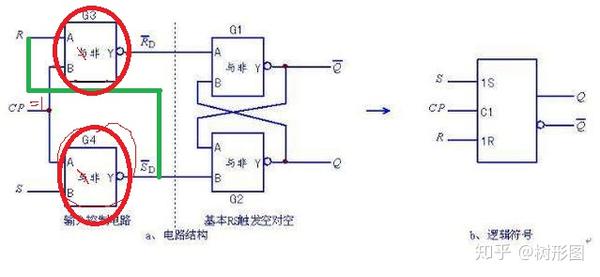

而在CP=1时,R-S触发器的前面的两个与非门(见图中红圈圈出的)就等于非门。如果我们让R等于S的非那么一定不会出现(1,1)的情况。

为了让R等于S的非,我们用绿线(如图)将R与S非过后相连。

这就是第二种D触发器,相比上一种减少了门的数量和种类。

J-K触发器

T触发器

浙公网安备 33010602011771号

浙公网安备 33010602011771号