Verilog中的延时模型

Verilog中的延时模型

一、专业术语定义

- 模块路径(module path): 穿过模块,连接模块输入(input端口或inout端口)到模块输出(output端口或inout端口)的路径。

- 路径延时(path delay):与特定路径相关的延时

- PLI:编程语言接口,提供 Verilog数据结构的过程访问。

- 时序检查(timing check):监视两个输入信号的关系并检查的系统任务,以保证电路能正确工作。

- 时序驱动设计(timing driven design):从前端到后端的完整设计流程中,用时序信息连接不同的设计阶段

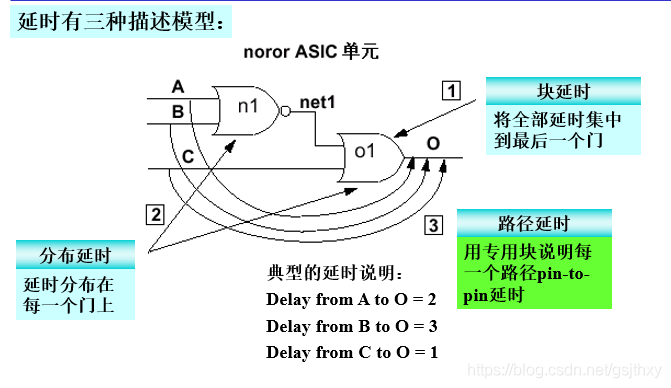

二、延时模型类型(Delay Modeling Types)

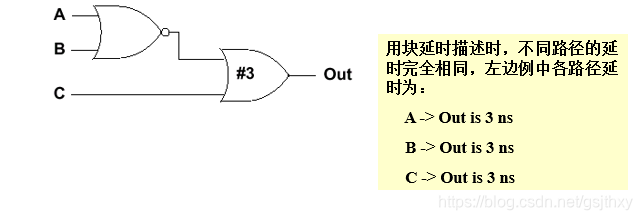

2.1、块延时(Lumped Delay)

- 块延时方法是将全部延时集中到最后一个门上。这种模型简单但不够精确,只适用于简单电路。因为当到输出端有多个路径时不能描述不同路径的不同延时。

- 可以用这种方法描述器件的传输延时,并且使用最坏情况下的延时(最大延时)。

-

`timescale 1ns/ 1ns

-

-

module noror( Out, A, B, C);

-

output Out;

-

input A, B, C;

-

-

nor n1 (net1, A, B);

-

or #3 o1 (Out, C, net1);

-

-

endmodule

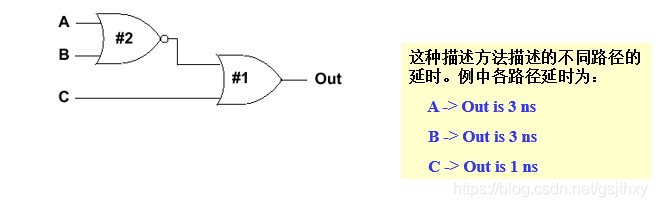

2.2、分布延时(Distributed Delays)

- 分布延时方法是将延时分散到每一个门。在相同的输出端上,不同的路径有不同的延时。分布延时有两个缺点:

– 在结构描述中随规模的增大而变得异常复杂。

– 仍然不能描述基本单元 (primitive) 中不同引脚上的不同延时。

-

`timescale 1ns/ 1ns

-

-

module noror( Out, A, B, C);

-

output Out;

-

input A, B, C;

-

-

nor #2 n1 (net1, A, B);

-

or #1 o1 (Out, C, net1);

-

-

endmodule

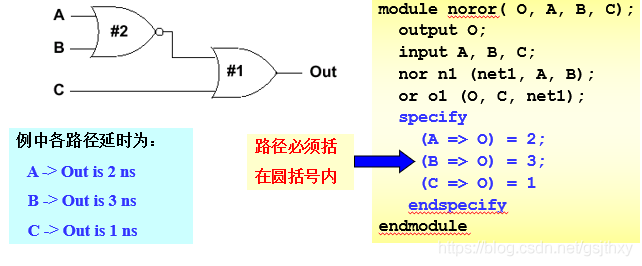

2.3、模块路径延时(Module Path Delays)

- 在专用的specify块描述模块从输入端到输出端的路径延时。

– 精确性:所有路径延时都能精确说明。

– 模块性:时序与功能分开说明

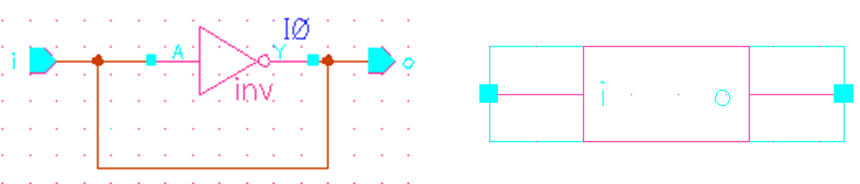

2.4、结构描述的零延时反馈(Loop)

• 当事件队列中所有事件结束时仿真前进一个时片。在某种零延时反馈情况下,新事件在同一时片不断的加入,致使仿真停滞在那个时片。

• 若在结构描述中出现从输出到输入的零反馈情况,多数仿真器会检测到这个反馈并产生错误信息。 Verilog 的lint checker 对这种情况会提出警告。

• 解决这个问题的方法是在电路中加入分布延时。路径延时不能解决零延时振荡问题,因为输出信号在反馈前不会离开模块。

2.5、精确延时控制

2.5.1、在Verilog中,可以:

- 说明门和模块路径的上升(rise)、下降(fall)和关断(turn-off)延时

-

and #(2,3) (out, in1, in2, in3); // rise, fall

-

-

bufif0 #( 3,3,7) (out, in, ctrl); // rise, fall, turn- off

-

-

(in => out) = (1, 2); // rise, fall

-

-

(a => b) = (5, 4, 7); // rise, fall, turn- off

- 在路径延时中可以说明六个延时值(0 ®1, 1 ®0, 0 ®Z, Z ®1, 1 ®Z, Z ®0)

(C => Q) = (5, 12, 17, 10, 6, 22);

- 在路径延时中说明所有12个延时值(0 ®1, 1 ®0, 0 ®Z, Z ®1, 1 ®Z, Z ®0, 0 ®X, X ®1, 1 ®X, X ®0, X ®Z, Z ®X)

(C => Q) = (5, 12, 17, 10, 6, 22, 11, 8, 9, 17, 12, 16);

- 上面所说明的每一个延时还可细分为最好、典型、最坏延时。

or #( 3.2:4.0:6.3) o1( out, in1, in2); // min: typ: max

not #( 1:2:3, 2:3:5) (o, in); // min: typ: max for rise, fall

user_module #(1:2:3, 2:3:4) ( ……);在Cadence Verilog中还不支持

(b => y) = (2: 3: 4, 3: 4: 6, 4: 5: 8); // min: typ: max for rise, fall, and turnoff

延时说明定义的是门或模块的固有延时。输入上的任何变化要经过说明的延时才能在输出端反映出来。如果没有延时说明,则基本单元的延时为0。分布关断延时只对三态基本单元有效。

- 上升延时是输出转换为1时的延时

- 下降延时是输出转换为0时的延时

- 关断延时输出转换为三态时的延时

- 到X的转换延时是最小延时,而从X到其它值的转换使用最坏延时

– 如果说明了上升、下降和关断延时,则 1->X 的转换延时使用上升和关断延时的最小值。 X->0的延时为下降延时; X->Z 的转换为关断延时。

– 如果只说明了上升和下降延时,则 1->X 和 X->0 使用下降延时, X->Z 使用上升和下降延时的最小延时

– 如果只说明了一个延时,则所有转换使用这个延时。

– 如果说明了六个延时,则 1->X 使用 1->X 和 1->Z 中最小延时; X->0 使用 1->0 和 X->0 的最大延时; X->Z 使用 1->Z 和 0->Z 中的最大延时。

浙公网安备 33010602011771号

浙公网安备 33010602011771号