理解单端,全差分、伪差分

单端信号:

单端信号(single-end)是相对于差分信号而言的,单端输入指信号有一个参考端和一个信号端构成,参考端一般为地端。

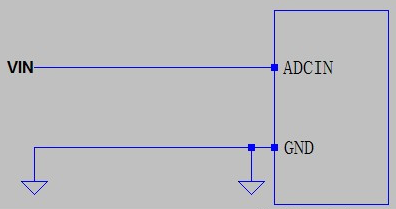

ADC单端输入

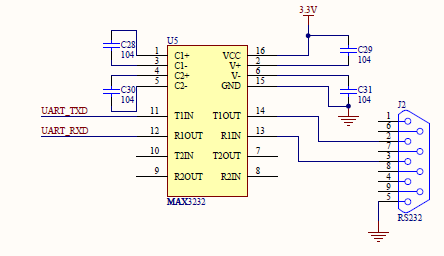

比如说UART232串口中,发送端TXD,接收端RXD,参考端是地,GND,是典型的单端信号输入输出。

单端输入时,是判断信号与 地的电压差。

RS232单端信号接口示意图

差分信号:

差分(Differential)是将单端信号进行差分变换,输出两个信号,一个和原信号同相,一个和原信号反相。差分信号有较强的抗共模干扰能力,适合较长距离传输,单端信号则没有这个功能。

差分输入时,是判断两信号线的电压差。

差分信号波形图

信号受干扰时 ,差分的两根线会同时受到影响,但电压差变化不大。而单端输入的一线变化时,GND不变,所以电压差变化较大。

差分信号和普通的单端信号走线相比,最明显的优势体现在一下三个方面:

-

抗干扰能力强,因为两根差分走线之间的耦合很好(最好相邻布线),当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

-

能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

-

时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。目前流行的LVDS(lowvoltagedifferentialsignaling)就是指这种小振幅差分信号技术。

-

单端转差分:

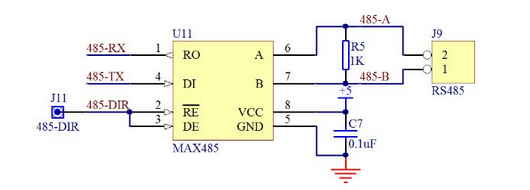

RS485电路图,RS232与RS485之间的转换。485-A与485-B是差分输入输出对,485-RX为单端输出,485-TX为单端输入,485-DIR为方向控制,实现半双工通信。

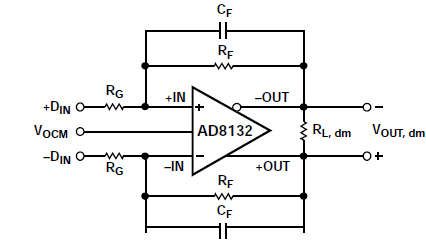

上图为典型全差分电路,所谓全差分即输入和输出均为差分的电路。上图所示为全差分运放电路。

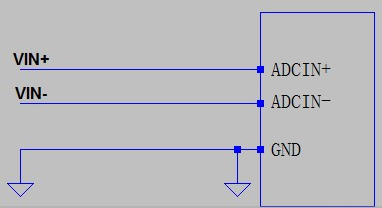

ADC差分输入

伪差分输入:

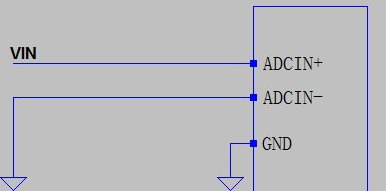

ADC伪差分输入

为了既有差分输入的优点又有单端输入简单的优点,还有一种伪差分输入,通过把信号地连到ADCIN-端实现一种类似差分的连接。

伪差分(Pseudo-differential)信号连接方式减小了噪声,并允许在仪器放大器的共模电压范围内与浮动信号连接.在伪差分模式下,信号与输入的正端连接,信号的参考地与输入的负端连接。伪差分输入减小了信号源与设备的参考地电位(地环流)不同所造成的影响,这提高了测量的精度。

伪差分输入与差分输入在减小地环流和噪声方面是非常相似的,不同的方面在于,差分输入模式下,负端输入是随时间变化的,而在伪差分模式下,负端输入一定仅仅是一个参考。描述伪差分的另外一种方式就是,输入仅仅在打破地的环流这个意义上是差分的,而参考信号(负端输入)不是作为传递信号的,而仅仅是为信号(正端输入)提供一个直流参考点。

相关问题:

-

-

伪差分输入能有效抑制共模噪声吗?

-

能部分抑制。由于两线对“大地”阻抗不一致,所以抑制效果有限。

-

-

伪差分输入与差分输入相比有哪些优缺点?

-

既然是“伪装”的,原则上没有优点只有缺点。其缺点就是两线不对称,共模抑制效果有限。硬要凑一个优点的话,就是可以勉强将单端输出信号伪装成差分,效果比完全单端连接效果稍好一点(解决两端地的小范围浮动)。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

浙公网安备 33010602011771号

浙公网安备 33010602011771号