yosys工具

ysyx的yosys工具

yosys工具使用

执行下面命令(粗粒度,yosys使用字级单元表示)

read_verilog counter.v

//细化

hierarchy -check -top counter

//查看rtl视图

show

//粗粒度综合

proc

//优化

opt

//执行fsm,memory 视图是不变的

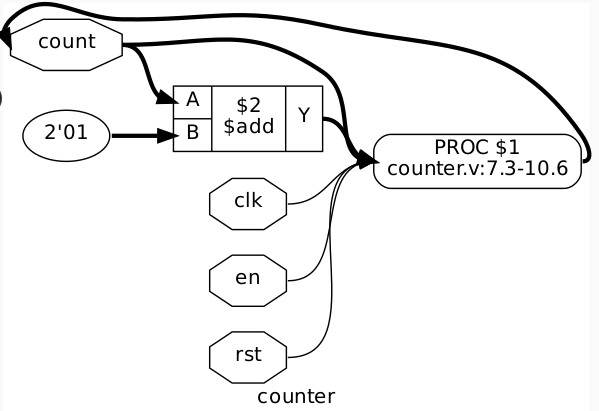

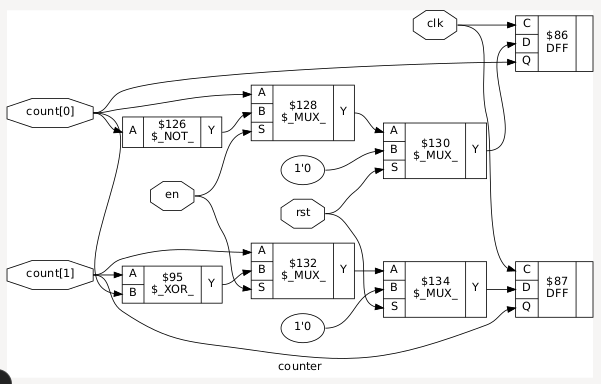

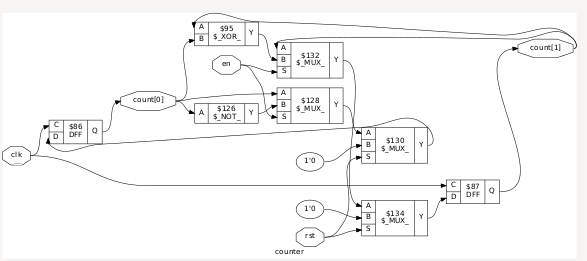

show命令后显示如下图片,这个时候存在过程块proc

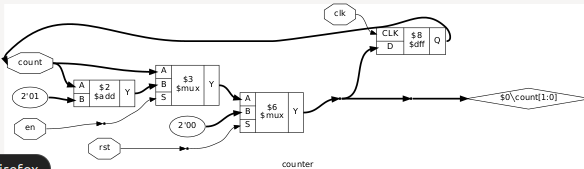

执行proc后,过程块消失,全部有小的cell表示

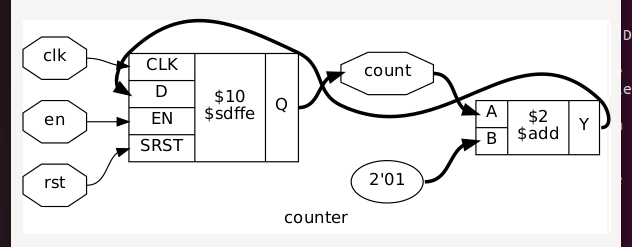

执行opt命令,结果表示单元数目显著减少

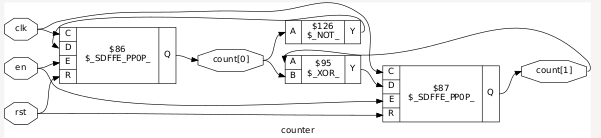

执行下面命令(细粒度,yosys使用门级电路表示)

//转换为门电路

techmap

//对一些多位的线网和端口进行拆分, 否则RTLIL中将会包含不必要的位抽取和位拼接操作

splitnets -ports

//一定要执行opt -full,否则无法show(原因是因为节点太多无法显示)

opt -full

执行下面命令(工艺映射),先创建个cell.lib

dfflibmap -liberty cell.lib

执行下列命令,先读入规则

read_liberty -lib cell.lib

继续执行

abc -liberty cell.lib

clean

至此,完成从RTL代码到网表的转换.

//保存网表文件

write_verilog netlist.v

//输出报告

stat -liberty cell.lib

开源EDA评估电路性能

- 在yosys-sta下执行

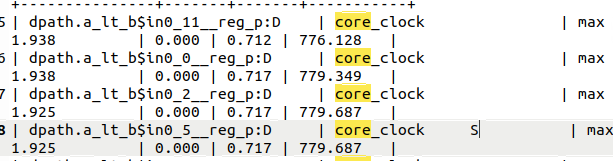

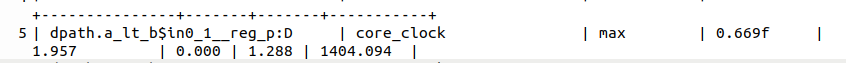

make sta查看result下的gcd.rpt可以看到时序报告

![image]()

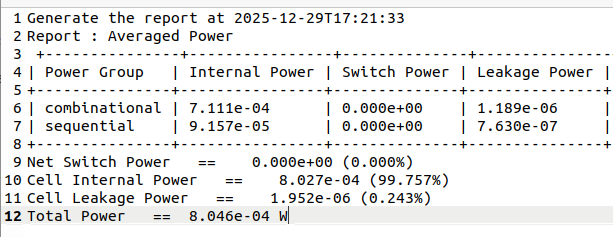

core_clock显示未1404.094MHz - 查看gcd.pwr可以查看功耗

![image]()

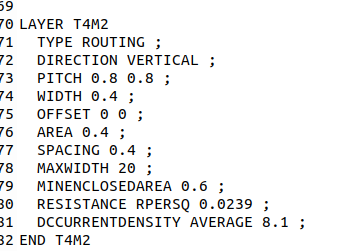

- 阅读ICsprout55的工艺LEF文件, 其中包含多少层金属层? 并尝试根据线宽和走线间距, 推测每层金属层的作用.

共有6层

MET1-MET5 T4M2 的TYPE都是布线,BT4M2是最宽的所以是电源线。width0.4其他都是0.1

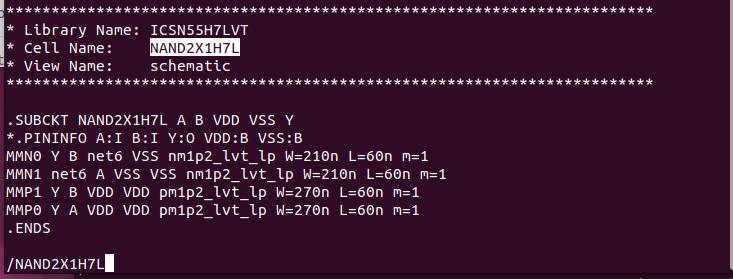

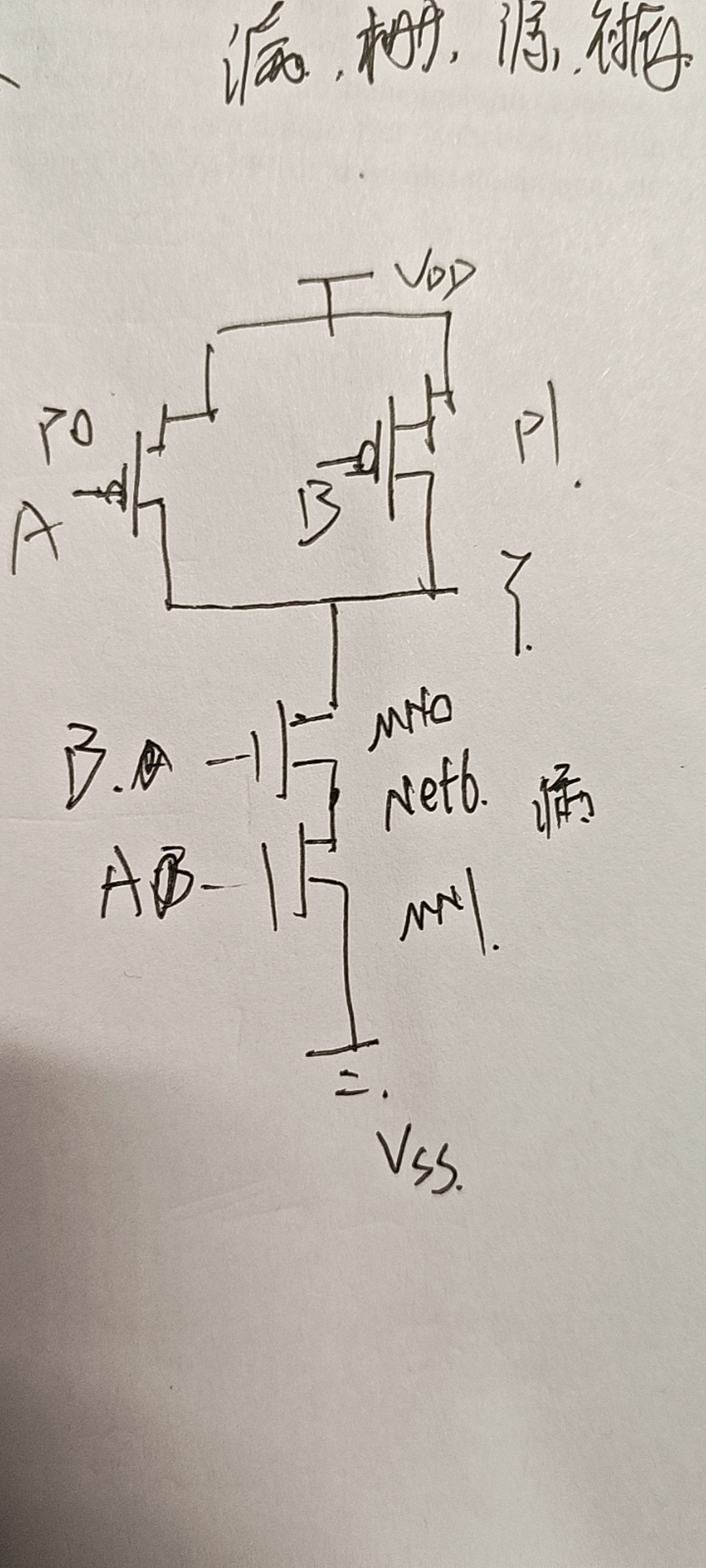

- 尝试根据上述CDL描述, 画出标准单元NAND2X1H7L的晶体管结构, 并检查其功能与与非门是否一致.

MMN0 后 Y B NET6 VSS 依次对应漏,栅,源,衬底

- ICsprout55的LIB文件中还存在命名类似OAI22X1H7L的标准单元, 其功能并不直观. 尝试查阅标准单元OAI22X1H7L相关的属性, 了解其功能.

OAI:Or-And-Invert 或与非门 6个管子,数集魅力时刻 doge

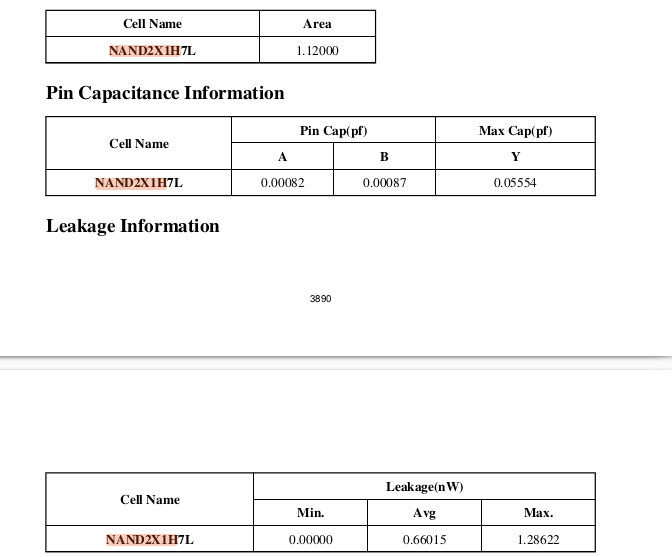

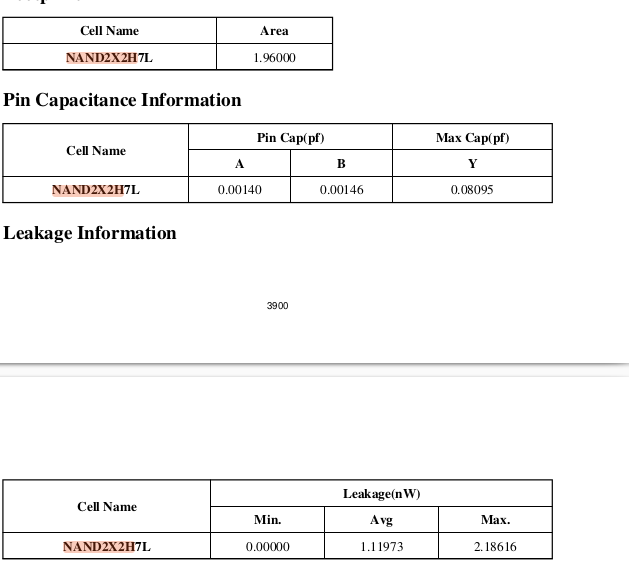

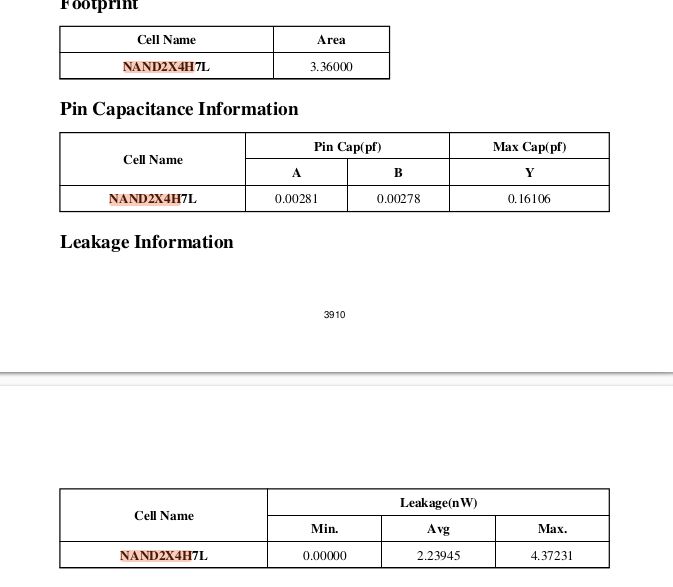

- 尝试查阅NAND2X1H7L, NAND2X2H7L和NAND2X4H7L的相关属性, 对比其面积和功耗.

路径yosys-sta/pdk/icsprout55/IP/STD_cell/ics55_LLSC_H7C_V1p10C100/ics55_LLSC_H7CL/do 有好东西

依次是NAND2X1H7L, NAND2X2H7L和NAND2X4H7L,驱动越强面积和功耗越大

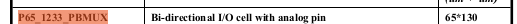

- 尝试查阅ICsprout55中的相关文件, 了解一个二输入与非门的尺寸以及一个I/O单元的尺寸, 并对比它们.、

不是一个量级,io单元要远大于与非门尺寸。原因:I/O 单元(如 GPIO、电源 Pad 等)需要承载静电保护 (ESD)、大电流驱动以及焊盘连接,因此它们的尺寸与标准单元完全不在一个数量级。

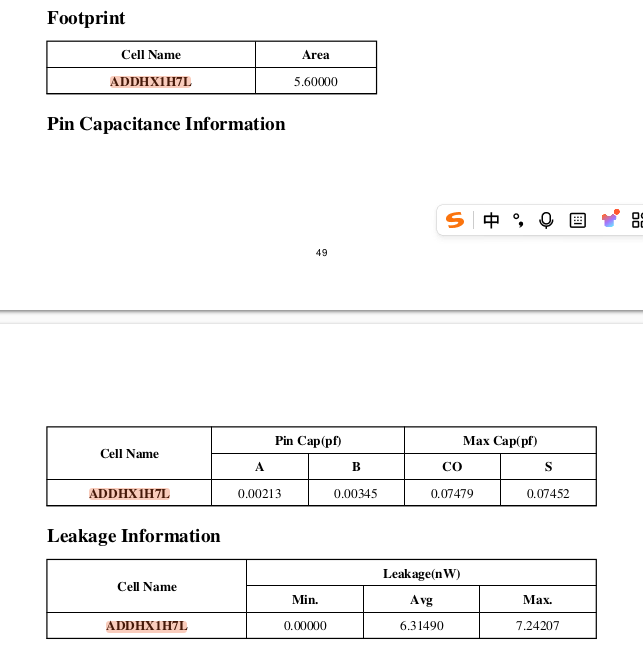

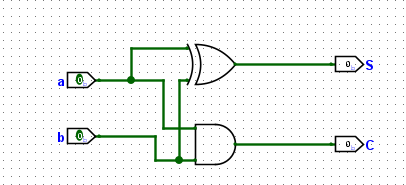

- 以ADDHX1H7L为例, 尝试从标准单元库的相关文件中找到这个标准单元的面积和晶体管结构. 假设某标准单元库不提供半加器的标准单元, 需要通过若干基本逻辑门的标准单元来搭建半加器, 请计算此时所需的面积和晶体管数量.

前面搭建过半加器,一个xor和一个and

-ICsprout55提供了不同PVT角的LIB文件(位于yosys-sta/pdk/ICsprout55IP/STD_cell/ics55_LLSC_H7C_V1p10C100/ics55_LLSC_H7CL/liberty目录下). 尝试为yosys-sta项目更换不同PVT角的LIB文件(在yosys-sta/scripts/pdk/icsprout55.tcl中指定), 然后重新评估电路的性能, 对比不同PVT角下的评估结果.

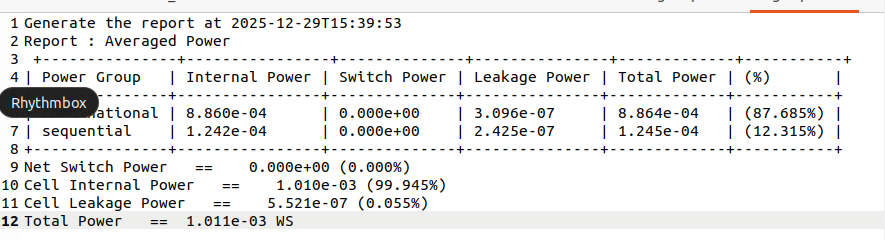

一共就两个工艺角,ss下频率明显慢了,功耗也少了

浙公网安备 33010602011771号

浙公网安备 33010602011771号