IEEE 802.3

IEEE 802.3 Single-mode Optical Fiber Ethernet Standards

https://www.tiafotc.org/ieee-802-3-ethernet-standards-update/singlemode-standards-update/

There are three 9 µm-diameter single-mode optical fiber types recommended by TIA Standards for new installations:

- Inside Plant (OS1a) single‑mode has the highest cabled attenuation of all options, 1.0 dB/km at 1310 nanometer (nm) and 1550 nm wavelengths, and supports indoor and short-haul local area network (LAN), data center, enterprise, and FTTx or “last mile” applications

- Outside Plant (OS2) single‑mode has the lowest cabled attenuation of all options, 0.4 dB/km at 1310 nm and 1550 nm, and is ideal for long-haul wide area network (WAN) applications

- Indoor-Outdoor single‑mode has a maximum cabled attenuation of 0.5 dB/km at 1310 nm and 1550 nm, which is less than OS1a but more than OS2, making it a good choice for between building and mid-haul metropolitan area network (MAN) applications

All three fiber types are characterized as “low‑water peak”, meaning the maximum attenuation requirement at 1383 nm is equivalent to the maximum attenuation specified at 1310 nm. This constraint eliminates the concern that the fiber will have high loss in the 1360 nm to 1460 nm band caused by OH ions absorbed during the manufacturing process. Low‑water peak characterization is critical to ensure support of applications that rely on wavelength‑division multiplexing (WDM) transmission schemes. Optional bend insensitive single‑mode optical fibers have a lower index of refraction material surrounding the fiber that reflects light back into the core and are recommended when the optical fibers or cables have to support bend radii less than 1 in (25 mm).

Single‑mode optical fiber connectors require greater mechanical precision for proper alignment and higher wavelength transmitters consume more power, so single‑mode optical fiber networks and equipment tend to cost more than multimode systems. On the other hand, only single‑mode optical fiber Ethernet networks have the extended transmission range necessary to support hyperscale data center, backbone, WAN, and MAN connections.

Desired data rate and operating range are the primary considerations when planning a single‑mode optical fiber infrastructure capable of supporting multiple generations of Ethernet applications. The single‑mode landscape is evolving, however. While single‑mode optical fiber transmission typically makes use of WDM schemes to increase throughput, some emerging short‑haul (e.g., 500 m) applications are beginning to specify more than 2‑fibers in parallel transmission schemes to provide a more economical path to achieving higher speed transmission in LAN environments.

IEEE 802.3 Single-mode Ethernet Applications

All fiber count IEEE 802.3 Ethernet single-mode applications:

| Application | No. of Fibers | Wavelength(s) | Operating Range1 | Standards Reference |

| 1000BASE-LX | 2 | 1310 nm | 2 m to 5 km | IEEE Std 802.3, Clause 38 |

| 10GBASE-ER | 2 | 1550 nm | 2 m to 40 km7 | IEEE Std 802.3, Clause 52 |

| 10GBASE-LX4 | 2 | four WDM2 | 2 m to 10 km | IEEE Std 802.3, Clause 53 |

| 10GBASE-LR | 2 | 1310 nm | 2 m to 10 km | IEEE Std 802.3, Clause 52 |

| 25GBASE-ER | 2 | 1310 nm | 2 m to 40 km7 | IEEE Std 802.3, Clause 114 |

| 25GBASE-LR | 2 | 1310 nm | 2 m to 10 km | IEEE Std 802.3, Clause 114 |

| 40GBASE-ER4 | 2 | four WDM3 | 2 m to 40 km7 | IEEE Std 802.3, Clause 87 |

| 40GBASE-FR | 2 | 1550 nm | 2 m to 2 km | IEEE Std 802.3, Clause 89 |

| 40GBASE-LR4 | 2 | four WDM3 | 2 m to 10 km | IEEE Std 802.3, Clause 87 |

| 50GBASE-ER | 2 | 1310 nm | 2 m to 40 km7 | IEEE Std 802.3, Clause 139 |

| 50GBASE-FR | 2 | 1310 nm | 2 m to 2 km | IEEE Std 802.3, Clause 139 |

| 50GBASE-LR | 2 | 1310 nm | 2 m to 10 km | IEEE Std 802.3, Clause 139 |

| 100GBASE-DR | 2 | 1310 nm | 2 m to 500 m | IEEE Std 802.3, Clause 140 |

| 100GBASE-ER4 | 2 | four WDM4 | 2 m to 40 km7 | IEEE Std 802.3, Clause 88 |

| 100GBASE-FR1 | 2 | 1310 nm | 2 m to 2 km | IEEE Std 802.3, Clause 140 |

| 100GBASE-LR1 | 2 | 1310 nm | 2 m to 10 km | IEEE Std 802.3, Clause 140 |

| 100GBASE-LR4 | 2 | four WDM4 | 2 m to 10 km | IEEE Std 802.3, Clause 88 |

| 100GBASE-ZR | 2 | DWDM6 | 2 m to 80 km | IEEE Std 802.3, Clause 154 |

| 200GBASE-DR4 | 8 | 1310 nm | 2 m to 500 m | IEEE Std 802.3, Clause 121 |

| 200GBASE-ER4 | 2 | four WDM4 | 2 m to 40 km7 | IEEE Std 802.3, Clause 122 |

| 200GBASE-FR4 | 2 | four WDM3 | 2 m to 2 km | IEEE Std 802.3, Clause 122 |

| 200GBASE-LR4 | 2 | four WDM4 | 2 m to 10 km | IEEE Std 802.3, Clause 122 |

| 400GBASE-DR4 | 8 | 1310 nm | 2 m to 500 m | IEEE Std 802.3, Clause 124 |

| 400GBASE-DR4-2 | 8 | 1310 nm | 2 m to 2 km | IEEE Std 802.3, Clause 124 |

| 400GBASE-ER8 | 2 | eight WDM5 | 2 m to 40 km7 | IEEE Std 802.3, Clause 122 |

| 400GBASE-FR4 | 2 | four WDM3 | 2 m to 2 km | IEEE Std 802.3, Clause 151 |

| 400GBASE-FR8 | 2 | eight WDM5 | 2 m to 2 km | IEEE Std 802.3, Clause 122 |

| 400GBASE-LR4-6 | 2 | four WDM3 | 2 m to 6 km | IEEE Std 802.3, Clause 151 |

| 400GBASE-LR8 | 2 | eight WDM5 | 2 m to 10 km | IEEE Std 802.3, Clause 122 |

| 800GBASE-DR8 | 16 | 1310 nm | 2 m to 500 m | IEEE Std 802.3, Clause 124 |

| 800GBASE-DR8-2 | 16 | 1310 nm | 2 m to 2 km | IEEE Std 802.3, Clause 124 |

|

1 Operating range varies according to the type of single-mode optical fiber cable used. |

||||

https://www.ieee802.org/3/bs/public/14_05/anslow_3bs_01_0514.pdf

https://www.ieee802.org/3/ba/public/may08/mellitz_01_0508.pdf

https://zhuanlan.zhihu.com/p/343643806

IEEE 802.3cd标准覆盖了50GBASE-LR/KR/SR/FR PMD子层

IEEE 802.3cd定义的50G标准有以下几种:

50GBASE-CR,通过双绞铜线屏蔽电缆的一个通道(2条同轴双绞线)传输50 Gb / s,至少达到3 m;

50GBASE-FR,在一个波长(总共2根光纤)上的50 Gb / s串行传输,可通过单模光纤电缆进行操作,最大可达2 km;

50GBASE-KR,通过电背板的一个通道传输50 Gb / s,在13.28125 GHz时总插入损耗小于30 dB;

50GBASE-LR,在一个波长(总共2根光纤)上以50 Gb / s的速率进行串行传输,可通过单模光纤电缆进行操作,并达到至少10 km;

50GBASE-SR,通过一个通道(总共2根光纤)的50 Gb / s传输速率,可通过多模光纤电缆进行操作,最大可达100 m。

400GE标准基线是由IEEE P802.3bs工作组于2015年初制定的。随后,400GE接口的多种PMD子层规格以及AUI电接口陆续提出来。

其中,IEEE 802.3bs定义了传输距离70-150m的SR16、传输距离为500m的DR4、传输距离为2km的FR8以及传输距离为10km的LR8。IEEE 802.3cm定义了传输距离为100m的SR8、SR4.2。100G Lambda MSA定义了传输距离为2km的 FR4、传输距离为10km的LR4。OIF定义了传输距离为80km的ZR。这些规格里边只有SR16仍采用NRZ的调制技术,其他规格均采用了PAM4调制。不同规格对应的电口、光口速率如图3所示。

https://www.synopsys.com/articles/ethernet-terminology.html

Utilization of the Ethernet protocol for connectivity is widespread in a broad range of things or devices around us. Historically, Ethernet has been used in local area networks (LANs) and metropolitan area networks (MANs), and now markets such as storage and automotive are adopting it due to its popularity and numerous benefits like its massive ecosystem and growing economies of scale. Integrated circuit (IC) designers are looking to integrate Ethernet functionality into their designs with an Ethernet IP solution that best serves their target applications.

However, because of its unique nomenclature, Ethernet may be a confusing standard to decipher. Serial interfaces such as PCI Express, Serial ATA (SATA) and USB have a single specification for each of their respective data rates, but Ethernet has many different specifications for the same data rate. For example, 10GBASE-ER and 10GBASE-KR are 10 Gbps Ethernet specifications but they describe different interconnect medium interfaces. As of 2016, there are at least twenty different types of one Gigabit Ethernet or Gigabit Ethernet and close to 30 different 10 Gigabit Ethernet specifications that have been defined by the IEEE 802.3 standard. As more Ethernet interfaces are deployed, it is important for designers to understand the Ethernet specification nomenclature. This article uses the Gigabit and 10 Gigabit references to define Ethernet nomenclature and help designers select the right specification for their target application.

Ethernet Data Rates

Serial data communication consists of data bits transmitting one at a time over an interconnect medium. The data rate is the number of bits transmitted per second (bits/s or bps), so if the bit time is 1 nanosecond (ns), then the data rate is 1000 million bits per second (1000 Mbps or 1 Gbps). Bit rates are typically defined as actual data rates; however, in serial transmission, the data rate is a subset of the total transmitted bits. To achieve the target data rate, line rates or physical layer gross data rate are increased. In Ethernet, to achieve the effective 1 Gbps throughput, the actual line rate is 1.25 Gbps, and in a 10 Gigabit Ethernet throughput, the line rate is 10.3125 Gbps.

Ethernet speeds are the actual data throughput rate without the data overhead, which are control bits, source address, destination address, and other non-data bits. The actual data throughput rate is also the operating rate of the Ethernet controller, which is also known as the media access control (MAC) or Ethernet MAC.

Ethernet Interconnect Mediums

Figure 1 shows the five major Ethernet interconnect mediums. An Ethernet medium may consist of only pairs of printed circuit board (PCB) traces connecting each PHY in the two ICs at each end, or it may include additional devices such as connector(s), cable (optical or copper), and transceivers.

Figure 1: Example of Ethernet interconnect mediums

The medium between two Ethernet PHYs can either be mechanical and electrical or optical. The PHYs driving each medium may have the same throughput data rate, but have different specifications, depending on the medium interface.

The mechanical and electrical medium is copper-based cables (twisted pair or twin axial) or backplanes with multiple connectors. Due to differences in cable, connector and backplane characteristics, the PHY specification for each of the interfaces may be required to be medium-dependent with different specifications.

The optical medium utilizes optical transceivers for electrical signal conversion to and from light signals and electrical signals at the two ends of a fiber optic cable. The two major optical transceiver types are single mode fiber (SMF) and multi-mode fiber (MMF), each supporting multiple different wavelengths (λ), fiber types, and cable reaches.

Ethernet Physical Layer

The IEEE 802.3 standard defines a Gigabit or 10 Gigabit PHY as a combination of three building blocks:

- Physical medium dependent (PMD)

- Physical medium attachment (PMA)

- Physical coding sublayer (PCS)

The PHY connects to the interconnect medium through the Media Dependent Interface (MDI) and connects to the MAC in the data link layer, through the media independent interface (MII), as shown in Figure 2.

Figure 2: Gigabit and 10 Gigabit Ethernet physical and data link layers

Speed-specific MII is an optional interface that provides an architectural implementation for different PHY entities, especially when the MAC is connected to an off-chip PHY. The MII interface is a chip-to-chip interface without a mechanical connector. Gigabit MAC or a repeater can be connected to a Gigabit PHY through the Gigabit Medium Independent Interface (GMII), and the 10 Gigabit MAC can connect to a 10 Gigabit PHY through the optional 10 Gigabit MII (XGMII).

Ethernet Nomenclature

Ethernet nomenclature is based on the interconnect data rate (R), modulation type (mTYPE), medium lengths (L), and a reference to the PHY’s PCS coding (C) scheme. When multiple lanes are aggregated, there is additional information on the number of aggregated lanes (n). In the absence of a reference to the number of lane(s), a single lane interface is assumed. The R mTYPE - L C n parameters used in Ethernet nomenclature are defined as:

- Data rate (R):

- 1000 → 1000 Mbps or 1 Gbps; Megabit unit is eliminated in the data rate reference

- 10G → 10 Gbps

- 10/1G → 10 Gbps downstream, 1 Gbps upstream

- Modulation type (mTYPE): BASE → Baseband

- Medium types / wavelength / reach (L):

- B → Bidirectional optics, with downstream (D) or upstream (U) asymmetric qualifiers

- C → Twin axial copper

- D → Parallel single mode (500 m)

- E → Extra-long optical wavelength λ (1510/1550 nm) / reach (40 km)

- F → Fiber (2 km)

- K → Backplane

- L → Long optical wavelength λ (~1310 nm) / reach (10 km)

- P → Passive optics, with single or multiple downstream (D) or upstream (U) asymmetric qualifiers, as well as eXternal sourced coding (X) of 4B/5B or 8B/10B

- RH → Red LED plastic optical fiber with PAM16 coding and different transmit power optics

- S → Short optical wavelength λ (850 nm) / reach (100 m)

- T → Twisted pair

- PCS coding (C):

- R → scRambled coding (64B/66B)

- X → eXternal sourced coding (4B/5B, 8B/10B)

- Number of Lanes (n):

- Blank space without lane number → defaults as 1-lane

- 4 → 4-lanes

For example, 10GBASE-KR is a 10 Gbps (10G) data rate baseband (BASE) specification, with a backplane (K) medium, using a 64B/66B (R) coding scheme, in a single lane configuration. This is purely an electrical specification that fully defines the features and characteristics of a compliant Ethernet PHY.

10GBASE-KX4 is also a 10 Gbps baseband specification for a backplane; however, it uses 8B/10B (X) coding, in an aggregated 4-lane configuration. Even though both 10GBASE-KX4 and 10GBASE-KR are 10 Gbps electrical interfaces, they describe different PHYs. A 10GBASE-KX4 PHY operates at 1/4 rate of the 10GBASE-KR across 4 lanes to achieve the same throughput.

Similarly, although 10GBASE-ER is a 10 Gbps baseband specification, it is not an electrical description like 10GBASE-KR or 10GBASE-KX4. 10GBASE-ER is an extra-long reach (E) single mode optical transceiver specification that utilizes 64B/66B (R) coding, capable of 40 km fiber optic cable reach. 10GBASE-ER mainly describes the requirements of an optical transceiver and does not provide the electrical requirements of a PHY that could drive the transceiver.

Therefore, it is important to distinguish the differences between the optical transceiver specification and electrical specifications defined in the IEEE 802.3 standard.

Summary

1000BASE-X or 10GBASE-R are names that only provide information on the data rate and the coding scheme without specifying the interface medium. By knowing how to decipher the Ethernet nomenclature by using the full name (10GBASE-KR or 10GBASE-ER), there is less ambiguity for IC designers to select the applicable medium. There may be different 10 Gigabit Ethernet specifications defined, but as long as the interconnect medium is correctly defined, the right specification can be selected for your next generation product. Synopsys’ DesignWare® Ethernet IP solutions support a broad range of Ethernet specifications and data rates.

图 152. 10GBASE-R PHY 连接到 IEEE802.3 MAC 和 RS

图 153. 10GBASE-KR PHY 连接到 IEEE802.3 MAC 和 RS

https://www.cnblogs.com/sztom/p/19084872

IEEE 802 groups

| IEEE | Description | 描述 | 状态 | 802 |

| 802.1 | Higher Layer LAN Protocols Working Group | 高层局域网协议工作组 | Active 活跃 | 1 |

| 802.2 | LLC (Logical link control) | LLC 逻辑链路控制 | Disbanded 解散 | 2 |

| 802.3 | Ethernet | 以太网 | Active 活跃 | 3 |

| 802.4 | Token bus | 令牌总线 | Disbanded 解散 | 4 |

| 802.5 | Token Ring MAC layer | 令牌环MAC层 | Disbanded 解散 | 5 |

| 802.6 | MANs (DQDB) | 城域网 (DQDB) | Disbanded 解散 | 6 |

| 802.7 | Broadband LAN using Coaxial Cable | 使用同轴电缆的宽带局域网 | Disbanded 解散 | 7 |

| 802.8 | Fiber Optic TAG | 光纤标签 | Disbanded 解散 | 8 |

| 802.9 | Integrated Services LAN (ISLAN or isoEthernet) |

综合业务局域网 (ISLAN 或 isoEthernet) |

Disbanded 解散 | 9 |

| 802.10 | Interoperable LAN Security | 可互操作局域网安全 | Disbanded 解散 | 10 |

| 802.11 | Wireless LAN (WLAN) & Mesh (Wi-Fi certification) |

无线局域网 (WLAN) 和 Mesh (Wi-Fi 认证) |

Active 活跃 | 11 |

| 802.12 | 100BaseVG | 100BaseVG | Disbanded 解散 | 12 |

| 802.13 | Unused | 未使用 | 为快速以太网开发预留 | 13 |

| 802.14 | Cable modems | 电缆调制解调器 | Disbanded 解散 | 14 |

| 802.15 | Wireless PAN | 无线个人局域网 (PAN) | Active 活跃 | 15 |

| 802.15.1 | Bluetooth certification | 蓝牙认证 | Disbanded 解散 | 15.1 |

| 802.15.2 | IEEE 802.15 and IEEE 802.11 coexistence |

IEEE 802.15 和 IEEE 802.11 共存 |

Hibernating 休眠中 | 15.2 |

| 802.15.3 | High-Rate wireless PAN (e.g., UWB, etc.) |

高速无线个人局域网 (PAN) (例如 UWB 等) |

? | 15.3 |

| 802.15.4 | Low-Rate wireless PAN (e.g., Zigbee, WirelessHART, MiWi) |

低速无线个人局域网 (PAN) (如 Zigbee, WirelessHART, MiWi) |

Active 活跃 | 15.4 |

| 802.15.5 | Mesh networking for WPAN | 用于 WPAN 的 Mesh 网络 | ? | 15.5 |

| 802.15.6 | Body area network | 体域网 | Active 活跃 | 15.6 |

| 802.15.7 | Visible light communications | 可见光通信 | ? | 15.7 |

| 802.16 | Broadband Wireless Access (WiMAX certification) |

宽带无线接入 (WiMAX 认证) |

Hibernating 休眠中 | 16 |

| 802.16.1 | Local Multipoint Distribution Service | 本地多点分布服务 | Hibernating 休眠中 | 16.1 |

| 802.16.2 | Coexistence wireless access | 共存无线接入 | Hibernating 休眠中 | 16.2 |

| 802.17 | Resilient packet ring | 弹性数据包环传输技术 | Disbanded 解散 | 17 |

| 802.18 | Radio Regulatory TAG | 无线电管制技术 | Active 活跃 | 18 |

| 802.19 | Wireless Coexistence Working Group | 无线共存工作组 | Active 活跃 | 19 |

| 802.20 | Mobile Broadband Wireless Access | 移动宽带无线接入 | Disbanded 解散 | 20 |

| 802.21 | Media Independent Handoff | 介质独立切换 | Hibernating 休眠中 | 21 |

| 802.22 | Wireless Regional Area Network | 无线区域网络 | Hibernating 休眠中 | 22 |

| 802.23 | Emergency Services Working Group | 紧急服务工作组 | Disbanded 解散 | 23 |

| 802.24 | Vertical Applications TAG | 垂直应用工作组 | Active 活跃 | 24 |

3.2 以太网标准

| 以太网标准 | 批准日期 | bps | base | Description | 标准 |

| 实验 | 1973 | 2.94Mbit/s | 同轴电缆 coaxial cable (coax) bus | 实验 | |

| Ethernet I | 1980-09 | 10Mbit/s | 粗同轴电缆 thick coax | DIX v1.0 | |

| Ethernet II | 1982-11 | 10Mbit/s | 粗同轴电缆 thick coax | DIX v2.0 | |

| 802.3-1985 | 1983-06 | 10Mbit/s | 10BASE5 | 粗同轴电缆 thick coax | 1985 |

| 802.3a | 1985-11 | 10Mbit/s | 10BASE2 | 细同轴电缆 Thin coax(又称细网或廉价网) cheapernet | 802.3a |

| 802.3b | 1985-09 | 10Mbit/s | 10BROAD36 | 802.3b | |

| 802.3c | 1985-12 | 10Mbit/s | repeater | 中继器规格 | 802.3c |

| 802.3d | 1987-12 | repeater | 光纤中继器间链路 | 802.3d | |

| 802.3e | 1987-06 | 1Mbit/s | 1BASE5 | 双绞线 250-500米 StarLAN | 802.3e |

| 802.3h | 1990-09 | 10Mbit/s | DTEs | 802.3h | |

| 802.3i | 1990-09 | 10 Mbit/s | 10BASE-T | 双绞线 Twisted pair (100m) | 802.3i |

| 802.3j | 1992-09 | 10 Mbit/s | 10BASE-F | 光纤 optical fiber | 802.3j |

| 802.3k | 1992-09 | 10 Mbit/s | repeater | 中继器 repeaters | 802.3k |

| 802.3m | 1995-09 | Maintenance 维护 | 802.3m | ||

| 802.3n | 1995-09 | Maintenance 维护 | 802.3n | ||

| 802.3q | 1993-06 | GDMO (ISO/IEC 10165-4) | 802.3q | ||

| 802.3r | 1996-07 | 10Mbit/s | 10BASE5 | 介质连接单元 PICS | 802.3r |

| 802.3s | 1995-09 | Maintenance 维护 | 802.3s | ||

| 802.3t | 1995-06 | 10 Mbit/s | 10BASE-T | 120 Ω 资料性附件 | 802.3t |

| 802.3u | 1995-06 | 100 Mbit/s | 100BASE-TX/T4/FX | Autonegotiation 具有自动协商功能 (100m) | 802.3u |

| 802.3v | 1995-12 | 10 Mbit/s | 10BASE-T | 150 Ω 资料附件 | 802.3v |

| 802.3x | 1997-03 | 全双工和流量控制 (Full duplex, flow control) | 802.3x | ||

| 802.3y | 1997-03 | 100 Mbit/s | 100BASE-T2 | 双绞线 | 802.3y |

| 802.3z | 1998-06 | 1 Gbit/s | 1000BASE-X | 光纤以太网 5000m | 802.3z |

| 802.3-1998 | 1998-06 | (802.3aa)对基础标准的修订 | 802.3aa | ||

| 802.3ab | 1999-06 | 1 Gbit/s | 1000BASE-T | 双绞线 | 802.3ab |

| 802.3ac | 1998-09 | 最大帧大小扩展至 1522 字节... | 802.3ac | ||

| 802.3ad | 2000-03 | Link aggregation | 并行链路的链路聚合,现已迁移至IEEE 802.1AX | 802.3ad | |

| 802.3-2002 | 2002-01 | (802.3ag)对基础标准的修订 | 802.3ag | ||

| 802.3ae | 2002-06 | 10 Gbit/s | 10GBASE-… | 10 Gigabit Ethernet over fiber: 10GBASE-SR, -LR, -ER, -SW, -LW, -EW |

802.3ae |

| 802.3af | 2003-06 | Power over | 以太网供电(15.4 W) | 802.3af | |

| 802.3ah | 2004-06 | Ethernet in the first mile | 802.3ah | ||

| 802.3ak | 2004-02 | 10 Gbit/s | 10GBASE-CX4 | 双轴电缆 | 802.3ak |

| 802.3-2005 | 2005-06 | (802.3am)对基础标准的修订 | 802.3am | ||

| 802.3an | 2006-06 | 10 Gbit/s | 10GBASE-T | 非屏蔽双绞线 (UTP) | 802.3an |

| 802.3ap | 2007-03 | 10 Gbit/s | Backplane | PCB | 802.3ap |

| 802.3aq | 2006-09 | 10 Gbit/s | 10GBASE-LRM | 多模光纤 | 802.3aq |

| P802.3ar | canceled | 拥塞管理(已撤回) | P802.3ar | ||

| 802.3as | 2006-09 | 框架扩展 | 802.3as | ||

| 802.3at | 2009-09 | Power over | 以太网供电增强功能(25.5 W) | 802.3at | |

| 802.3au | 2006-06 | Power over | 以太网供电隔离要求(802.3-2005/Cor 1) | 802.3au | |

| 802.3av | 2009-09 | 10 Gbit/s | EPON | 10 Gbit/s EPON | 802.3av |

| 802.3aw | 2007-06 | 10 Gbit/s | 10GBASE-T | 修复了 10GBASE-T 出版物(802.3-2005/Cor 2) | 802.3aw |

| 802.3ax | 2008-11 | Link aggregation | 链路聚合 – 已迁移至802.1AX并获批准 | 802.3ax | |

| 802.3-2008 | 2008-12 | (802.3ay)基础标准的修订版 | 802.3ay | ||

| 802.3az | 2010-09 | 节能以太网 Energy-Efficient | 802.3az | ||

| 802.3ba | 2010-06 | 100 Gbit/s | backplane | 40 Gbit/s 和 100 Gbit/s 以太网。 | 802.3ba |

| 802.3-2008 | 2009-12 | 10 Gbit/s | (802.3bb)/Cor 1增加暂停反应延迟时间… | 802.3bb | |

| 802.3bc | 2009-09 | 将802.1AB (LLDP) 附件 F 中指定的以太网相关 TLV(类型、长度、值)移动并更新到 802.3 | 802.3bc | ||

| 802.3bd | 2011-06 | 基于优先级的流量控制... | 802.3bd | ||

| 802.3.1 | 2011-05 | (802.3be) 以太网 MIB 定义。 | 802.3be | ||

| 802.3bf | 2011-05 | 提供对某些数据包传输和接收启动时间的准确指示,以支持 IEEE P802.1AS | 802.3bf | ||

| 802.3bg | 2011-03 | 40 Gbit/s | 提供 40 Gbit/s PMD… | 802.3bg | |

| 802.3-2012 | 2012-08 | (802.3bh) 基本标准的修订版 | 802.3bh | ||

| 802.3bj | 2014-06 | 100 Gbit/s | backplane | 四通道 100 Gbit/s 背板 PHY… | 802.3bj |

| 802.3bk | 2013-08 | EPON | 支持 PX30、PX40、PRX40 和 PR40 PMD 的扩展功率预算等级。 | 802.3bk | |

| 802.3bm | 2015-02 | 100 Gbit/s | 100G/40G以太网光纤 | 802.3bm | |

| 802.3bn | 2016-09 | 10 Gbit/s | 10G-EPON 10GPASS-XR |

10G-EPON和 10GPASS-XR,同轴电缆无源光网络 | 802.3bn |

| 802.3bp | 2016-06 | 1 Gbit/s | 1000BASE-T1 Automotive |

适用于汽车和工业环境的单条双绞线千兆以太网 | 802.3bp |

| 802.3bq | 2016-06 | 40 Gbit/s | 25GBASE-T 40GBASE-T |

适用于四对平衡双绞线电缆,距离超过 30 米,带有两个连接器 | 802.3bq |

| 802.3br | 2016-06 | 穿插快速交通规范及管理参数 | 802.3br | ||

| 802.3bs | 2017-12 | 400 Gbit/s | 200GbE 400GbE |

单模光纤上200GbE (200 Gbit/s), 光学物理介质上400GbE (400 Gbit/s) |

802.3bs |

| 802.3bt | 2018-09 | 10GBASE-T | Power over | 第三代以太网供电,使用四对平衡双绞线(4PPoE),功率高达 100 W,包括 10GBASE-T. | 802.3bt |

| 802.3bu | 2016-12 | 100 Mbit/s | Power over | 用于单双绞线以太网 (100BASE-T1) 的数据线供电 (PoDL) | 802.3bu |

| 802.3bv | 2017-02 | 1 Gbit/s | 塑料光纤(POF)千兆以太网 plastic optical fiber | 802.3bv | |

| 802.3bw | 2015-10 | 100 Mbit/s | 100BASE-T1 Automotive |

单根双绞线 100 Mbit/s 以太网,适用于汽车应用 | 802.3bw |

| 802.3-2015 | 2015-09 | 802.3bx – 802.3 标准的新合并修订版 | 802.3bx | ||

| 802.3by | 2016-06 | 25 Gbit/s | backplane | 光纤,双轴电缆和背板25千兆以太网 | 802.3by |

| 802.3bz | 2016-09 | 5 Gbit/s | 2.5GBASE-T 5GBASE-T |

通过Cat-5e/Cat-6双绞线电缆实现 2.5 Gigabit/s 和 5 Gigabit/s 以太网 | 802.3bz |

| 802.3ca | 2020-06 | 50 Gbit/s | 25G-EPON 50G-EPON |

以太网无源光网络上行/上行速率分别为 25/10、25/25、50/10、50/25、50/50 Gbit/s | 802.3ca |

| 802.3cb | 2018-09 | 5 Gbit/s | backplane | 通过背板以 2.5 Gbit/s 和 5 Gbit/s 的速度运行 | 802.3cb |

| 802.3cc | 2017-12 | 25 Gbit/s | 单模光纤传输速率为 25 Gbit/s | 802.3cc | |

| 802.3cd | 2018-12 | 200 Gbit/s | 50 Gbit/s 和物理层的媒体访问控制参数以及 50、100 和 200 Gbit/s 操作的管理参数 | 802.3cd | |

| 802.3ce | 2017-03 | 多通道时间戳 | 802.3ce | ||

| 802.3.2-2019 | 2019-03 | 802.3cf,YANG 数据模型定义 | 802.3cf | ||

| 802.3cg | 2019-11 | 10 Mbit/s | 10BASE-T1L 10BASE-T1S |

10 Mbit/s 单双绞线以太网 | 802.3cg |

| 802.3ch | 2020-06 | 10 Gbit/s | MultiGigBASE-T1 Automotive |

汽车以太网(2.5、5、10 Gbit/s),传输距离超过 15 米,可选 PoDL | 802.3ch |

| 802.3-2018 | 2018-08 | 802.3cj – 802.3-2015 维护 | 802.3cj | ||

| 802.3ck | 2022-09 | 400 Gbit/s | 使用 100 Gbit/s 通道的 100、200 和 400 Gbit/s 以太网 | 802.3ck | |

| 802.3cm | 2020-01 | 400 Gbit/s | 通过多模光纤(四对和八对,100 米)传输 400 Gbit/s | 802.3cm | |

| 802.3cn | 2019-11 | 400 Gbit/s | 通过单模光纤和DWDM实现: 50 Gbit/s (40km), 100Gbit/s (80km), 200Gbit/s (four λ, 40km), 400Gbit/s (eight λ, 40km and single λ, 80km over DWDM) |

802.3cn | |

| 802.3cp | 2021-06 | 50 Gbit/s | 10/25/50 Gbit/s 单链光纤接入,传输距离至少为 10/20/40 km | 802.3cp | |

| 802.3cq | 2020-01 | Power over | 两对以太网供电(维护) | 802.3cq | |

| 802.3cr | 2021-02 | 隔离(维护) Isolation (maintenance) | 802.3cr | ||

| 802.3cs | 2022-09 | 10 Gbit/s | Super-PON | “超级PON”——覆盖范围扩大,10 Gbit/s 光纤接入, 覆盖距离至少为 50 km,每波长对分光比为 1:64,共 16 个波长对 |

802.3cs |

| 802.3ct | 2021-06 | 100 Gbit/s | 100 Gbit/s DWDM 系统(采用相干调制,传输距离可达 80 公里) | 802.3ct | |

| 802.3cu | 2021-02 | 400 Gbit/s | 使用 100 Gbit/s 通道,通过 SMF 传输 100 Gbit/s 和 400 Gbit/s | 802.3cu | |

| 802.3cv | 2021-05 | Power over | 以太网供电维护 | 802.3cv | |

| 802.3cw | canceled | 400 Gbit/s | 400 Gbit/s DWDM 系统, 已撤回 | 802.3cw | |

| 802.3cx | 2023-03 | 提高PTP时间戳准确性 | 802.3cx | ||

| 802.3cy | 2023-06 | 25 Gbit/s | MultiGigBASE-T1 Automotive |

25 Gbit/s 电动汽车以太网 | 802.3cy |

| 802.3cz | 2023-03 | Automotive | 多千兆位光学汽车以太网 | 802.3cz | |

| 802.3da | (TBD) | 10 Mbit/s | 10BASE-T1S | 在单平衡对多点网段上以 10 Mb/s 的速度运行,长度可扩展至 50 米 - 计划于 2025 年中期实现 | 802.3da |

| 802.3db | 2022-09 | 400 Gbit/s | 采用 100 Gbit/s 信令,在光纤上实现 100 Gbit/s、200 Gbit/s 和 400 Gbit/s 的运行 | 802.3db | |

| 802.3-2022 | 2022-07 | 802.3dc – 802.3-2018 维护,纳入近期修订 bt/ca/cb/cd/cg/ch/cm/cn/cp/cq/cr/ct/cu/cv | 802.3dc | ||

| 802.3dd | 2022-06 | Power over | 单对以太网数据线供电维护 | 802.3dd | |

| 802.3de | 2022-09 | 点对点单对以太网的时间同步 | 802.3de | ||

| 802.3df | 2024-02 | 800 Gbit/s | 使用 100 Gbit/s 通道的 200 Gb/s、400 Gb/s 和 800 Gb/s | 802.3df | |

| 802.3dg | (TBD) | 100 Mbit/s | 100BASE-T1L | (单对 100 Mbps,长度扩展至 500 米) 计划于 2025 年中期推出 | 802.3dg |

| 802.3dh | canceled | Automotive | 基于塑料光纤的每秒数千兆位汽车以太网 | 802.3dh | |

| 802.3dj | (TBD) | 1.6 Tbit/s | Ultra Ethernet | 200 Gb/s、400 Gb/s、800 Gb/s 和 1.6 Tbit/s(使用 200 Gbit/s 通道) 计划于 2026 年春季推出。 | 802.3dj |

| 802.3dk | (TBD) | 50 Gbit/s | 大于50 Gbit/s双向光接入 | 802.3dk | |

| 802.3dm | (TBD) | Automotive | 非对称电气汽车以太网 | 802.3dm | |

| 802.3dn | 2024-09 | Automotive | 802.3-2022/Cor 1 多千兆汽车 MDI 回波损耗 | 802.3dn |

https://www.cse.wustl.edu/~jain/cse570-19/ftp/backplne.pdf

10GBASE-KX4 and 10GBASE-KR correspond to the IEEE 802.3ap standard published in 2007

https://www.ieee802.org/3/ck/public/19_01/lusted_3ck_01_0119.pdf

Nomenclature

https://download.tek.com/document/Tek%20PAM4%20Solution%20Update-2018-05-23_0.pdf

https://harrisburg.psu.edu/files/pdf/16861/2019/05/06/tektronix_penn_state_si_april_12_2019.pdf

https://cdrdv2-public.intel.com/667071/an835-ch-683852-667071.pdf

https://en.wikipedia.org/wiki/25_Gigabit_Ethernet

The IEEE P802.3cd [2] standard defines a Physical Coding Sublayer (PCS) in Clause 133 which after encoding gives a data rate of 51.5625 Gbit/s. 802.3cd also defines an RS-FEC for forward error correction in Clause 134 which after FEC encoding gives a data rate of 53.125 Gbit/s. It is not possible to transmit 53.125 Gbit/s over an electrical interface while maintaining suitable signal integrity so four-level pulse-amplitude modulation (PAM4) is used to map pairs of bits into a single symbol. This leads to an overall baud rate of 26.5625 GBd for 50 Gbit/s per lane Ethernet. PAM4 encoding for 50G Ethernet is defined in Clause 135 of the 802.3 standard

https://www.ieee802.org/3/ca/public/meeting_archive/2019/03/kramer_3ca_10_0319.pdf

https://www.intel.com/content/www/us/en/docs/programmable/683805/current/types-of-rs-fec.html

Table 5. Types of RS-FEC

| RS-FEC | Parameter Name | NRZ PHY | PAM4 PHY | |

|---|---|---|---|---|

| FEC encoding | — | RS (528, 514, t=7, m=10) | RS (544, 514, t=15, m=10) | |

| Total symbols | n | 528 | 544 | |

| Message symbols | k | 514 | 514 | |

| Parity symbols | n-k | 14 | 30 | |

| Bits per symbol | m | 10 | 10 | |

| Correctable symbols | t | 7 | 15 | |

| Coding gain | DFE | — | 4.9 dB @ 1E-15 | 5.4 dB @ 1E-15 |

| Random | — | 5.3 dB @ 1E-12 | 6.5 dB @ 1E-12 | |

https://www.cnblogs.com/xena/p/18082650

对于802.3ck中描述的100Gbps以太网,在添加里德-所罗门前向纠错(RS-FEC)之前,64b/66b编码被转码为256b/257b块。这样做是为了减少块编码所使用的开销,以便为更强大的PAM4 FEC留下更多的开销。256b/256b转码将四个64b/66b块组合在一起,去掉两个比特的头,在整个256比特块上添加一个单比特头。

一个FEC块由n个FEC符号组成,其中k个FEC符号是实际数据,其余(n-k)个FEC符号是代码和冗余位–也被称为奇偶校验位。因此,一个FEC的特点是有序的一对(n,k)。

一个给定的FEC可以纠正的错误数量取决于实际的实现。对于802.3ck 100Gbps以太网,使用了Reed-Solomon(RS)(544,514,t=15)FEC,FEC符号为10比特宽。这意味着,每块514个数据FEC符号要增加30个奇偶校验FEC符号。t=15指的是这个FEC可以纠正多达15个FEC符号的错误,每个符号包含多达10位的错误。

https://www.xilinx.com/publications/events/designcon/2016/slides-pam4signalingfor56gserial-zhang-designcon.pdf 看起来很专业 ,没仔细看

https://www.tek.com/en/documents/whitepaper/optical-bandwidth-requirements-nrz-and-pam4-signaling

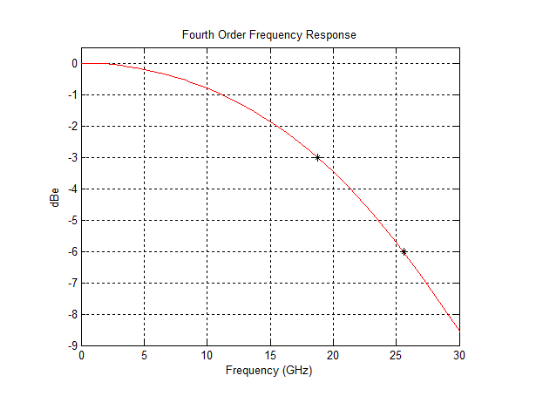

Figure 1. Graph of an ORR (Optical Reference Receiver) at 25Gbps. Note that the -3dBe point is at 18.75 GHz and that the -6dBe (-3dBo) point is at 1.025 * 25 GHz = 25.625 GHz.

https://www.ieee802.org/3/bm/public/sep12/petrilla_02a_0912_optx.pdf

100G SR4 & RS(528, 514, 7, 10) FEC

IEEE standards

The IEEE 802.3 standard defines KR-FEC and KP-FEC, where “K” denotes the FEC used on backplanes. KR-FEC is used for NRZ signals, and KP-FEC is used for PAM-4 signals. KR1-FEC translates 4x25G NRZ electrical signals into a 100GBASE-KR1 encoded signal. KR-FEC is denoted as RS(528, 514). Here, the RS encoding starts with a 514-symbol data field (k), where each symbol consists of 10 bits and appends 14 parity symbols to form a 528-symbol encoded codeword (n).

KP-FEC can be applied to both 100G (KP1) or 400G (KP4) signals. KP1-FEC is applied to PAM-4 signals to group two 50-Gbit PAM-4 electrical signals into a single 100GBASE-KP1 encoded signal. KP1-FEC translates 30 parity symbols, in which each symbol consists of 10 bits. This parity string gets appended to a 514-symbol data field (k) to form a 544-symbol encoded codeword (n), so KP1-FEC is denoted as RS(544,514).

https://www.ieee802.org/3/bj/public/sep11/slavick_01_0911.pdf

https://blog.csdn.net/icxiaoge/article/details/119983003

https://static.fmad.io/blog-10g-ethernet-layer1-64b-66b.html

Currently the serial links of standard Ethernet are fixed at 10.3125Ghz and 25.78125Ghz and it will probably stay that way for at least the next 5 years, until 400G ethernet starts to gain wide spread adoption.

But whats with these funky frequency rates ? 10G ethernet should be exactly 10.000GHz, and not 10.3125Ghz? Well, that's kind of true, but kind of not. 10G ethernet is 10Ghz of serialized data payload which does not include the control payload bandwidth. If we do the math of 2b (of control) / 64b (of data) = 66b encoding = 0.03125 a number that looks quite familiar. It means the encoding overhead is 3.125% of the data rate, which also means if we run the serial link at exactly 10.00Ghz then 3.125% of that 10Ghz bandwidth will be dedicated to control logic leaving 10Ghz - 0.3125Ghz = 9.6875Ghz remains for data. That of course means 10G ethernet is no longer 10Gbit of payload so.. what did the designers do ? what all modders do, they overclocked that shit! Now its hard to imagine an uber crazy nitro-watercooled network 100Ghz transceiver's gaining much traction in the market, but what did gain acceptance is a slight 3.125% overclocking of the serial link to make the final link speed 10.3125Ghz with 0.3125Ghz for control and a full 10.0Ghz of bandwidth for data

https://www.ieee802.org/3/bs/baseline_3bs_0715.pdf IEEE P802.3bs Baseline Summary

http://www.iccsz.com/site/cn/News/2023/01/10/20230110034059280187.htm

SFP56是一种小型化外形尺寸可插拔以太网收发器。SFP56在50 Gb/s有效载荷之上有具备256b/257b编码开销,可以将信号的物理线路速率提高到26.5625 Gbaud。

https://blog.csdn.net/weixin_45365488/article/details/132559791

https://blog.csdn.net/pangzi_sh/article/details/122717208

https://nateurope.com/wp-content/uploads/2023/04/NAT-MCH-HUB-E-40GX_TechRef.pdf

CPU and associated Memory

The NAT-MCH-HUB-E-40GX is equipped with a Marvell 88F3720 CPU with dual ARM A53 core. It has 4GB eMMC available, as well as 2GB DRAM DDR4-1600, 16 bit wide. For N.A.T. internal use, also a MicroSD-Card slot is mounted.

Ethernet Switch

The NAT-MCH-HUB-E-40GX features a Marvell 98EX5520 “Armstrong-LP”. The Switch Port assignment between the Ethernet switch and the PIPEs is described in chapter 5.3 Port Assignment.

Port Extenders (PIPE)

For providing XAUI functionality, the NAT-MCH-HUB-E-40GX owns four Marvell 98PX1012 passive intelligent port extenders (PIPE) “Prestera-LP”. The Switch Port assignment of the PIPEs is described in chapter 5.3 Port Assignment

FPGA

The NAT-MCH-HUB-E-40GX features a Lattice MACHXO2-FPGA for LED control.

Microcontroller

An Atmel ATmega128 microcontroller works as IPMI controller

SerDes modes supported by the Ethernet switch are listed below.

SerDes modes supported by the PIPEs are listed below

https://www.synopsys.com/dw/ipdir.php?ds=dwc_enterprise_ether_pcs

The IP supports the following link types through the PMA layer:

- 10GBASE-R

- 25GBASE-CR

- 25GBASE-CR-S

- 25GBASE-KR

- 25GBASE-KR-S

- 40GBASE-R

- 40GBASE-KR4

- 50GBASE-CR2

- 50GBASE-KR2

- 100GBASE-CR4

- 100GBASE-KR4

https://www.intel.com/content/www/us/en/docs/programmable/683805/current/100gbase-kr4.html 这个100GBASE-KR4选用的NRZ调制而不是PAM4? 留个疑问

Figure 16. 100GBASE-KR4 OSI Model

AN = Auto-Negotation

CGMII = 100 Gb/s Media Independent Interface

LLC = Logical Link Control

MAC = Media Access Control

MDI = Medium Dependent Interface

PCS = Physical Coding Sublayer

PHY = Physical Layer Device

PMA = Physical Medium Attachment

PMD = Physical Medium Dependent

RS-FEC = Reed-Solomon Forward Error Correction

https://www.intel.com/content/www/us/en/docs/programmable/683023/23-2/overview-16832.html 100Gbase-KR1/2使用PAM4,100Gbase-KR4却使用NRZ?

able 3. Supported Ethernet Protocols

| Ethernet Channel | Protocol | Number of Lanes and Line Rate |

|---|---|---|

| 10GE | 10GBASE-KR | 1x10.3125 Gbps NRZ lane for Copper Backplane |

| 10GBASE-CR | 1x10.3125 Gbps NRZ lane for Direct Attach Copper Cable | |

| 10GBASE-LR | 1x10.3125 Gbps NRZ lane for optical fiber | |

| 25GE | 25GBASE-KR | 1x25.78125 Gbps NRZ lane for Copper Backplane |

| 25GBASE-CR | 1x25.78125 Gbps NRZ lane for Direct Attach Copper Cable | |

| 25GBASE-R | 1x25.78125 Gbps NRZ lane based on the 25G Ethernet Consortium specification | |

| 25GAUI-1 | 1x25.78125 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| 40GE | 40GBASE-KR4 | 4x10.3125 Gbps NRZ lanes for Copper Backplane |

| 40GBASE-CR4 | 4x10.3125 Gbps NRZ lanes for Direct Attach Copper Cable | |

| 40GBASE-SR4 | 4x10.3125 Gbps NRZ lanes for optical fiber | |

| 50GE | 50GBASE-KR1 | 1x53.125 Gbps NRZ lane for Copper Backplane |

| 50GBASE-CR1 | 1x53.125 Gbps NRZ lane for Direct Attach Copper Cable | |

| 50GBASE-KR2 | 2x25.78125 Gbps NRZ lane for Copper Backplane | |

| 50GBASE-CR2 | 2x25.78125 Gbps NRZ lane for Direct Attach Copper Cable | |

| 50GAUI-1 | 1x53.125 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| 50GAUI-2 | 2x25.78125 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| 100GE | 100GBASE-KR1 | 1x106.25 Gbps PAM4 lanes for Copper Backplane |

| 100GBASE-CR1 | 1x106.25 Gbps PAM4 lanes for Direct Attach Copper Cable | |

| 100GBASE-KR2 | 2x53.125 Gbps PAM4 lanes for Copper Backplane | |

| 100GBASE-CR2 | 2x53.125 Gbps PAM4 lanes for Direct Attach Copper Cable | |

| 100GBASE-KR4 | 4x25.78125 Gbps Non-Return-to-Zero (NRZ) lanes for Copper Backplane | |

| 100GBASE-CR4 | 4x25.78125 Gbps NRZ lanes for Direct Attach Copper Cable | |

| 100GAUI-1 | 1x106.25 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| 100GAUI-2 | 2x53.125 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| 100GAUI-4 | 4x26.5625 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| CAUI-2 | 2x53.125 Gbps PAM4 lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| CAUI-4 | 4x25.78125 Gbps NRZ lanes for Low Loss Links: Chip-to-Chip, Chip-to-Module | |

| 200GE | 200GBASE-KR2 | 2x106.25 Gbps PAM4 lanes for Copper Backplane |

| 200GBASE-CR2 | 2x106.25 Gbps PAM4 lanes for Direct Attach Copper Cable | |

| 200GBASE-KR4 | 4x53.125 Gbps PAM4 lanes for Copper Backplane | |

| 200GBASE-CR4 | 4x53.125 Gbps PAM4 lanes for Direct Attach Copper Cable | |

| 200GAUI-2 | 2x106.25 Gbps PAM4 for Low Loss Links: Chip-to-Chip or Chip-to-Module | |

| 200GAUI-4 | 4x53.125 Gbps PAM4 for Low Loss Links: Chip-to-Chip or Chip-to-Module | |

| 200GAUI-8 | 8x26.5265 Gbps PAM4 for Low Loss Links: Chip-to-Chip or Chip-to-Module | |

| 400GE | 400GBASE-KR4 | 4x106.25 Gbps PAM4 lanes for Copper Backplane |

| 400GBASE-CR4 | 4x106.25 Gbps PAM4 lanes for Direct Attach Copper Cable | |

| 400GAUI-4 | 4x106.25 Gbps PAM4 lanes for Low Loss Links: Chip-to-Chip or Chip-to-Module | |

| 400GBASE-KR8 | 8x53.125 Gbps PAM4 lanes for Copper Backplane (Ethernet Consortium) | |

| 400GBASE-CR8 | 8x53.125 Gbps PAM4 lanes for Direct Attach Copper Cable | |

| 400GAUI-8 | 8x53.125 Gbps PAM4 lanes for Low Loss Links: Chip-to-Chip or Chip-to-Module |

https://www.eet-china.com/mp/a371970.html

摸透以太网的PHY、MAC及其通信接口

本文主要介绍以太网的MAC(Media Access Control,即媒体访问控制子层协议)和PHY(物理层)之间的MII(Media Independent Interface ,媒体独立接口),以及MII的各种衍生版本——GMII、SGMII、RMII、RGMII等。

简介

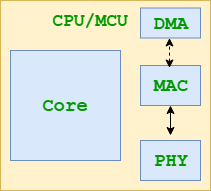

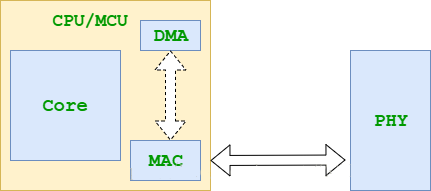

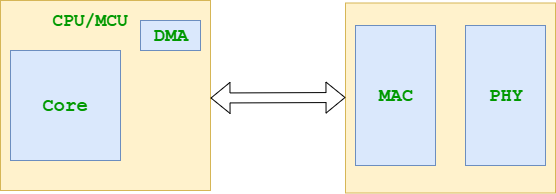

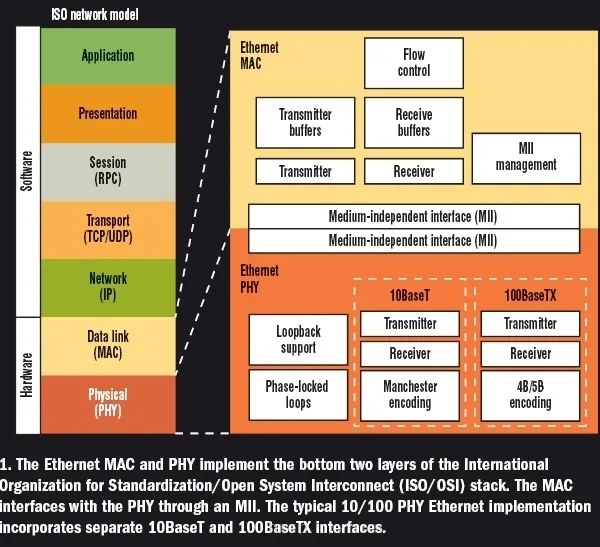

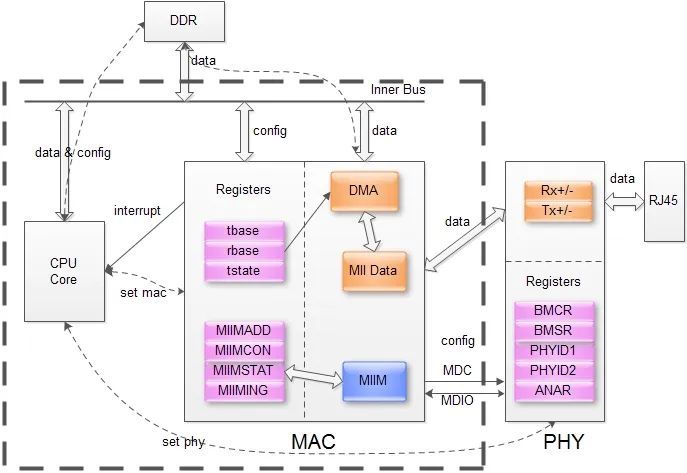

从硬件的角度看,以太网接口电路主要由MAC(Media Access Control)控制器和物理层接口PHY(Physical Layer,PHY)两大部分构成。如下图所示:

DMA控制器通常属于CPU的一部分,用虚线放在这里是为了表示DMA控制器可能会参与到网口数据传输中。

但是,在实际的设计中,以上三部分并不一定独立分开的。由于,PHY整合了大量模拟硬件,而MAC是典型的全数字器件。考虑到芯片面积及模拟/数字混合架构的原因,通常,将MAC集成进微控制器而将PHY留在片外。更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合。可分为下列几种类型:

CPU集成MAC与PHY。目前来说并不多见

CPU集成MAC,PHY采用独立芯片。比较常见

CPU不集成MAC与PHY,MAC与PHY采用集成芯片。比较常见

MAC及PHY工作在OSI七层模型的数据链路层和物理层。具体如下:

什么是MAC

MAC(Media Access Control)即媒体访问控制子层协议。

该部分有两个概念:MAC可以是一个硬件控制器 及 MAC通信以协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。MAC硬件大约就是下面的样子了:

在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层。

在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC(逻辑链路控制)层。该层协议是以太网MAC由IEEE-802. 3以太网标准定义。

以太网数据链路层其实包含MAC(介质访问控制)子层和LLC(逻辑链路控制)子层。一块以太网卡MAC芯片的作用不但要实现MAC子层和LLC子层的功能,还要提供符合规范的PCI界面以实现和主机的数据交换。

MAC从PCI总线收到IP数据包(或者其他网络层协议的数据包)后,将之拆分并重新打包成最大1518Byte、最小64Byte的帧。

这个帧里面包括了目标MAC地址、自己的源MAC地址和数据包里面的协议类型(比如IP数据包的类型用80表示,最后还有一个DWORD(4Byte)的CRC码。

可是目标的MAC地址是哪里来的呢?

这牵扯到一个ARP协议(介乎于网络层和数据链路层的一个协议)。第一次传送某个目的IP地址的数据的时候,先会发出一个ARP包,其MAC的目标地址是广播地址,里面说到:“谁是xxx.xxx.xxx.xxx这个IP地址的主人?”

因为是广播包,所有这个局域网的主机都收到了这个ARP请求。收到请求的主机将这个IP地址和自己的相比较,如果不相同就不予理会,如果相同就发出ARP响应包。

这个IP地址的主机收到这个ARP请求包后回复的ARP响应里说到:“我是这个IP地址的主人”。这个包里面就包括了他的MAC地址。以后的给这个IP地址的帧的目标MAC地址就被确定了。(其它的协议如IPX/SPX也有相应的协议完成这些操作)。

IP地址和MAC地址之间的关联关系保存在主机系统里面,叫做ARP表。由驱动程序和操作系统完成。

在Microsoft的系统里面可以用arp-a 的命令查看ARP表。收到数据帧的时候也是一样,做完CRC校验以后,如果没有CRC效验错误,就把帧头去掉,把数据包拿出来通过标准的接口传递给驱动和上层的协议栈。最终正确的达到我们的应用程序。

还有一些控制帧,例如流控帧也需要MAC直接识别并执行相应的行为。

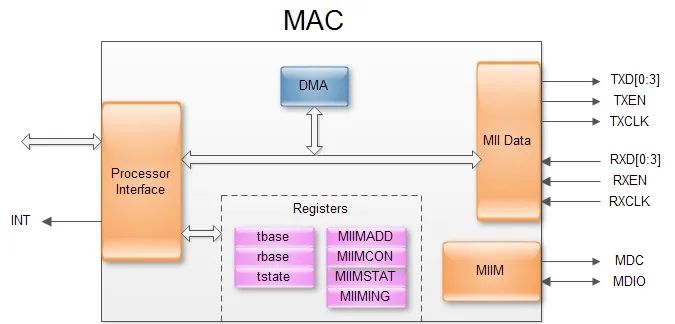

以太网MAC芯片的一端接计算机PCI总线,另外一端就接到PHY芯片上,它们之间是通过MII接口链接的。

一个MAC的结构图如下图所示:

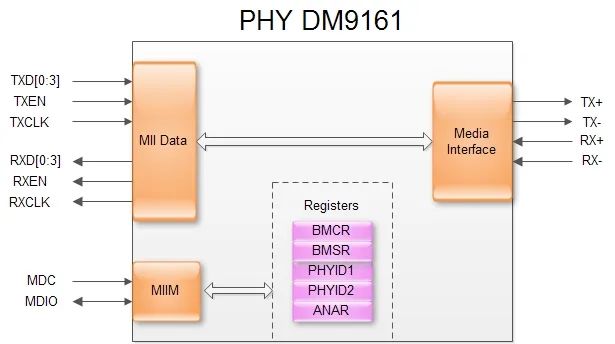

什么是PHY

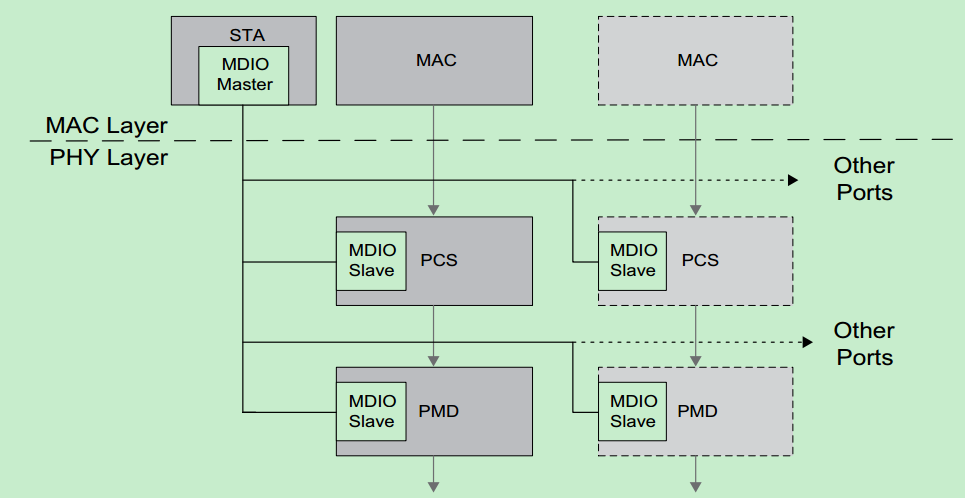

PHY((Physical Layer,PHY))是IEEE802.3中定义的一个标准模块,STA(station management entity,管理实体,一般为MAC或CPU)通过SMI(Serial Manage Interface)对PHY的行为、状态进行管理和控制,而具体管理和控制动作是通过读写PHY内部的寄存器实现的。一个PHY的基本结构如下图:

PHY是物理接口收发器,它实现OSI模型的物理层。

IEEE-802.3标准定义了以太网PHY。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。

注:PHY寄存器在IEEE802.3标准的 22.2.4 Management functions 节有介绍,但不涉及所有的寄存器,个别寄存器需要到其它章节中看,当然,文档里面也提到该在哪里找到哪个寄存器。

什么是MII

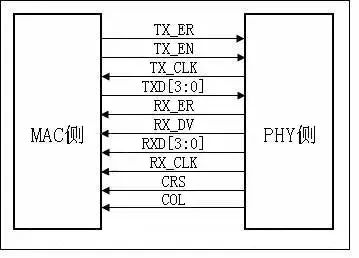

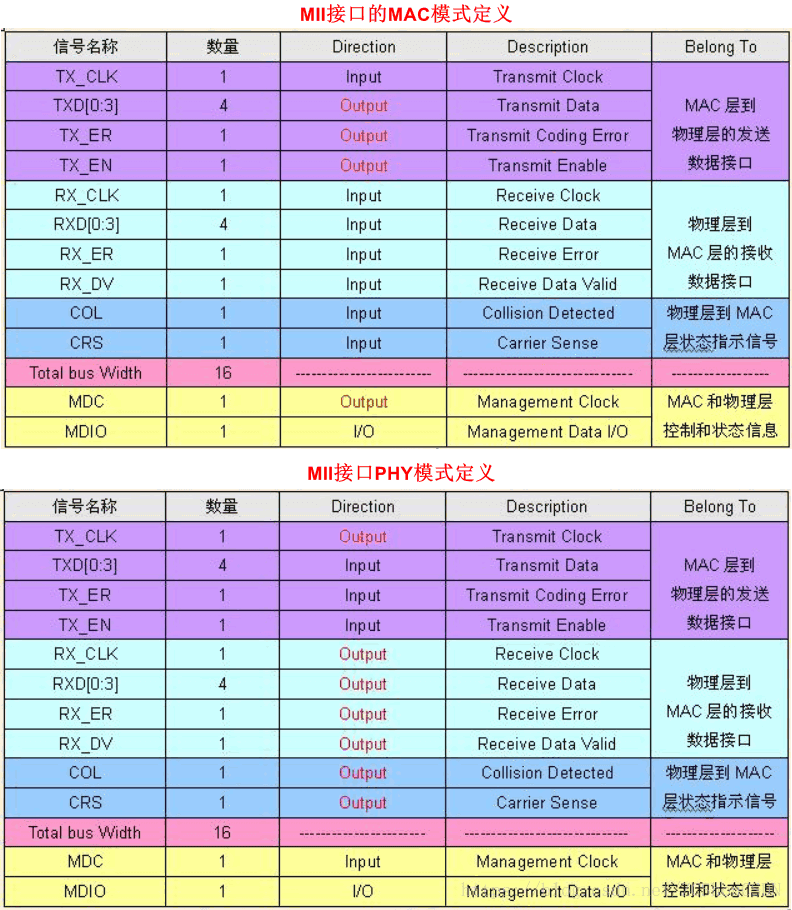

MII(Media Independent Interface)即媒体独立接口,MII 接口是 MAC 与 PHY 连接的标准接口。它是 IEEE-802.3 定义的以太网行业标准。MII 接口提供了 MAC 与 PHY 之间、PHY 与 STA(Station Management)之间的互联技术,该接口支持 10Mb/s 与 100Mb/s 的数据传输速率,数据传输的位宽为 4 位。MII 接口如下图所示:

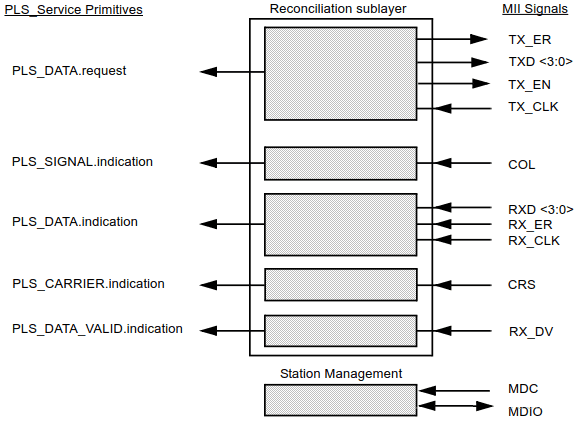

“媒体独立” 表明在不对 MAC 硬件重新设计或替换的情况下,任何类型的 PHY 设备都可以正常工作。802.3 协议最多支持 32 个 PHY,但有一定的限制:要符合协议要求的 connector 特性。此外,提到 MII,就有可能涉及到 RS,PLS,STA 等名词术语,下面讲一下他们之间对应的关系。所谓 RS 即 Reconciliation sublayer,它的主要功能主要是提供一种 MII 和 MAC/PLS 之间的信号映射机制。它们(RS 与 MII)之间的关系如下图:

MII的Management Interface是与STA(Station Management)相连的。注:关于本节,具体可参考IEEE以太网标准802.3的22.3 Signal timing characteristics节,其中包含时钟信号等更详细内容。MII接口主要包括四个部分。一是从MAC层到PHY层的发送数据接口,二是从PHY层到MAC层的接收数据接口,三是从PHY层到MAC层的状态指示信号,四是MAC层和PHY层之间传送控制和状态信息的MDIO接口。

MII 包括一个数据接口,以及一个 MAC 和 PHY 之间的管理接口:

- 数据接口: 包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII 数据接口总共需要 16 个信号,包括

- TX_ER(transmit coding error): TX_ER 同步于 TX_CLK,在数据传输过程中,如果 TX_ER 有效超过一个时钟周期,并且此时TX_EN 是有效的,则数据通道中传输的数据是无效的,没用的。注:当 TX_ER 有效并不影响工作在 10Mb/s 的 PHY 或者 TX_EN 无效时的数据传输。在 MII 接口的连线中,如果 TX_ER 信号线没有用到,必须将它下拉接地。

- TXD<3:0>(transmit data): TXD 由 RS 驱动,同步于 TX_CLK,在 TX_CLK 的时钟周期内,并且TX_EN 有效,TXD 上的数据被 PHY 接收,否则 TXD 的数据对 PHY 没有任何影响。

- TX_EN: 发送使能。TX_EN 由 Reconciliation 子层根据 TX_CLK 上升沿同步进行转换。

- TX_CLK(transmit clock): TX_CLK (Transmit Clock) 是一个连续的时钟信号(即系统启动,该信号就一直存在),它是 TX_EN、TXD、TX_ER(信号方向为从 RS 到 PHY)的参考时钟,TX_CLK 由 PHY 驱动 TX_CLK 的时钟频率是数据传输速率的 25%,偏差 ±100ppm。例如,100Mb/s 模式下,TX_CLK 时钟频率为 25MHz,占空比在 35% 至 65% 之间。

- COL(collision detected): COL 不需要同步于参考时钟。The behavior of the COL signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation。即半双工模式信号有效,全双工模式信号无效。

- RXD<3:0>(receive data): RXD由RS驱动,同步于 RX_CLK,在 RX_CLK 的时钟周期内,并且 RX_DV 有效,RXD 上的数据被RS 接收,否则 RXD 的数据对 RS 没有任何影响。While RX_DV is de-asserted, the PHY may provide a False Carrier indication by asserting the RX_ER signal while driving the value <1110> onto RXD<3:0>。

- RX_ER(receive error): RX_ER 同步于 RX_CLK,其在 RX 通道中的作用类似于 TX_ER 对于 TX 通道数据传输的影响。

- RX_CLK: 它与 TX_CLK 具有相同的要求,所不同的是它是 RX_DV、RXD、RX_ER(信号方向是从 PHY 到 RS)的参考时钟。RX_CLK 同样是由 PHY 驱动,PHY 可能从接收到的数据中提取时钟 RX_CLK,也有可能从一个名义上的参考时钟(e.g., the TX_CLK reference)来驱动RX_CLK。

- CRS(carrier sense): CRS 不需要同步于参考时钟,只要通道存在发送或者接收过程,CRS 就需要有效。The behavior of the CRS signal is unspecified when the duplex mode bit0.8 inthe control register is set to a logic one(自动协商禁止,人工设为全双工模式), or when the Auto-Negotiation process selects a full duplex mode of operation,即半双工模式信号有效,全双工模式信号无效。

- RX_DV(Receive Data Valid): RXD_DV 同步于 RX_CLK,被 PHY 驱动,它的作用如同于发送通道中的 TX_EN,不同的是在时序上稍有一点差别:为了让数据能够成功被RS接收,要求RXD_DV有效的时间必须覆盖整个 FRAME 的过程,即starting no later than the Start Frame Delimiter (SFD) and excluding any End-of-Frame delimiter。MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。

- MII 管理接口: 是个双信号接口,通过管理接口,MAC 就能监视和控制 PHY。其管理是使用 SMI(Serial Management Interface) 总线通过读写 PHY 的寄存器来完成的。一个是时钟信号(***MDC (management data clock))。另一个是数据信号(MDIO (management data input/output)***)。

- MDC: 由站管理实体向 PHY 提供,作为在 MDIO 信号上传送信息的定时参考。MDC 是一种非周期性的信号,没有最高或最低时间。无论 TX_CLK 和 RX_CLK 的标称周期如何,MDC 的最小高低时间应为 160 ns,MDC 的最小周期为 400 ns。

- MDIO: 是 PHY 和 STA 之间的双向信号。它用于在 PHY 和 STA 之间传输控制信息和状态。控制信息由 STA 同步地针对 MDC 驱动并且由 PHY 同步地采样。状态信息由 PHY 针对 MDC 同步驱动并由 STA 同步采样。

PHY 里面的部分寄存器是 IEEE 定义的,这样PHY把自己的目前的状态反映到寄存器里面。

MAC 通过 SMI 总线不断的读取PHY 的状态寄存器以得知目前 PHY 的状态。例如连接速度、双工的能力等。

当然也可以通过 SMI 设置 PHY的寄存器达到控制的目的。例如流控的打开关闭、自协商模式还是强制模式等。

不论是物理连接的MII总线和 SMI 总线,还是 PHY 的状态寄存器和控制寄存器都是由IEEE的规范的。因此不同公司的 MAC 和 PHY 一样可以协调工作。当然为了配合不同公司的 PHY 的自己特有的一些功能,驱动需要做相应的修改。

MII 支持 10Mbps 和 100Mbps 的操作,一个接口由 14 根线组成,它的支持还是比较灵活的。

但是有一个缺点是因为它一个端口用的信号线太多,如果一个 8 端口的交换机要用到 112 根线,16 端口就要用到 224 根线,到 32 端口的话就要用到 448 根线。

一般按照这个接口做交换机是不太现实的。所以现代的交换机的制作都会用到其它的一些从 MII 简化出来的标准,比如 RMII、SMII、GMII等。

什么是RMII

简化媒体独立接口是标准的以太网接口之一,比 MII 有更少的 I/O 传输。RMII 口是用两根线来传输数据的,MII 口是用 4 根线来传输数据的,GMII 是用 8 根线来传输数据的。MII/RMII 只是一种接口,对于10Mbps 线速,MII 的时钟速率是 2.5MHz 就可以了,RMII 则需要 5MHz;对于 100Mbps 线速,MII 需要的时钟速率是 25MHz,RMII 则是 50MHz。

MII/RMII 用于传输以太网包,在 MII/RMII 接口是 4/2bit 的,在以太网的PHY里需要做串并转换,编解码等才能在双绞线和光纤上进行传输,其帧格式遵循IEEE 802.3(10M)/IEEE 802.3u(100M)/IEEE 802.1q(VLAN)。

以太网帧的格式为:前导符 + 开始位 + 目的 mac 地址 + 源 mac 地址 + 类型/长度 + 数据 + padding(optional) + 32bitCRC。如果有 vlan,则要在类型/长度后面加上 2 个字节的 vlan tag,其中 12bit 来表示vlan id,另外,4bit 表示数据的优先级!

什么是GMII

GMII是千兆网的MII接口,这个也有相应的RGMII接口,表示简化了的GMII接口。GMII 采用 8 位接口数据,工作时钟125MHz,因此传输速率可达 1000Mbps。同时兼容 MII 所规定的10/100 Mbps工作方式。GMII 接口数据结构符合IEEE以太网标准,该接口定义见 IEEE 802.3-2000。

| GTX_CLK | 1000M发送时钟 | MAC → PHY |

| TX_CLK | 100/10M发送时钟 | MAC → PHY |

| TX_ER | 发送数据错误 | MAC → PHY |

| TX_EN | 发送使能 | MAC → PHY |

| TX_[7:0] | 发送数据8bit | MAC → PHY |

| RX_CLK | 接收时钟 | PHY → MAC |

| RX_DV | 接收数据有效 | PHY → MAC |

| RX_ER | 接收数据错误 | PHY → MAC |

| RX_[7:0] | 接收数据8bit | PHY → MAC |

| CRS | 载波监测 | PHY → MAC |

| COL | 冲突碰撞监测 | PHY → MAC |

| MDIO | 管理数据 | 双向 |

| MDC | 管理数据时钟 | MAC → PHY |

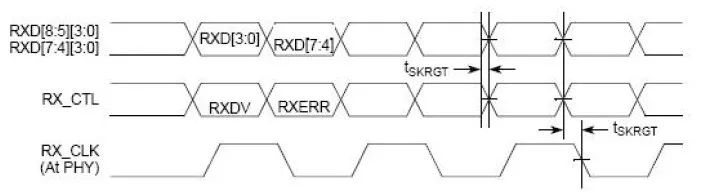

什么是RGMII

RGMII(Reduced Gigabit Media Independant Interface),精简GMII接口。相对于GMII相比,RGMII具有如下特征:

- 发送/接收数据线由8条改为4条

- TX_ER和TX_EN复用,通过TX_CTL传送

- RX_ER与RX_DV复用,通过RX_CTL传送

- 1 Gbit/s速率下,时钟频率为125MHz

- 100 Mbit/s速率下,时钟频率为25MHz

- 10 Mbit/s速率下,时钟频率为2.5MHz

信号定义如下:

| TXC | 发送时钟 | MAC→PHY |

| TX_CTL | 发送数据控制 | MAC → PHY |

| TXD[3:0] | 发送数据4bit | MAC → PHY |

| RXC | 接收时钟 | PHY → MAC |

| RX_CTL | 接收数据控制 | PHY → MAC |

| RXD[3:0] | 接收数据4bit | PHY → MAC |

| MDIO | 管理数据 | 双向 |

| MDC | 管理数据时钟 | MAC → PHY |

虽然RGMII信号线减半,但TXC/RXC时钟仍为125Mhz,为了达到1000Mbit的传输速率,TXD/RXD信号线在时钟上升沿发送接收GMII接口中的TXD[3:0]/RXD[3:0],在时钟下降沿发送接收TXD[7:4]/RXD[7:4],并且信号TX_CTL反应了TX_EN和TX_ER状态,即在TXC上升沿发送TX_EN,下降沿发送TX_ER,同样的道理试用于RX_CTL,下图为发送接收的时序:

什么是SMI

SMI:串行管理接口(Serial Management Interface),通常直接被称为MDIO接口(Management Data Input/Output Interface)。MDIO最早在IEEE 802.3的第22卷定义,后来在第45卷又定义了增强版本的MDIO,其主要被应用于以太网的MAC和PHY层之间,用于MAC层器件通过读写寄存器来实现对PHY层器件的操作与管理。

MDIO主机(即产生MDC时钟的设备)通常被称为STA(Station Management Entity),而MDIO从机通常被称为MMD(MDIO Management Device)。通常STA都是MAC层器件的一部分,而MMD则是PHY层器件的一部分。

MDIO接口包括两条线,MDIO和MDC,其中MDIO是双向数据线,而MDC是由STA驱动的时钟线。MDC时钟的最高速率一般为2.5MHz,MDC也可以是非固定频率,甚至可以是非周期的。MDIO接口只是会在MDC时钟的上升沿进行采样,而并不在意MDC时钟的频率(类似于I2C接口)。如下图所示。

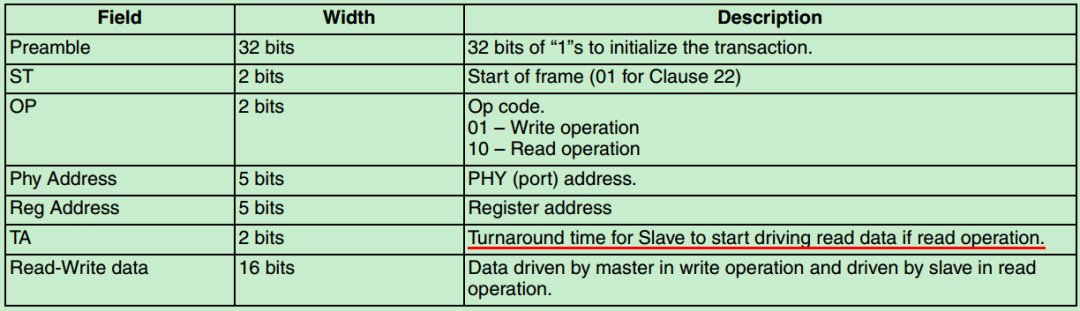

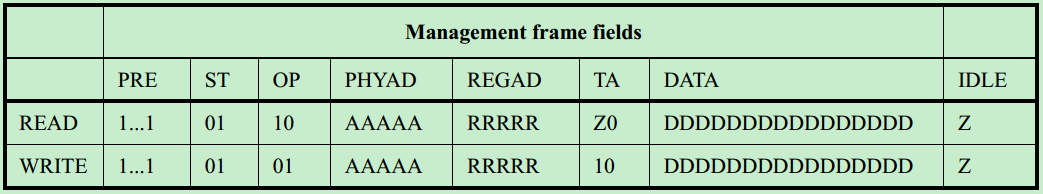

MDIO接口有两个版本,通常被称为卷22版本和卷45版本。卷22版本的MDIO接口最多支持连接32个MMD(PHY层设备),每个设备最多支持32个寄存器。卷45版本的MDIO接口最多支持连接32个MMD,32个设备类型,每个设备最多支持64K个寄存器。卷22版本的MDIO接口的数据帧格式如下:

具体每个bit描述如下:

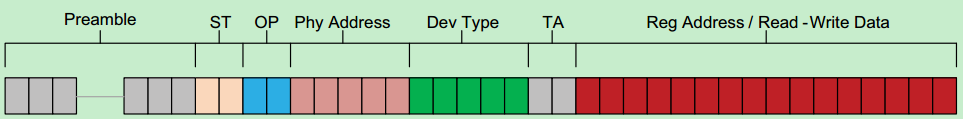

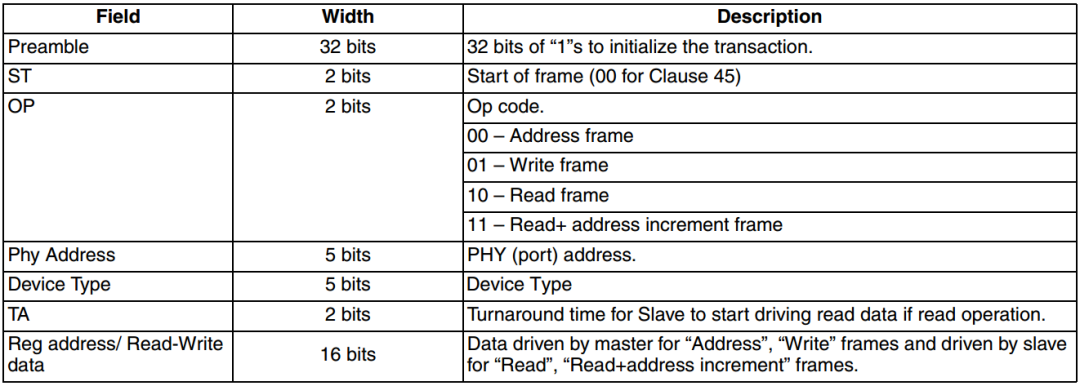

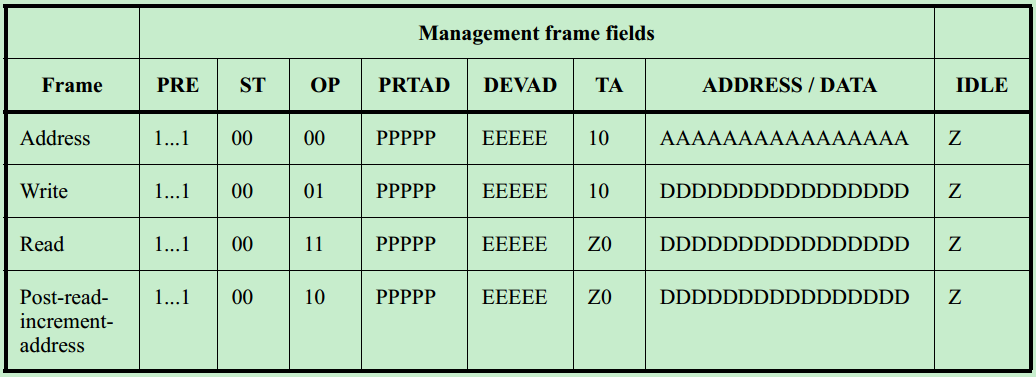

卷45版本的MDIO接口的数据帧格式如下:

具体每个bit的描述如下:

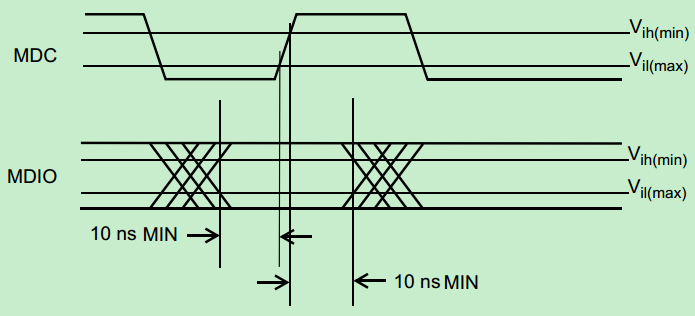

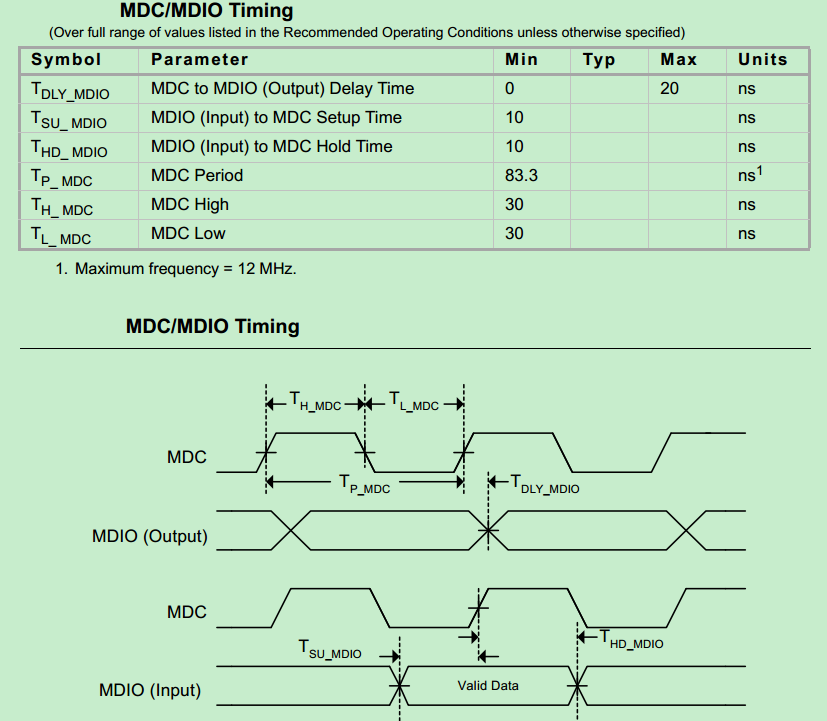

如果是STA(MAC层设备)驱动MDIO,则MDIO相对于MDC上升沿,至少要有10ns的建立时间(Setup Time)和10ns的保持时间(Hold Time)。如下图所示:

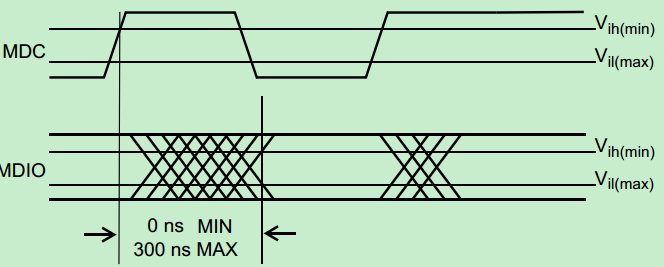

如果MDIO是由MMD(PHY层设备)驱动的,则MDIO相对于MDC的Tco(Clock to Output Delay)的范围是0ns~300ns。如下图所示:

实际上,MDC的频率也并非一定是小于或等于2.5MHz,比如Marvell的88E1512最大支持12MHz的MDC:

IEEE 802.3建议同时对MDIO进行下拉(下拉电阻建议为2k欧姆+5%),和上拉(上拉电阻建议为1.5k欧姆+5%),使得在TA时,MDIO处于中间态。但是并非所有的PHY器件都有这样的要求,比如Marvell的88E1512只要求对MDIO进行上拉即可,上拉电阻范围为1.5k~10kΩ。

QA

网卡的MAC和PHY间的关系?

网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口.物理层的芯片称之为PHY.

数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能.以太网卡中数据链路层的芯片称之为MAC控制器.

很多网卡的这两个部分是做到一起的.他们之间的关系是pci总线接mac总线,mac接phy,phy接网线(当然也不是直接接上的,还有一个变压装置).

网卡上除RJ-45接口外,还需要其它元件吗?

PHY和MAC是网卡的主要组成部分,网卡一般用RJ-45插口,10M网卡的RJ-45插口也只用了1,2,3,6四根针,而100M或1000M网卡的则是八根针都是全的.

除此以外,还需要其它元件,因为虽然PHY提供绝大多数模拟支持,但在一个典型实现中,仍需外接6,7只分立元件及一个局域网绝缘模块.绝缘模块一般采用一个1:1的变压器.这些部件的主要功能是为了保护PHY免遭由于电气失误而引起的损坏.

另外,一颗CMOS制程的芯片工作的时候产生的信号电平总是大于0V的(这取决于芯片的制程和设计需求),但是这样的信号送到100米甚至更长的地方会有很大的直流分量的损失.而且如果外部网线直接和芯片相连的话,电磁感应(打雷)和静电,很容易造成芯片的损坏.再就是设备接地方法不同,电网环境不同会导致双方的0V电平不一致,这样信号从A传到B,由于A设备的0V电平和B点的0V电平不一样,这样会导致很大的电流从电势高的设备流向电势低的设备.

为了解决以上问题Transformer(隔离变压器)这个器件就应运而生.它把PHY送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到连接网线的另外一端.这样不但使网线和PHY之间没有物理上的连接而换传递了信号,隔断了信号中的直流分量,还可以在不同0V电平的设备中传送数据.

隔离变压器本身就是设计为耐2KV~3KV的电压的.也起到了防雷感应(我个人认为这里用防雷击不合适)保护的作用.有些朋友的网络设备在雷雨天气时容易被烧坏,大都是PCB设计不合理造成的,而且大都烧毁了设备的接口,很少有芯片被烧毁的,就是隔离变压器起到了保护作用.

隔离变压器本身是个被动元件,只是把PHY的信号耦合了到网线上,并没有起到功率放大的作用.那么一张网卡信号的传输的最长距离是谁决定的呢?

一张网卡的传输最大距离和与对端设备连接的兼容性主要是PHY决定的.但是可以将信号送的超过100米的PHY其输出的功率也比较大,更容易产生EMI的问题.这时候就需要合适的Transformer与之配合.作PHY的老大公司Marvell的PHY,常常可以传送180~200米的距离,远远超过IEEE的100米的标准.

RJ-45的接头实现了网卡和网线的连接.它里面有8个铜片可以和网线中的4对双绞(8根)线对应连接.其中100M的网络中1,2是传送数据的,3,6是接收数据的.1,2之间是一对差分信号,也就是说它们的波形一样,但是相位相差180度,同一时刻的电压幅度互为正负.这样的信号可以传递的更远,抗干扰能力强.同样的,3,6也一样是差分信号.

网线中的8根线,每两根扭在一起成为一对.我们制作网线的时候,一定要注意要让1,2在其中的一对,3,6在一对.否则长距离情况下使用这根网线的时候会导致无法连接或连接很不稳定.

现在新的PHY支持AUTO MDI-X功能(也需要Transformer支持).它可以实现RJ-45接口的1,2上的传送信号线和3,6上的接收信号线的功能自动互相交换.有的PHY甚至支持一对线中的正信号和负信号的功能自动交换.这样我们就不必为了到底连接某个设备需要使用直通网线还是交叉网线而费心了.这项技术已经被广泛的应用在交换机和SOHO路由器上.

在1000Basd-T网络中,其中最普遍的一种传输方式是使用网线中所有的4对双绞线,其中增加了4,5和7,8来共同传送接收数据.由于1000Based-T网络的规范包含了AUTOMDI-X功能,因此不能严格确定它们的传出或接收的关系,要看双方的具体的协商结果.

一片网卡主要功能的实现就基本上是上面这些器件了.

其他的,还有一颗EEPROM芯片,通常是一颗93C46.里面记录了网卡芯片的供应商ID,子系统供应商ID,网卡的MAC地址,网卡的一些配置,如SMI总线上PHY的地址,BOOTROM的容量,是否启用BOOTROM引导系统等东西.

很多网卡上还有BOOTROM这个东西.它是用于无盘工作站引导操作系统的.既然无盘,一些引导用必需用到的程序和协议栈就放到里面了,例如RPL,PXE等.实际上它就是一个标准的PCI ROM.所以才会有一些硬盘写保护卡可以通过烧写网卡的BootRom来实现.其实PCI设备的ROM是可以放到主板BIOS里面的.启动电脑的时候一样可以检测到这个ROM并且正确识别它是什么设备的.AGP在配置上和PCI很多地方一样,所以很多显卡的BIOS也可以放到主板BIOS里面.这就是为什么板载的网卡我们从来没有看到过BOOTROM的原因.

最后就是电源部分了.大多数网卡现在都使用3.3V或更低的电压.有的是双电压的.因此需要电源转换电路.

而且网卡为了实现Wake on line功能,必须保证全部的PHY和MAC的极少一部分始终处于有电的状态,这需要把主板上的5V Standby电压转换为PHY工作电压的电路.在主机开机后,PHY的工作电压应该被从5V转出来的电压替代以节省5V Standby的消耗.(许多劣质网卡没有这么做).

有Wake on line功能的网卡一般还有一个WOL的接口.那是因为PCI2.1以前没有PCI设备唤醒主机的功能,所以需要着一根线通过主板上的WOL的接口连到南桥里面以实现WOL的功能.新的主板合网卡一般支持PCI2.2/2.3,扩展了PME#信号功能,不需要那个接口而通过PCI总线就可以实现唤醒功能.

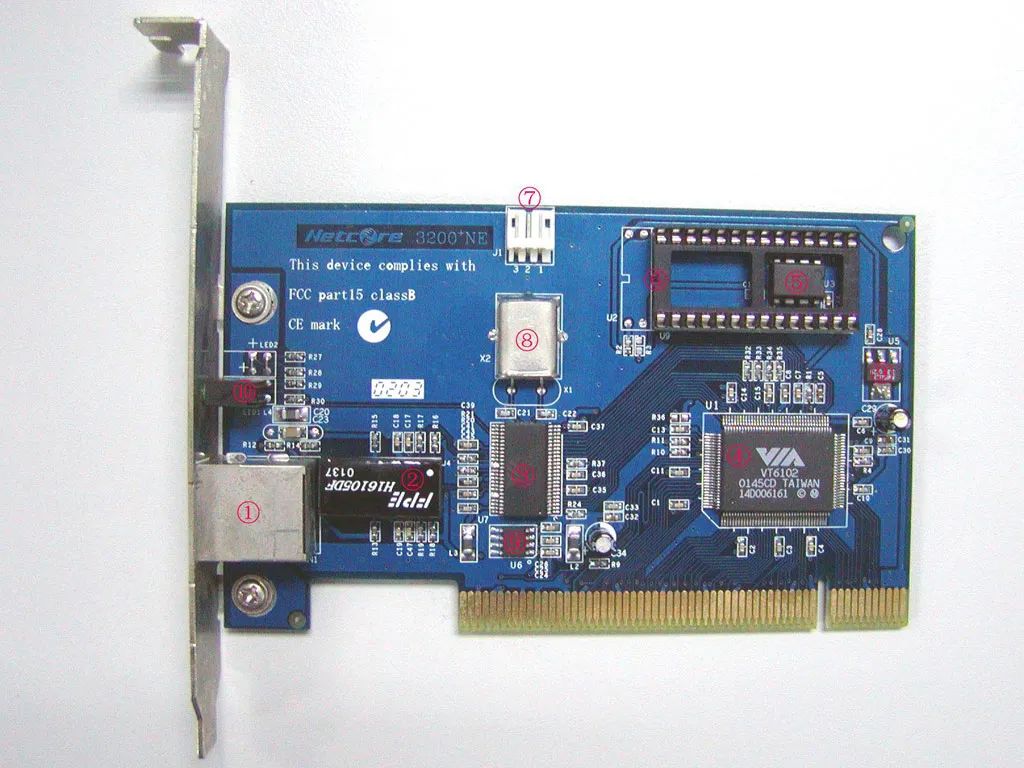

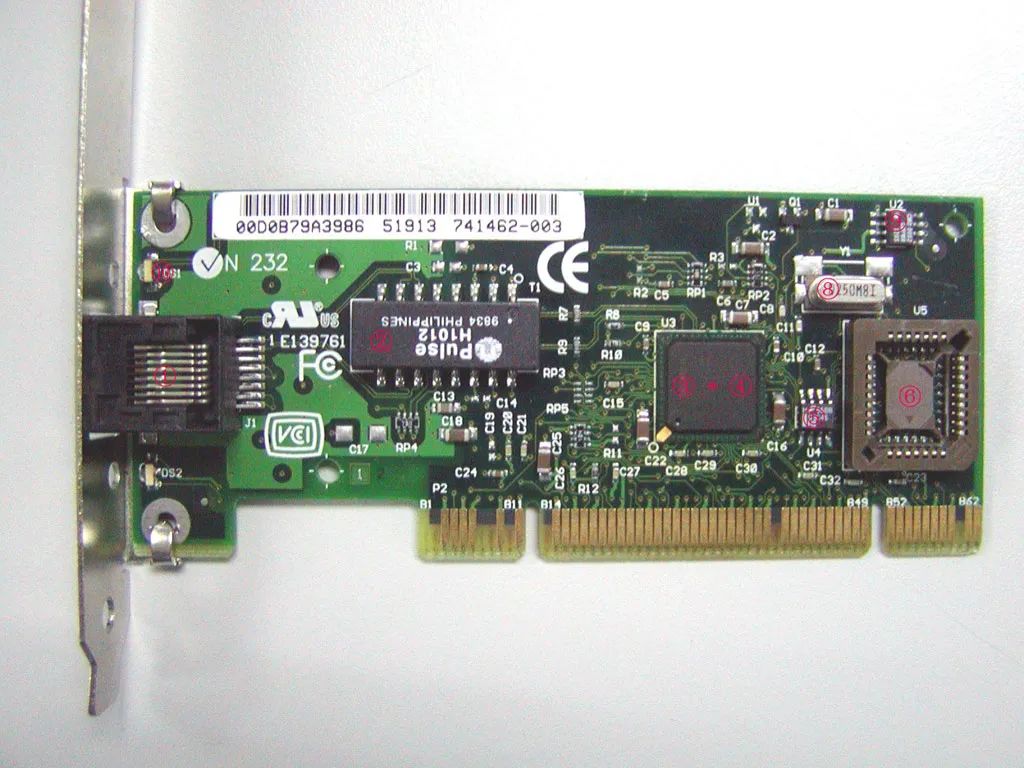

我们现在来看两个图

MAC和PHY分开的以太网卡

MAC和PHY集成在一颗芯片的以太网卡

上图中各部件为:

①RJ-45接口

②Transformer(隔离变压器)

③PHY芯片

④MAC芯片

⑤EEPROM

⑥BOOTROM插槽

⑦WOL接头

⑧晶振

⑨电压转换芯片

⑩LED指示灯

网卡的功能主要有两个:一是将电脑的数据封装为帧,并通过网线(对无线网络来说就是电磁波)将数据发送到网络上去;二是接收网络上其它设备传过来的帧,并将帧重新组合成数据,发送到所在的电脑中.网卡能接收所有在网络上传输的信号,但正常情况下只接受发送到该电脑的帧和广播帧,将其余的帧丢弃.然后,传送到系统CPU做进一步处理.当电脑发送数据时,网卡等待合适的时间将分组插入到数据流中.接收系统通知电脑消息是否完整地到达,如果出现问题,将要求对方重新发送.

PHY和MAC之间如何进行沟通

通过IEEE定义的标准的MII/GigaMII(Media Independed Interfade,介质独立界面)界面连接MAC和PHY。这个界面是IEEE定义的。MII界面传递了网络的所有数据和数据的控制。

而MAC对PHY的工作状态的确定和对PHY的控制则是使用SMI(Serial Management Interface)界面通过读写PHY的寄存器来完成的。PHY里面的部分寄存器也是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。

我们看到了,不论是物理连接的MII界面和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

一片网卡主要功能的实现就基本上是上面这些器件了。

其他的,还有一颗EEPROM芯片,通常是一颗93C46。里面记录了网卡芯片的供应商ID、子系统供应商ID、网卡的MAC地址、网卡的一些配置,如SMI总线上PHY的地址,BOOTROM的容量,是否启用BOOTROM引导系统等东西。

很多网卡上还有BOOTROM这个东西。它是用于无盘工作站引导操作系统的。

既然无盘,一些引导用必需用到的程序和协议栈就放到里面了,例如RPL、PXE等。实际上它就是一个标准的PCI ROM。所以才会有一些硬盘写保护卡可以通过烧写网卡的BootRom来实现。

其实PCI设备的ROM是可以放到主板BIOS里面的。启动电脑的时候一样可以检测到这个ROM并且正确识别它是什么设备的。AGP在配置上和PCI很多地方一样,所以很多显卡的BIOS也可以放到主板BIOS里面。这就是为什么板载的网卡我们从来没有看到过BOOTROM的原因。

https://www.rohde-schwarz.taipei/data/activity/file/1668753017911720319.pdf

DATA RATE EVOLUTION IN HIGH-SPEED TECHNOLOGIES AND CHALLENGES FOR HIGH-SPEED PCBS AND INTERCONNECTS WITH PCIE 5.0

https://www.cnblogs.com/LiamJacob/p/17675759.html

物理编码层(PCS)的作用和结构

- PCS 是万兆以太网中负责将 MAC 层的数据转换为适合高速传输的格式的层

- PCS 的主要功能有:

- 将 64 位数据转换为 66 位数据,添加同步头(SYNC Header)来区分不同类型的帧

- 对数据进行加扰(Scrambling)来保证零一均衡,避免直流失调和时钟恢复困难

- 对数据进行变速器(Gearbox)操作,实现并行数据和串行数据之间的速率转换

- 对接收到的数据进行同步头搜索(SYNC Header Search),实现帧对齐和锁定

- 对发送端的数据进行序列暂停(Sequence Pause),实现流量控制

- PCS 的结构如下图所示:

与 NRZ 相比,PAM4 也存在一些缺点。它的信噪比 (SNR) 比 NRZ 低约 -9.54 dB,反射强度是 NRZ 的三倍

https://fpga.eetrend.com/content/2019/100017255.html

本文主要介绍以太网Drive Side接口(MAC和PHY之间的接口),也被称为MII(Media Independent Interface),支持从10M到100G的不同应用场合,主要包括MII、RMII、SMII(Cisco Systems Specification)、SSMII、S3MII、GMII、RGMII、SGMII、QSGMII(Cisco Systems Specification)、TBI、RTBI、XGMII、XAUI、RXAUI、XLGMII、XLAUI、CGMII、CAUI、HIGIG(Broadcom Specification)、Interlaken等接口,下面就针对10Mbps到100Gbps的不同接口进行介绍,最后介绍一下PHY芯片的控制接口MDIO BUS

1、MII接口

100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。TXC和RXC均由PHY提供。PHY在TXC的上升沿采样TXD上的数据,MAC在RXC的上升沿采样RXD上的数据。

2、RMII接口

REF_CLK是由外部时钟源提供的50MHz参考时钟,与MII接口不同,MII接口中的接收时钟和发送时钟是分开的,而且都是由PHY芯片提供给MAC芯片的。这里需要注意的是,由于数据接收时钟是由外部晶振提供而不是由载波信号提取的,所以在PHY层芯片内的数据接收部分需要设计一个FIFO,用来协调两个不同的时钟,在发送接收的数据时提供缓冲。PHY层芯片的发送部分则不需要FIFO,它直接将接收到的数据发送到MAC就可以了。

3、SMII(Cisco Systems Specification)接口

REF_CLK:所有端口共用的一个参考时钟,频率为125MHz,为什么100Mbps速率要用125MHz时钟呢?因为在每8位数据中会插入2位控制信号。

TXD/RXD以10比特为一组,以SYNC为高电平来指示一组数据的开始,在SYNC变高后的10个时钟周期内,TXD上依次输出的数据是:TXD[7:0]、TX_EN、TX_ER,控制信号的含义与MII接口中的相同;RXD上依次输出的数据是:RXD[7:0]、RX_DV、CRS,RXD[7:0]的含义与RX_DV有关,当RX_DV为有效时(高电平),RXD[7:0]上传输的是物理层接收的数据。当RX_DV为无效时(低电平),RXD[7:0]上传输的是物理层的状态信息数据。

当速率为10Mbps时,每一组数据要重复10次,MAC/PHY芯片每10个周期采样一次。MAC/PHY芯片在接收到数据后会进行串/并转换。

4、SSMII接口

5、S3MII接口

6、GMII接口

GMII的数据宽度为8位,GMII接口中的发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的),在用作MII模式时,使用TX_CLK和8根数据线中的4根。

7、RGMII接口

RGMII的时钟频率为125MHz,TX/RX数据宽度从8为变为4位,为了保持1000Mbps的传输速率不变,RGMII接口在时钟的上升沿和下降沿都采样数据。在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7:4]。RGMII同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。

TX_EN信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,下降沿发送TX_ER;同样的,RX_DV信号线上也传送RX_DV和RX_ER两种信息,在RX_CLK的上升沿发送RX_DV,下降沿发送RX_ER。

8、SGMII接口

SGMII收发各一对差分信号线,时钟频率625MHz,在时钟信号的上升沿和下降沿均采样,参考时钟RX_CLK由PHY提供,是可选的,主要用于MAC侧没有时钟的情况,一般情况下,RX_CLK不使用。收发都可以从数据中恢复出时钟。

在TXD发送的串行数据中,每8比特数据会插入TX_EN/TX_ER两比特控制信息,同样,在RXD接收数据中,每8比特数据会插入RX_DV/RX_ER两比特控制信息,所以总的数据速率为1.25Gbps=625Mbps*2。

其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8b/10b变换,本来8b/10b变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8b/10b变换在MAC芯片中完成了。8b/10b变换的主要作用是扰码,让信号中不出现过长的连“0”和连“1”情况,影响时钟信息的提取。

9、TBI接口

TBI即Ten BitInterface的意思,接口数据位宽由GMII接口的8位增加到10位,其实,TBI接口跟GMII接口的差别不是很大,多出来的2位数据主要是因为在TBI接口下,MAC芯片在将数据发给PHY芯片之前进行了8b/10b变换(8b/10b变换本是在PHY芯片中完成的,TBI在MAC中完成了,所以每传输一个字节需要传输10bit数据)。

RBC0和RBC1是从接收数据中恢复出来的半频时钟,频率为62.5MHz,RBC0和RBC1不是差分信号,而是两个独立的信号,两者之间有180度的相位差,在这两个时钟的上升沿都采样数据。RBC0和RBC1也叫伪差分信号。除掉上面说到的之外,剩下的信号都跟GMII接口中的相同。

大多数芯片的TBI接口和GMII接口兼容。在用作TBI接口时,CRS和COL一般不用。

10、RTBI接口

RTBI接口数据位宽为5bit,时钟频率为125MHz,在时钟的上升沿和下降沿都采样数据,同RGMII接口一样,TX_EN线上会传送TX_EN和TX_ER两种信息,在时钟的上升沿传TX_EN,下降沿传TX_ER;RX_DV线上传送RX_DV和RX_ER两种信息,在RX_CLK上升沿传RX_DV,下降沿传RX_ER。

11、XGMII接口

XGMII接口的单端信号采用HSTL/SSTL_2逻辑,端口电压1.5V/2.5V,由于SSTL_2的端口电压高,功耗大,现在已很少使用。

TXC[3:0]:发送通道控制信号,TXC=0时,表示TXD上传输的是数据;TXC=1时,表示TXD上传输的是控制字符。TXC[3:0]分别对应TXD[31:24],TXD[23:16],TXD[15:8],TXD[7:0]。

RXC[3:0]:接收通道控制信号,RXC=0时,表示RXD上传输的是数据;RXC=1时,表示RXD上传输的是控制字符。RXC[3:0]分别对应RXD[31:24],RXD[23:16],RXD[15:8],RXD[7:0]。

TX_CLK:TXD和TXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。

RX_CLK:RXD和RXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。156.25MHz*2*32=10Gbps。

XGMII接口还有XLGMII(40Gb)、CGMII(100Gb)等变种。其基本已经被XAUI/XLAUI/CAUI接口取代了。

12、XAUI接口

XAUI接口有如下一系列的变种:RXAUI、XLAUI(40Gb)、CAUI(100Gb)等。

由于受电气特性的影响,XGMII接口的PCB走线最大传输距离仅有7cm,并且XGMII接口的连线数量太多,给实际应用带来不便。因此,在实际应用中,XGMII接口通常被XAUI接口代替,XAUI即10Gigabit Attachment Unit Interface,XAUI在XGMII的基础上实现了XGMII接口的物理距离扩展,将PCB走线的传输距离增加到50cm,使背板走线成为可能。

源端XGMII把收发32位宽度数据流分为4个独立的lane通道,每个lane通道对应一个字节,经XGXS(XGMII ExtenderSublayer)完成8b/10b编码后,将4个lane分别对应XAUI的4个独立通道,XAUI端口速率为:2.5Gbps*1.25*4=12.5Gbps。

在发送端的XGXS模块中,将TXD[31:0]/RXD[31:0],TXC[3:0]/RXC[3:0],TX_CLK/RX_CLK转换成串行数据从TX Lane[3:0]/RX Lane[3:0]中发出去,在接收端的XGXS模块中,串行数据被转换成并行,并且进行时钟恢复和补偿,完成时钟去抖,经过5b/4b解码后,重新聚合成XGMII。

XAUI接口采用差分线,收发各四对,CML逻辑,AC耦合方式,耦合电容在10nF~100nF之间。

XAUI接口可以直接接光模块,如XENPAK/X2等。也可以转换成一路10G信号XFI,接XFP/SFP+等。

有些芯片不支持XAUI接口,只支持XGMII接口,这时可以用专门的芯片进行XGMII→XAUI接口转换,如BCM8011等。

XAUI/XLAUI/CAUI是四通道串行总线,采用的差分信号,CML逻辑传输,并且进行了扰码,大大增强了信号的抗扰性能,使得信号的有效传输距离增加到50cm。

XAUI/XLAUI/CAUI在物理结构上是一样的,收发通道独立,各四对差分信号线。

对于XAUI总线,每对差分线上的数据速率为3.125Gbps,总数据带宽为12.5Gbps,有效带宽为12.5Gbps*0.8=10Gbps(因为XAUI总线数据在传输前进行了8b/10b变换,编码效率为80%)。

对于XLAUI总线,每对差分线上的数据速率为10.3125Gbps,总数据带宽为41.25Gbps,有效带宽为41.25Gbps*(64/66)=40Gbps(因为XLAUI总线数据在传输前进行了64b/66B变换,编码效率为96.97%)。

对于CAUI总线,每对差分线上的数据速率为25.78125Gbps,总数据带宽为103.125Gbps,有效带宽为103.125Gbps*(64/66)=100Gbps(因为CAUI总线数据在传输前进行了64B/66B变换,编码效率为96.97%)。

13、Interlaken

Interlaken是Cisco和Cortina公司共同推出的一种高速通道化的C2C(芯片间)接口协议。主要用于10Gbps端口的MAC、OC-768SONET Framer、下一代100Gbps以太网集成电路、100Gbps Swich Fabric与包处理器。主要有以下特征:

- 支持256个通道,可以扩展到64K;

- 与SPI4.2(SystemPacket Interface Level 4 (SPI-4) Phase 2 Revision 1: OC-192 System Interfacefor Physical and Link Layer Devices.(OIF-SPI-4-2.1))类似,通过简单control word来表示packet;

- 通过Meta Frame完成各个lane的对齐;

- 协议本身和实际使用lane数目和SerDes速率无关;

- 提供带外带内两种flow control方式,以及xon/xoff的整个接口的flow control;

- 采用64/67B数据编码;

- 接口本身性能随lane增加而同比增加。

TX_Ddta[n:0]p/n:数据发送通道,CML差分电平,每对差分线速率为1~6.25Gbps;

TX_FC_CLK:数据发送通道带外流控参考时钟,LVCMOS电平;

TX_FC_SYNC:数据发送通道带外流控同步信号,LVCMOS电平;

TX_FC_DATA:数据发送通道带外流控数据信号,LVCMOS电平;

RX_Ddta[n:0]p/n:数据接收通道,CML差分电平,每对差分线速率为1~6.25Gbps;

RX_FC_CLK:数据接收通道带外流控参考时钟,LVCMOS电平;

RX_FC_SYNC:数据接收通道带外流控同步信号,LVCMOS电平;

RX_FC_DATA:数据接收通道带外流控数据信号,LVCMOS电平;

14、MDIO BUS(SMI(Serial Management Interface))

MDIO是一个以太网控制器的传输协议,广泛用于以太网控制器和PHY之间的数据通讯。

MDIO(Management Data Input/Output),管理数据输入输出总线。它是由IEEE802.3定义的以太网行业标准,它承载着MAC层和物理层通信的重任。MDIO接口包括两根信号线:时钟线MDC,数据线MDIO(双向),MAC层芯片(或其他控制芯片)可以通过它们访问物理层芯片的寄存器,并通过这些寄存器来对物理芯片进行控制和管理。

MDC(Management Data Clock):管理接口的时钟,是一个非周期信号,信号的最小周期为400ns(最快2.5MHz),最小正电平时间和负电平时间为160ns,最大正负电平时间无限制。

MDIO(Management Data Input/Output):是双向的数据线,用来传送MAC层的控制信息和物理层的状态信息。它与MDC时钟同步,在MDC上升沿有效。

14.1、MDIO帧格式

PRE:帧前缀域,为32个连续“1”比特,这帧前缀域不是必需的,某些物理层芯片的MDIO操作就没有这个域。

ST:帧开始标识码,为“01”。

OP:帧操作码(读写操作),比特“10”表示此帧为一读操作帧,比特“01”表示此帧为一写操作帧。

PHYAD:PHY芯片的地址,5个比特,每个芯片都把自己的地址与这5个比特进行比较,若匹配则响应后面的操作,若不匹配,则忽略掉后面的操作。一个系统最多联31个PHY(地址0为保留)。

REGAD:用来选择物理层芯片的32个寄存器中的某个寄存器的地址。一个PHY上最多32个寄存器地址(可以使用shadow value技术,访问更多的寄存器)。

TA:状态转换域,若为读操作,则第一比特时MDIO为高阻态,第二比特时由物理层芯片使MDIO置“0”。若为写操作,则MDIO仍由MAC层芯片控制,其连续输出“10”两个比特。

DATA:帧的寄存器的数据域,16比特,若为读操作,则为物理层送到MAC层的数据,若为写操作,则为MAC层送到物理层的数据。

IDLE:帧结束后的空闲状态,此时MDIO无源驱动,处于高阻状态,但一般用上拉电阻使其处在高电平,即MDIO引脚需要上拉电阻。

14.2、MDIO操作时序

MDIO工作流程如下:

- Preamle(PRE):在没有传输数据的空闲状态时,数据线MDIO处于高阻态(由于外部上拉,故一直为1)。

- Start of Frame(ST):MAC驱动MDIO线,出现一个2bit的开始标识码(01)。

- Operation Code(OP):MAC驱动MDIO线,出现一个2bit数据来标识是读操作(10)还是写操作(01)。

- PHY Address(PHYAD):MAC驱动MDIO线,出现一个5bit数据标识PHY的地址,对应该地址的PHY芯片会响应。

- Reg Address(REGAD):MAC驱动MDIO线,出现一个5bit的PHY芯片寄存器地址(需要读/写的地址)。

- Turnaround(TA):写操作的话,MAC驱动MDIO线,出现10;读操作的话,MDIO pin of MAC must be put in high-impedance state,在第二个周期,PHY驱动MDIO线,出现0。

- Data,MDIO串行读出/写入PHY芯片寄存器的数据(16bit)。

- 最后MDIO恢复成空闲状态(IDLE),同时MDIO进入高阻状态。

本文主要介绍了以太网MAC和PHY之间的接口,支持10Mbps到100Gbps的不同速率等级,同时介绍了PHY芯片的控制接口MDIO总线。

https://www.ieee802.org/misc-docs/GlobeCom2009/IEEE_802d3_Law.pdf

参考:

https://app-community.fs.com/blog/25g-50g-100g-technology-and-trend.html

https://www.itu.int/epublications/publication/itu-t-g-9806-2020-cor-2-2024-08

https://www.pxisa.org/wp-content/uploads/2022/10/HighSpeedSerial_WP_Final.pdf

https://www.ieee802.org/3/10GEPON_study/public/july06/thaler_1_0706.pdf

https://www.01signal.com/ -----A brief introduction to 8b/10b encoding, 64b/66b, 128b/130b e

https://www.ieee802.org/3/bn/public/mar13/hajduczenia_3bn_04_0313.pdf 64b/66b line code

https://www.ieee802.org/3/by/public/Mar15/slavick_3by_02a_0315.pdf 25G PHY types

https://www.ieee802.org/3/cd/public/May16/lusted_3cd_02_0516.pdf Nomenclature

https://ethernettechnologyconsortium.org/wp-content/uploads/2020/03/25G-50G-Specification-FINAL.pdf 比较老,速率不含编码

50G links can optionally instantiate a FEC sublayer. When the link is configured to use Firecode FEC, the FEC sublayer operates similarly to Clause 74 FEC at x1.25 rate, transmitting and receiving data at 51.5625 Gb/s over 4 lanes at 12.89063 Gb/s each.

https://cn.fs.com/mo/blog/25g-50g-100g-technology-and-trend-2726.html

https://www.iol.unh.edu/sites/default/files/testsuites/ethernet/Cl137/IEEE802.3_CL137_PMD_TestPlan.pdf 50, 100, 200 AND 400 GIGABIT ETHERNET TESTING SERVICE Clause 137 50GBASE-KR, 100GBASE-KR2, and 200GBASE-KR4 PMD Test Plan

https://symmetron.ua/image/catalog/2023_1/k_39.pdf

https://www.keysight.com/us/en/assets/7018-06273/data-sheets-archived/5992-3195.pdf N1091BSCA IEEE 802.3bs/cd Measurement and Debug Application

https://grouper.ieee.org/groups/802/3/cd/public/Mar18/sakai_3cd_01_0318.pdf ERL Measured Results for 50G-KR Device (comment #r01-89)

https://www.ieee802.org/3/bj/public/may12/diminico_01a_0512.pdf IEEE 802.3bj: 100GBASE-CR4 Specifications

https://www.intel.com/content/www/us/en/docs/programmable/683805/current/100gbase-kr4-mapping-ieee802-3bj-clause-91.html FEC选用RS(528,514)而不是RS(544,514)

https://ethernetalliance.org/wp-content/uploads/2023/03/EA_50G_HSN_Webinar.pdf Ethernet in the Field 50Gb/s Lane Rate Webinar

https://www.ieee802.org/3/bj/public/may12/diminico_01a_0512.pdf IEEE 802.3bj: 100GBASE-CR4 Specifications

https://www.ieee802.org/3/hssg/public/sep06/law_01_0906.pdf Overview of 10G Ethernet Family

浙公网安备 33010602011771号

浙公网安备 33010602011771号