ICEE-开关电源的驱动控制原理: 二极管 + MOS管工作原理 + CMOS | SiC | Gas + Digital Circuits + RF Trisistors

背景知识:

半导体行业是政策、情报、组织管理、资本、智力、科技、工艺、设备都密集型。

半导体的生产研究涉及全球政治合作与竞争、产业与资本分布、高精尖科学工艺(精密化工, 尖端物理, 数学)、产业分工合作、组织管理、情报与科技交流严密等,

多为主权力量或产业资本组织高层次人才与资本直接或间接运营。

FET由\(\large V_{GS} 与 V_{DS}\)决定的"四个工作区":

注意: FET虽是"压控型器件", 但 "开启和关断速度"受 FET结电容 \(\large C_{GS}\)、\(\large C_{GD}\) 的"充放电速度"影响。因此"\(\large I{G}\)(驱动电流)必须保障一定的大小(查Datasheet)"。

- \(\large V_{GS} <= V_{GS(th)}\) 时,FET的"D-S沟道关断态", \(\large V_{DS}\)无作用。

- \(\large V_{GS} > V_{GS(th)}\) 时,FET的"D-S沟道导通态"(即使 \(\large V_{DS}=0,\ I_{d}=0\))。

- \(\large \bf{ V_{DS} < ( V_{GS} - V_{GS(th)} ) }\) 为“非饱和: 可变电阻区”

\(\large V_{GS}\)一定时, \(\large \bf{ R_{DS} }\ 几乎不因\ V_{DS}\ 而变化\), \(\large I_{d}与V_{DS}是线性关系\)(恒阻特性) - \(\large \bf{ V_{DS} > ( V_{GS} - V_{GS(th)} ) }\) 为“饱和: 恒定电流区”

\(\large V_{GS}\)一定时, \(\large \bf{ I_{d} }\ 几乎不因\ V_{DS}\ 而变化\), \(\large R_{DS}与V_{DS}是线性关系\)(恒流特性)

- \(\large \bf{ V_{DS} < ( V_{GS} - V_{GS(th)} ) }\) 为“非饱和: 可变电阻区”

- 击穿区 : \(\large \bf{ V_{DS} > V_{V(BR)DSS} }\).

0. 科学知识

电荷: 空穴(正电荷),电子(负电荷),施加电压可操控电荷的有序(方向与流通量)移动。

电流: 空穴(正电荷) 或/和 电子(负电荷) 有规律的移动将形成电流通路(电荷流通),

并且电流大小与总电荷流量成正比。

半导体材料与工艺:

常见的半导体材料主要包括硅 (Si)、锗 (Ge)、砷化镓 (GaAs)和磷化铟 (InP)。

硅是最广泛使用的半导体材料,大多数集成电路的主材料; 优点是自然资源丰富,产业链完善,生产工艺成熟。

掺杂: 一种半导体工艺,改变材料的电阻微观物理配方配比,组成有特殊物理性质的新村料。

即使同一类半导体也有许多生产商销售的多种型号,它们的区别多为材料、工艺、规格、批次、产商。

沟道:一种半导体工艺,在导电衬底上化学刻制两个可填充沟道,填充N型或者P型半导体

PN结二极管是半导体的分析的最小单位 ,由P(Positive)型半导体与N(Negative)型半导体形成PN结时:

P型半导体掺杂, 会带有大量的空穴(正电荷);

N型半导体,带有更多活跃电子(负电荷);

1 二极管--PN结

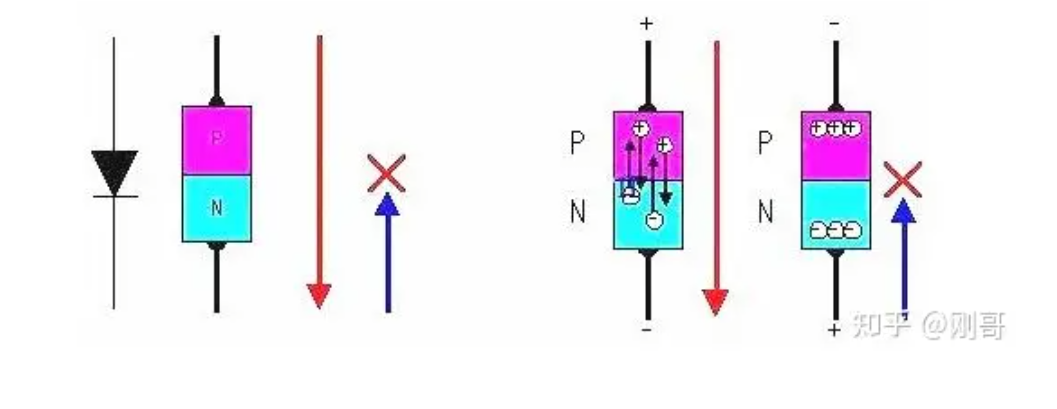

我们先说明仅含有一个P–N结的二极管的工作过程:

当在二极管加上正向电压(P端接正极, N端接负极)时,PN结导通,有电流通过。

这是因为在P型半导体端为正电压时:

N型半导体端的负电荷(电子), 受电压而涌向P型半导体端,

P型半导体端的正电荷(空穴), 受电压而移向N型半导体端,

因而形成PN结导通的电流(电荷流动)。

同理,当二极管加上反向电压(P端接负极,N端接正极)时,P型半导体端为负电压:

正电荷聚集在P型半导体端,负电荷则聚集在N型半导体端,

电荷不移动,其PN结没有电流通过,二极管截止。

[PDF] TI Docs.: Trade-offs Between CMOS, JFET, and Bipolar Input Stage…

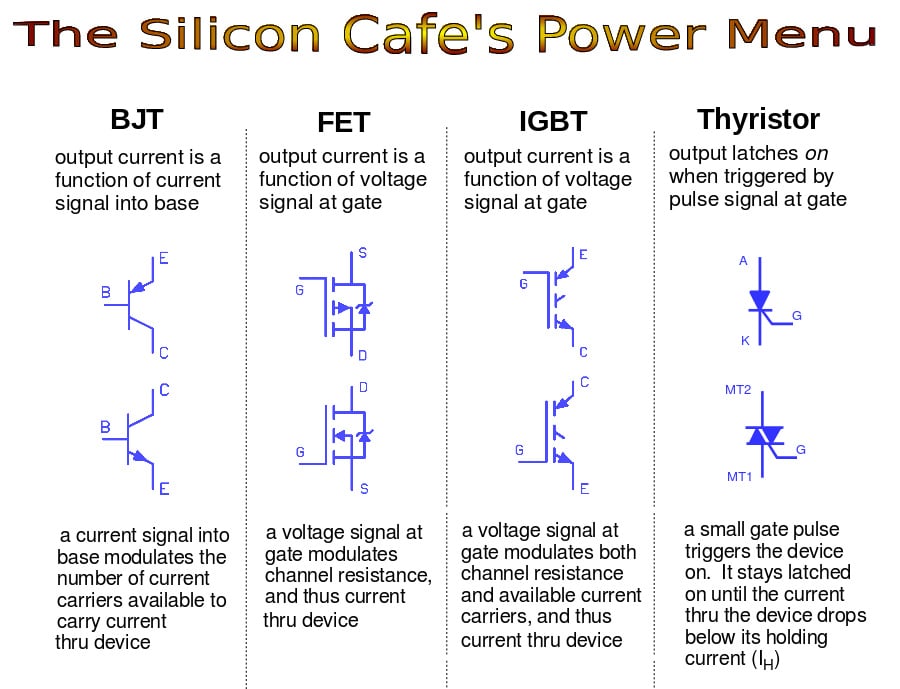

BJT(Bipolar Junction Transistor, 三极管):

BJT(三极管)的导电既有多数载流子,又有少数载流子,故称为双极型三极管;

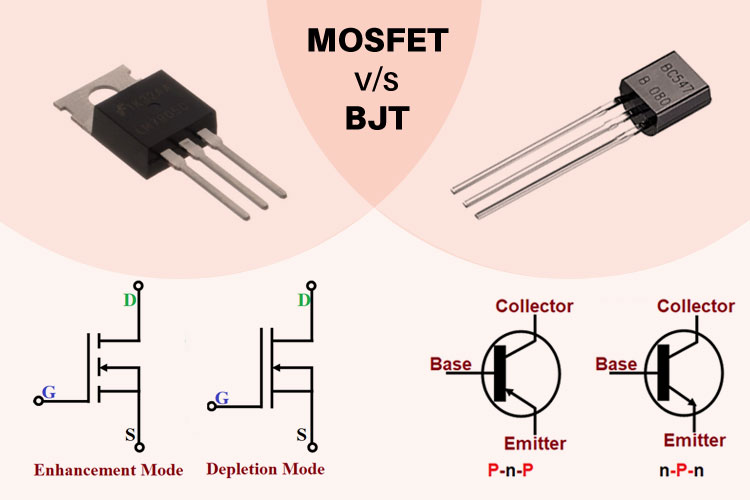

BJT按结构分PNP和NPN型两种;

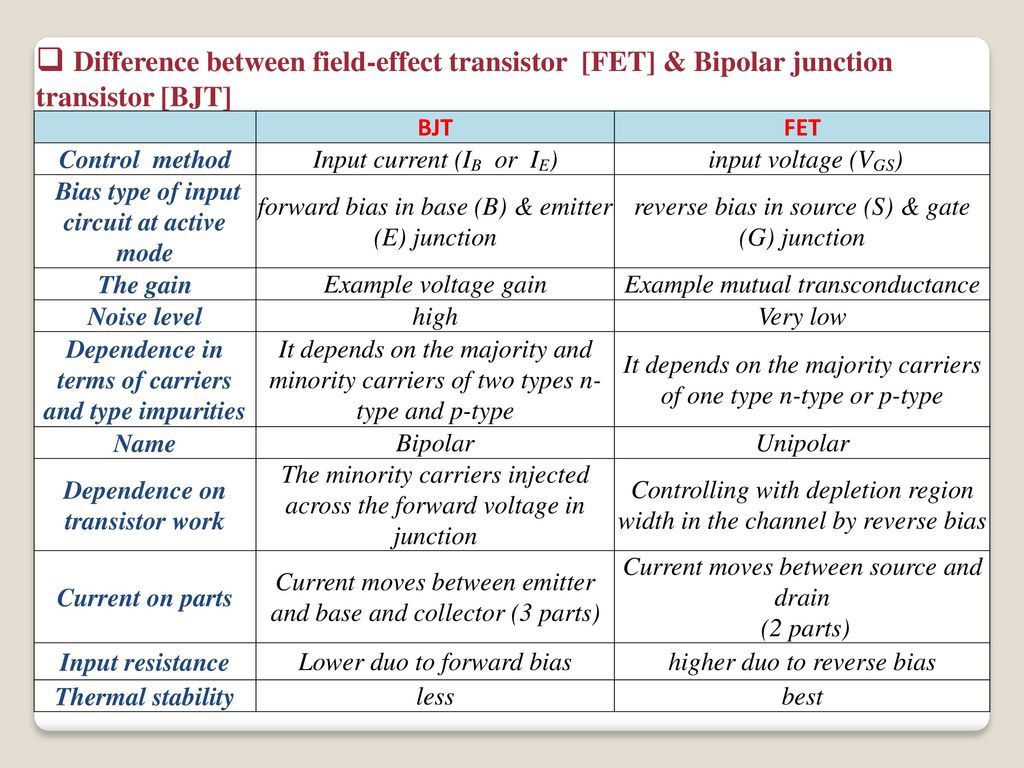

场效应管(FET) 与 三极管(BJT) :

- 历史背景时代: 早先发明的是BJT,以其优异性能迅速代替电子管, 也发现一些应用领域的问题;而FET是在BJT的基础上长斯研究而生的新一代,但并没有完全取代BJT,少数方面不如BJT,实际上两种都应用非常广。

- 总体性能比较: 新一代的FET总体要明显更优(调制的效率、频率、抗噪及渔温度稳定度),只要电路设计合理,采用场效应管会明显提升整体性能。

- 应用调制区别: FET以电压调制代替BJT的电流调制,尽管两种调都用到电压和电流,对比上有高低大小不同。但总体原理上:

三极管通过电流的大小控制输出,输入消耗功率比较的大。

场效应管是通过输入电压控制输出,输入消耗功率比较的小。

- 电流成因与电流调制原理:

- 电流成因:

形成电流的有多子(Majority Carrier多数载流子) 与少子(Minority Carriers少数载流子), 但少子的浓度受温度、辐射等影响较大.

BJT(三极管)的导电既有多子, 又有少子,故称为Bipolar(双极型)三极管;

FET(场效应管)导电只有多子,故又称为Unipolar(单极型)三极管。

所以场效应管比三极管的温度稳定性好、抗辐射能力强、噪声系数很小。在环境条件(温度等)变化很大的情况下应选用场效应管。

2.电流调制:

JFETs / MOSFETs | NXP Semiconductors

JFET用PN结反向电压改变导电沟道宽窄, 而调制Drain漏极电流;

MOS FET用栅源电压改变PN结表面感生电荷的多少,而调制Drain漏极电流。

FET(场效应管)的作用

- FET可以用作电子开关、可变电阻、恒流源、放大器Amplifier、Analog and Digital electrical circuits、特别是新一代数字电路大多是用FET元……。

- FET Amplifier的输入阻抗极高,耦合电容可较小,不必使用电解电容耦合。极高的输入阻抗也非常适合作为阻抗变换。常用于多级放大器的输入级作阻抗变换。

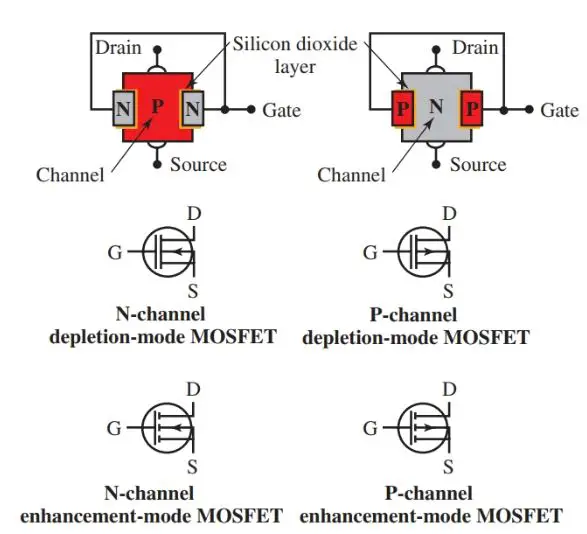

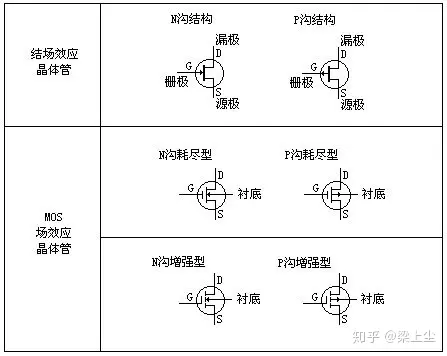

**FET(场效应管)的分类*:

-

FET种类多,按导电沟道分N型和P型,

![]()

-

按原理结构分JFET和JGFET(绝缘栅场效应管),

JFET(结型场效应管)有两个PN结;

JGFET(绝缘栅极型场效应管) 是 Gate栅极与其它电极完全绝缘。

而JGFET应用最多的一种子分类是MOS FET(简称MOS管, 金属-氧化物-半导体场效应管),

MOS FET管根据导电方式的不同,

又分CMOS(Enhancement Mode增强型)、Depletion Mode(耗尽型)两种;

CMOS(Enhancement Mode增强型)指: 当Vgs=0时 Idss=0 即FET截止状态;加上Vgs>0后FET导通有电流Id(多数载流子被引到Gate栅极), 从而“增强”了该区域的载流子,形成导电沟道。

Depletion Mode(耗尽型) MOSFET指; 当Vgs=0时, Idss>0即有形成导电沟道;加上Vg>0后, 使Idss=0即FET转向截止(使多数载流子流出沟道,因而“耗尽”载流子而止)。

3.还有PMOS、NMOS和VMOS功率场效应管,以及最近刚问世的πMOS场效应管、VMOS功率模块等。

![]()

场效应管的参数 (DS: Drain-Source)

场效应管的参数很多,包括直流参数、交流参数和极限参数,但一般使用时重要参数有:

- Idss — 饱和DS电流: 是指结型或耗尽型绝缘栅场效应管,栅极电压Ugs=0时的DS电流.

- Ut — 开启电压: 是指CMOS(增强型绝缘栅场效管),使DS间刚导通时的栅极电压。

- Up — 夹断电压: 是指结型或耗尽型绝缘栅场效应管,使DS间刚截止时的栅极电压。

- gM — 跨导: 是表示栅源电压Ugs— 对漏极电流Id的控制能力,即漏极电流Id变化量与栅源电压Uds变化量的比值。gM 是衡量场效应管放大能力的重要参数。

- BUds — DS击穿电压: 是指栅源电压Ugs一定时,场效应管正常工作所能承受的最大DS电压。这是一项极限参数,加在场效应管上的工作电压必须小于BUds。

- PDSM — 最大耗散功率。也是一项极限参数,是指场效应管性能不变坏时所允许的最大漏源耗散功率。使用时,场效应管实际功耗应小于PDSM并留有一定余量。

- IDSM — 最大漏源电流。是一项极限参数,是指场效应管正常工作时,漏源间所允许通过的最大电流。场效应管的工作电流不应超过IDSM.

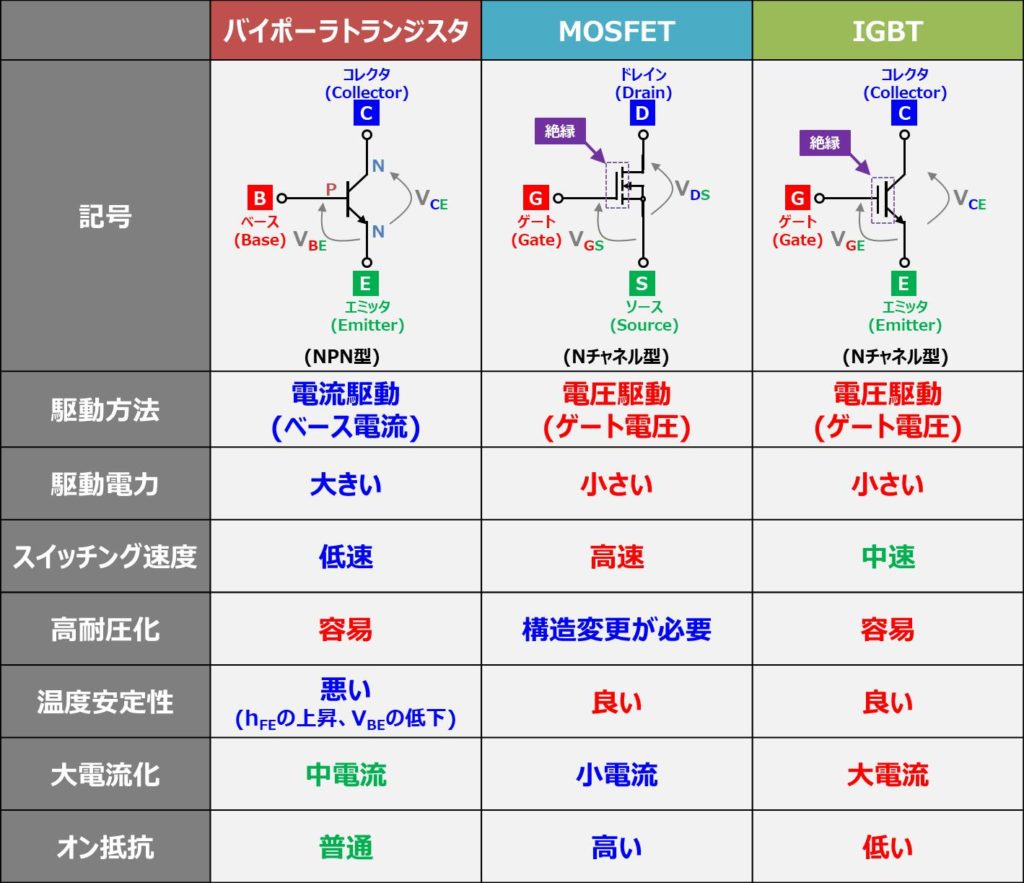

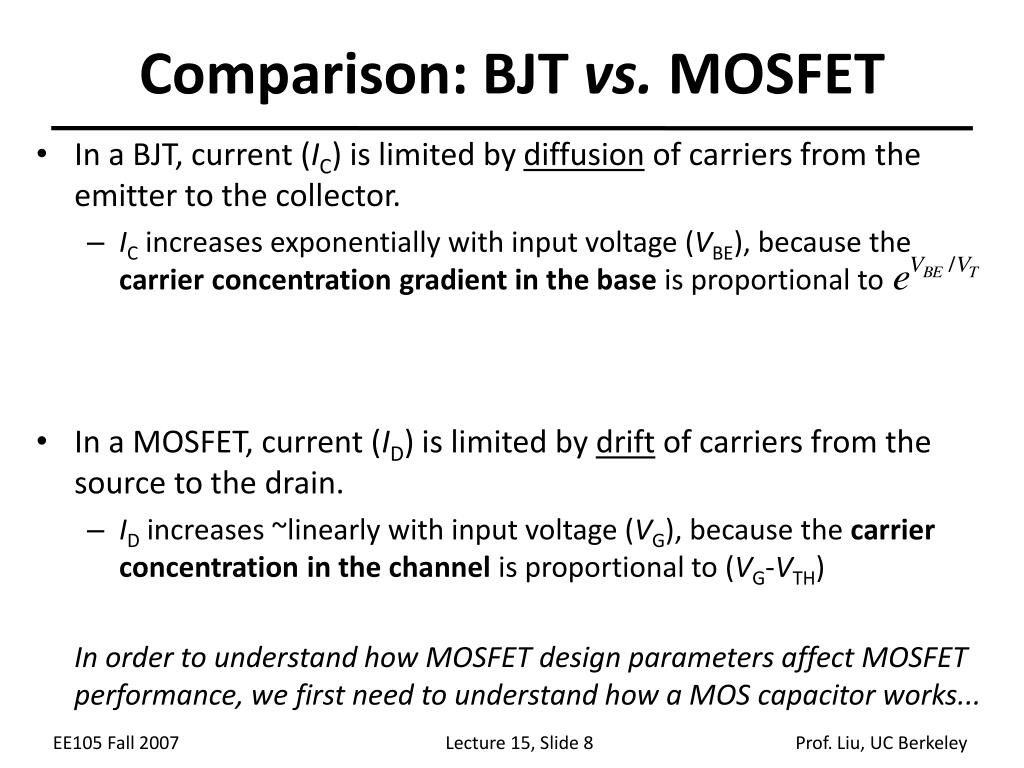

通过对比全面认识BJT(三极管)和FET(场效应管):

0. 电极区别:

三极管有Base(基极b)、Emitter(发射极e)、Collector(集电极c)三个电极;

FET场效应管也有Gate(栅极g)、Source(源极s)、Drain(漏极d)三个电极,

它们二者有对应关系,电极的作用相似,即基极-栅极都是控制极,发射极对应源极,集电极对应漏极;

- 分类差别:

BJT按结构分PNP和NPN型两种;

而场效应管种类多,按导电沟道分N型和P型,参考上文的“FET(场效应管)的分类”一节。 - 电容差别:

BJT三极管极间电容较大, 耦合电容较大, 输入阻抗较低。

MOS管极间电容较小, 耦合电容较小,输入阻抗极高。 - 阻抗差别:

三极管输入阻抗较低,在几百欧姆-几千欧姆之间,基极电流较大,输出电阻较高,对前级电路影响较大,阻抗不匹配时几乎不能工作;

场效应管的输入阻抗极高,达到兆欧以上,MOS管更高,栅极几乎没有电流,对前级电路影响较小,和三极管一样输出电阻也较高; - 灵活性差别:

三极管的发射极、集电极不能互换,否则β极低,不能正常工作,

场效应管对于一些特定条件的(衬底没有和源极连着一起),源极和漏极是可以互换的。耗尽型的场效应管的栅极电压可正可负,灵活性高; - 接法差别:

三极管有三种接法:共射、共基、共集,

场效应管也有三种接法:共源、共栅、共漏接法;

二者对应;phase关系一致; - 判别差别:

三极管仅有两种,判别上比较简单,焊接存储只要求防止温度过高即可,没静电影响;

场效应管类型多,判别上较为复杂,MOS管必须对栅极和源极放电,严防感应静电击穿,在存储、运输时必须将栅极、源极短路; - 载流子差别:

三极管有两种载流子导电,即少子与多子,属于双极性器件;

场效应管只有一种载流子参加导电,属于单极性器件;

体现在稳定性上差别:三极管由于少子也参与了导电,而少子容易受到温度的影响,热稳定性较差,故其噪声高,且制造复杂;场效应管由于其由多子导电,热稳定性较好,故噪声小;制造工艺简单,容易集成、功耗低、体积小、安全工作区域广;大规模、超大规模集成电路均大多由场效应管制作; - 偏置差别:

三极管正常工作需要合适的偏置电流;

场效应管正常工作时需要合适的偏置电压; - 控制类型:

三极管是电流控制型器件,也就是通过基极电流的变化控制集电极电流的变化;

场效应管属于电压控制型器件,也就是通过栅极电压的变化来控制(改变导电沟道的宽度)源漏极电流大小; - 特性曲线差别:

三极管分截止区、放大区、饱和区、击穿区;

场效应管分截止区、放大区、可变电阻区、击穿区,

二者有对应关系;在特性曲线上均有输入、输出特性曲线;

从电路分析计算,场效应管较三极管简单;

三极管的转移特性(IC-Vbe)是按指数规律变化,

场效应管的转移特性是按平方规律变化,

因此场效应管的非线性失真比三极管大; - 放大能力:

表征三极管放大能力的重要参数是电流放大倍数β,

场效应管用跨导表示gm,其值较小,放大能力差,电压放大倍数小于三极管电路; - 其它差别:

三极管和场效应管都可以作为可变电阻、开关器件;

三极管的功耗较高,但较便宜;在信号电压较低, 允许取用电流较高的,选用三极管。

场效应管功耗极低,对信号源取较少(高输出阻抗)电流,达到阻抗匹配,适用低噪高输入电阻的前置电路;

场效应管作为开关管的效率较高,多用在大电流、高速开关电源上;

在环境温度变化较大的场合应使用场效应管。

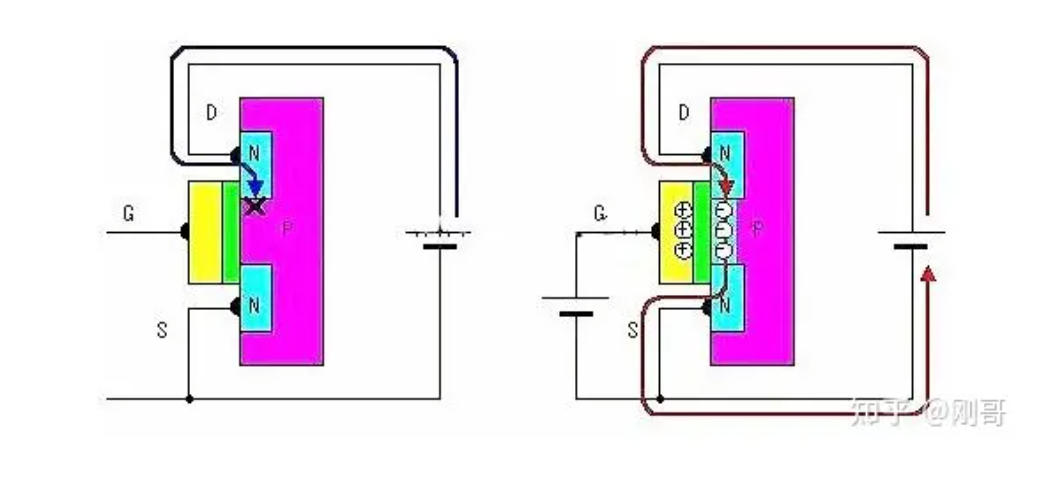

2 MOS FET工作原理(场效应管是电压驱动类, 三极管是电流驱动类 )

MOS FET(Metal Oxide Semiconductor Field Effect Transistor(金属氧化物半导体场效应管), 简称MOS 场效应管 或 MOS管。一般有耗尽型和增强型两种。后文以CMOS(增强型MOS)为例分析。

场效应管由Source(源极),Drain(漏极),Gate(栅极)三个电极使用,由于导电衬底的掺杂不同可分为N沟道和P沟道场效应管。

如上图所示,我们将Drain(漏极)接到电源正极,Source(源极)接到电源负极。

FET截止状态: 上图左, 是因为Gate(栅极)没有电压,Source(源极)和Drain(漏极)之间相当于两个背靠背的二极管,不会有电流流过。

加电待通状态: 当Gate(栅极)加上电压,并小于其阈值Vgs(th)时,Gate(栅极)和衬底P(Plate)之间会由于电场的作用,将P(Positive)型半导体中的空穴推开,此时N型半导体的Source源极和Drain漏极的负电子被吸引出来而涌向Gate(栅极),但由于氧化膜的阻挡,使得电子聚集在两个N沟道之间的P型半导体。

随着Gate(栅极)电压的增大,Gate(栅极)附近的电子浓度会增加。

FET导通状态: 上图右,当Vgs超过其阈值Vgs(th)时,在Source(源极)和Drain(漏极)之间的N型半导体会形成一个电子通道。同时此时由于Drain(漏极)加有正电压,就可以形成Drain(漏极)到Source(源极)的电流。

我们也可以想像成为两个N型半导体之间为一条沟,Gate(栅极)电压的建立相当于为它们搭了一座桥梁,

Idss("桥的大小"即Drain到 Source的电流)由Vgs(栅极电压)的高低决定。因此FET管为电压控制性晶体管。

我们可以将MOS管想象成阀门,Gate(栅极)就像开关可以控制水流是否可以通过。

3. MOS FET的Generation

FET -> MOS FET -> CMOS FET-> SiC MOS FET -> GaN MOS FET

多代都在同时使用,每一代都有优缺点,与应用范围。

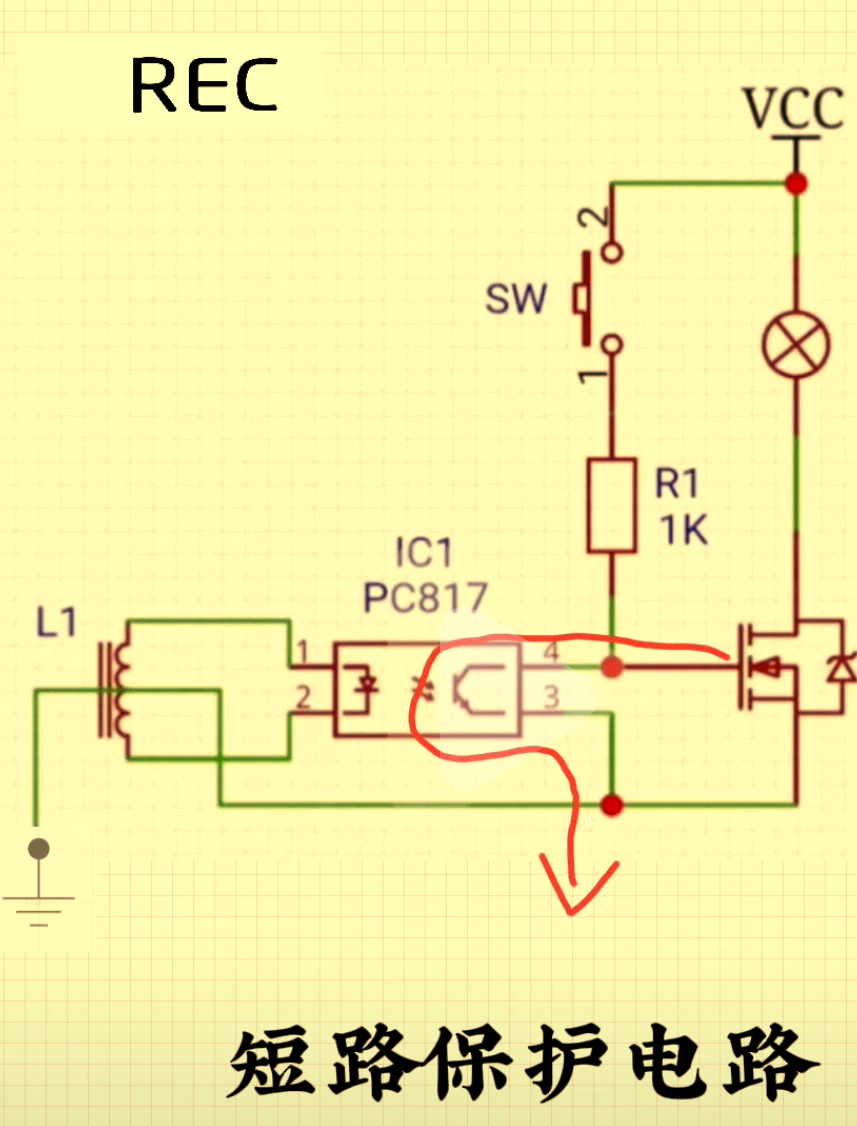

4. MOS FET的驱动控制

- 导通: 只要Vgs(th)达到则Idss形成,MOS FET导通;

- 截止: 正常时应取消Vgs(th)电压,MOS FET停止,

应急保护时可将Vgs(th)强制拉低(导流Vgs到G地), 断开Idss,

防止MOS FET过载(如短路、过热或过流时)。

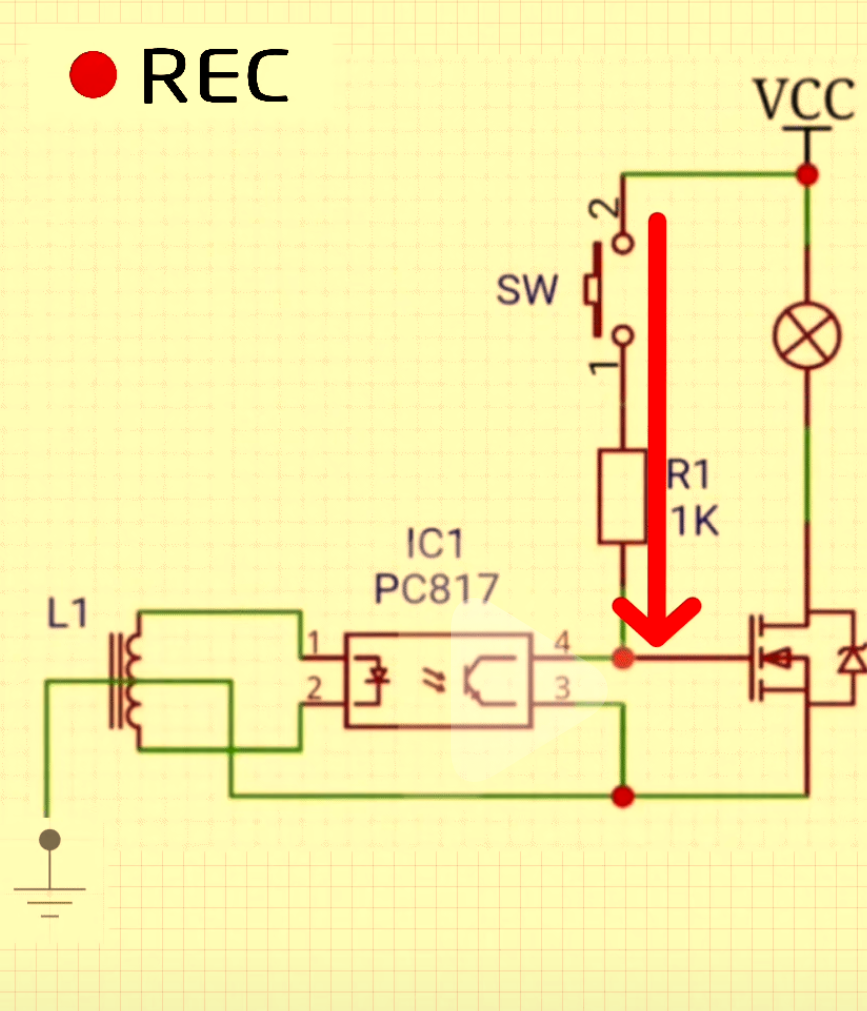

如下图:

(光电耦合能隔离高电压来驱动,应急保护地将Vgs(th)强制拉低以断开Idss防止MOS FET过载):

![]()

常用“Switching Power”的驱动控制原理: 就是将上图的SW开关换用光电耦合来驱动,就能施电压达到Vgs(th)拉高, 能形成Idss使MOS FET导通:

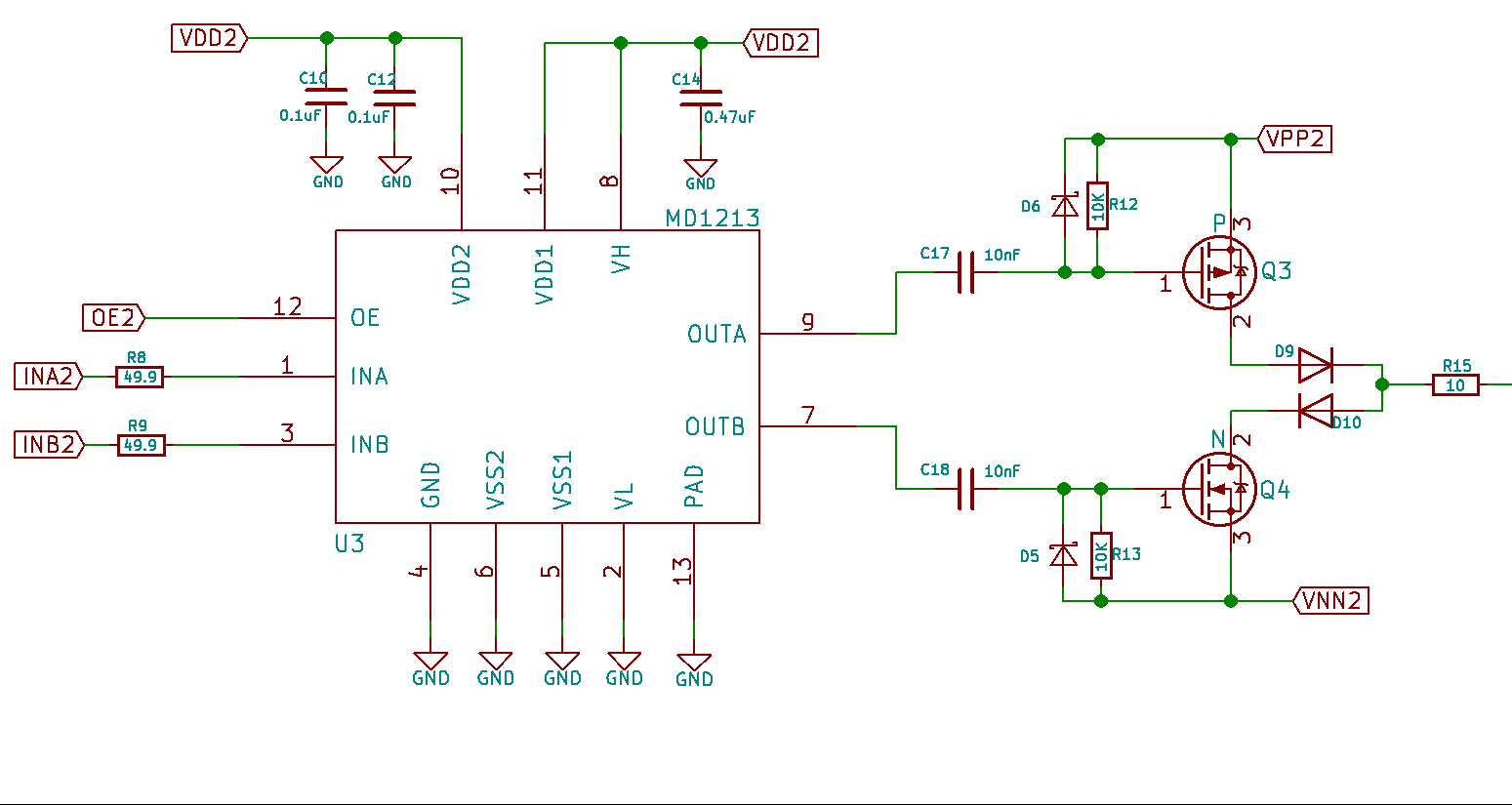

常用“Switching Power”的驱动控制原理: 推挽式 P型 与 N型 MOS FET双管驱动(电容耦合)电路实例:

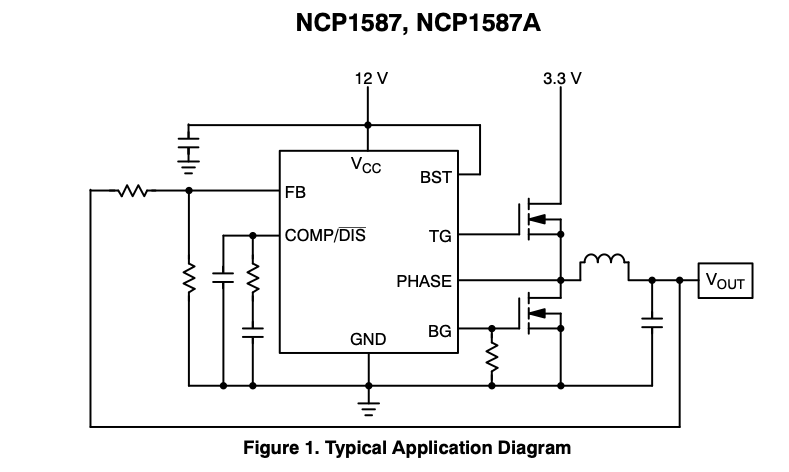

常用“Switching Power”的DC-DC直流大功率电压变换**:

以某 600W ATX 电源的12V-5V 和 12V-3.3V 的DC-DC电路为例(MOSFET: 两只060N03L推挽式,由Onsemi的NCP1587进行PWM调功原理图):

5. CMOS FET工作原理

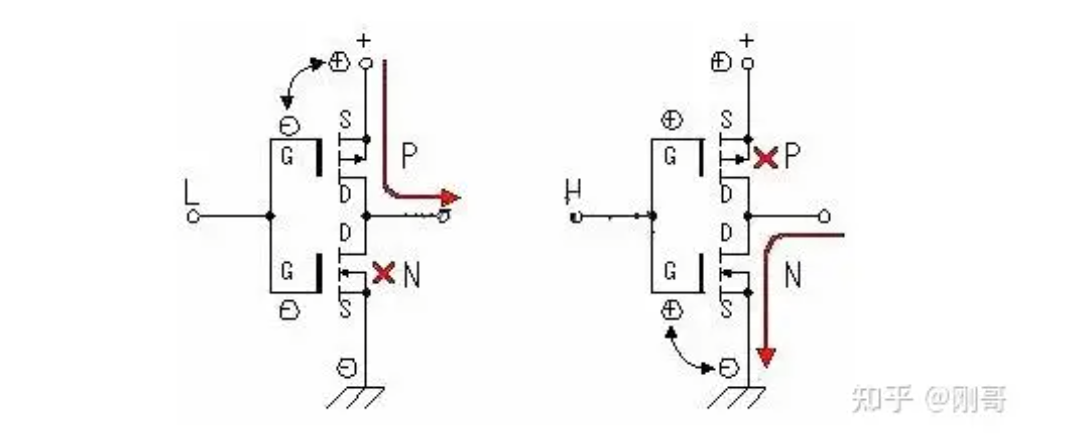

CMOS FET(增强型MOS场效应管), 电路将一个增强型P沟道MOS FET和一个增强型N沟道MOS FET组合使用。

如下图所示:

当输入端为L(低电平)时,P沟道MOS FET导通,输出端与电源正极接通。

当输入端为H(高电平)时,N沟道MOS FET导通,输出端与电源负极接通。

在数字电路上,制定电平(电压标准,多少伏特电压以上为高,多少伏特电压以下为低),

并且将CMOS FET输出端电压的高低判断为1和0,就实现通过数字逻辑控制电路状态及行为。

然后将所有的逻辑通过不同的逻辑规则组合就可以实现有目标的不同逻辑功能。

在数字芯片设计上,最终生产的最小单位就是MOS管,

通过将MOS管组合封装之后就是我们要的芯片。

Actually, switching speed comparation between Bipolar , CMOS and BiCMOS

can be verified by the current production of RF Trisistors and Switching Trisistors from the mainstream Semiconductor Suppliers, TI, ADI, Vishay, NXP, Infinion, STM, SONY, ROHM, TOSHIBA,...

RF Trisistors@Infinion:

https://www.infineon.com/cms/en/product/rf/rf-transistor/low-noise-rf-transistors/

Bipolar vs CMOS vs BiCMOS-Difference between Bipolar,CMOS,BiCMOS

compares Bipolar vs CMOS vs BiCMOS and mentions difference between Bipolar, CMOS and BiCMOS technologies:

Bipolar Technology

Following are the characteristics or benefits of Bipolar technology:

• Higher switching speed

• It offers high current drive per unit area and high gain

• Generally better noise performance and better high frequency characteristics

• It has better analogue capability compare to others.

• Improved I/O speed.

• It offers high power dissipation.

• lower input impedance (high drive current)

• low packing density.

• low voltage swing logic.

• It offers lower delay sensitivity to load.

• high gm (gm α Vin)

• It offers high unity gain bandwidth at low current

• They are basically unidirectional devices.

CMOS

Following are the characteristics or benefits of CMOS technology:

• It offers high noise margins.

• It has low static power dissipation compare to other technologies.

• It offers high packing density

• It offers high yield along with large integrated complex functions.

• It has low manufacturing cost per device.

• Scalable threshold voltage

• It has High input impedance and low drive current.

• It offers higher delay sensitivity to load (i.e. it has fan out limitation.)

• It has lower trans-conductance, here trans-conductance gm α Vin

• It has lower output drive current (This will have issue while driving higher capacitive loads)

• A near ideal switching device

• Bi-directional capability (drain & source are interchangeable)

BiCMOS

Following are the characteristics of BiCMOS technology:

BiCMOS combines both Bipolar and CMOS technologies in single IC.

As we know CMOS has merits over bipolar in areas of low power dissipation, large noise margins and greater packing densities.

Bipolar has merits over CMOS in areas of faster switching speed and large current cababilities.

浙公网安备 33010602011771号

浙公网安备 33010602011771号