组合逻辑电路总结

逻辑电路分类

- 组合逻辑电路: 无记忆功能,输出直接由当时的输入决定

- 时序逻辑电路: 具有记忆功能,输出不仅取决于当时的输入,还与过去的输入有关

组合电路的分析流程

- 确定电路结构为组合电路 。

- 逐级分析,或划分模块后分析。得到逻辑表达式或真值表 。

- 分析得到的逻辑表达式或真值表,得出电路的功能描述。

常用组合逻辑模块

译码器

将输入的某种代码(通常为二进制码),转换为事件或另一种代码输出的过程,称为译码。

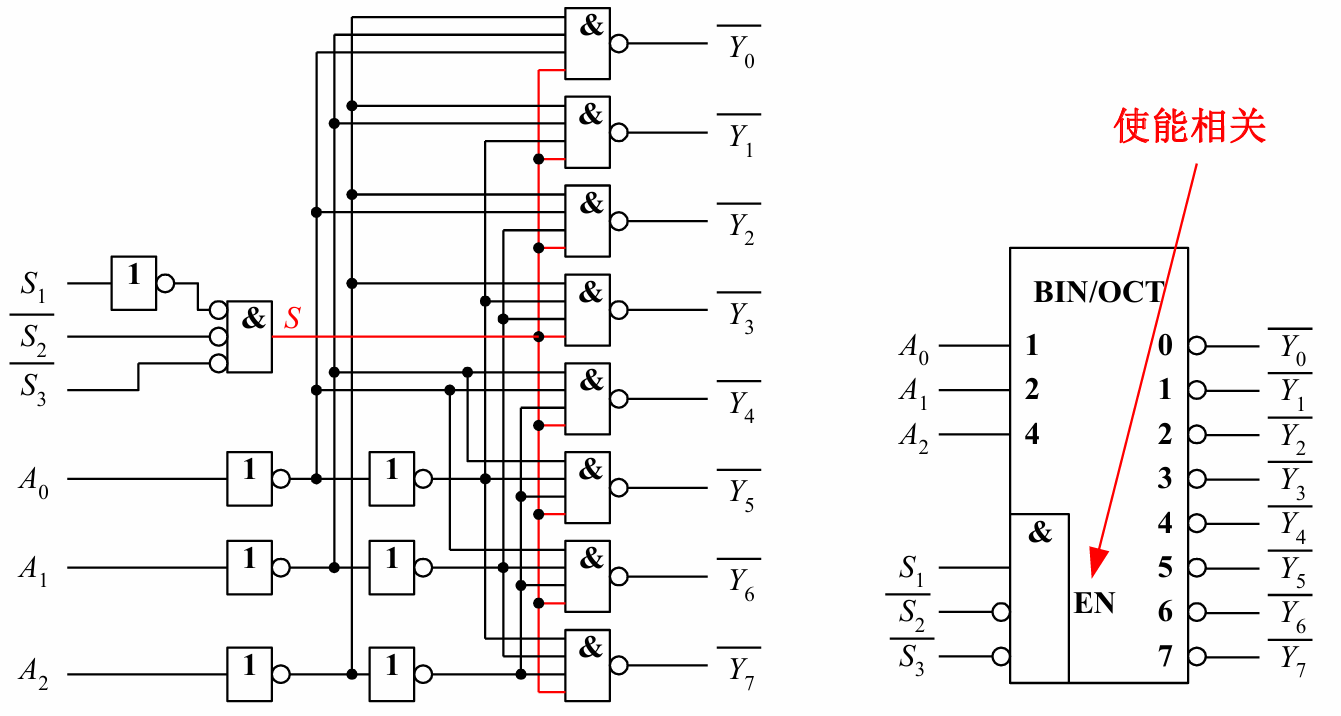

3-8译码器

- 其中 \(m_i\) 是由 \(A_2A_1A_0\) 组成的最小项

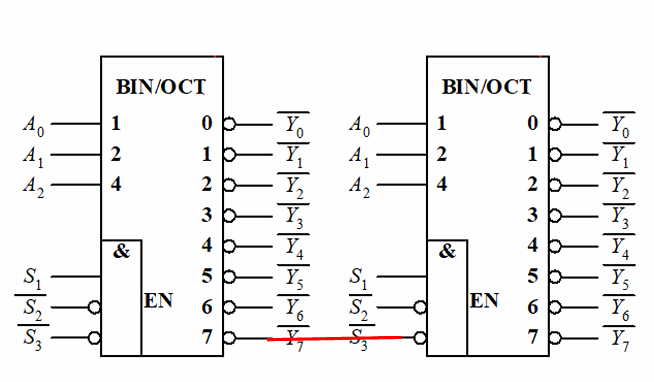

利用多个译码器扩展范围

- 两个3-8译码器,将第一个的输出连到第二个的控制端,得到一个4-16译码器。

可见当\(A_2A_1A_0 \not = 111\)时,左边的输出端起作用。当\(A_2A_1A_0=111\)时,右边的输出端起作用。

编码器

- 将输入信号(事件),用一个代码表示(输出) 的过程,称为编码。

- 编码器有普通编码器和优先编码器两种。

- 普通编码器在同一个时刻只能允许有一个输入 (单个事件)。

- 优先编码器允许多个事件同时发生,按照事先设定的优先级,确定输出代码。

- 编码器和译码器是逆过程。

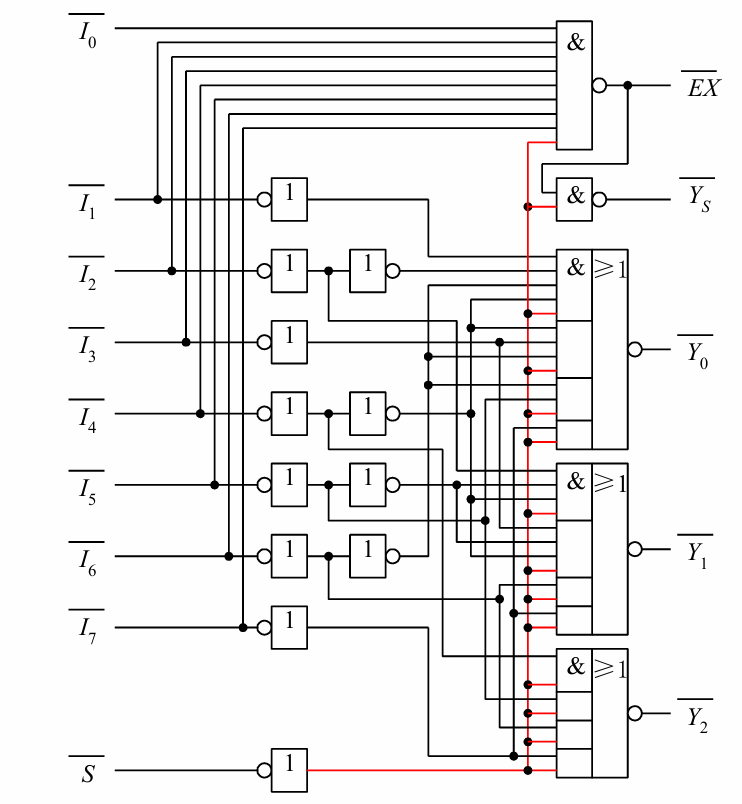

8-3优先编码器

其中 \(Y_{m_i}\) 为 \(Y_2Y_1Y_0\)组成的最小项\(m_i\)

- 真值表

| \(I_7\) | \(I_6\) | \(I_5\) | \(I_4\) | \(I_3\) | \(I_2\) | \(I_1\) | \(I_0\) | \(Y_2Y_1Y_0\) |

|---|---|---|---|---|---|---|---|---|

| 1 | x | x | x | x | x | x | x | 111 |

| 0 | 1 | x | x | x | x | x | x | 110 |

| 0 | 0 | 1 | x | x | x | x | x | 101 |

| 0 | 0 | 0 | 1 | x | x | x | x | 100 |

| 0 | 0 | 0 | 0 | 1 | x | x | x | 011 |

| 0 | 0 | 0 | 0 | 0 | 1 | x | x | 010 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | 001 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 000 |

- 扩展输出

只有当所有编码输入端都为高电平,选通输入为0(\(\overline S = 0\))时 。表示电路已选通,但没有输入。

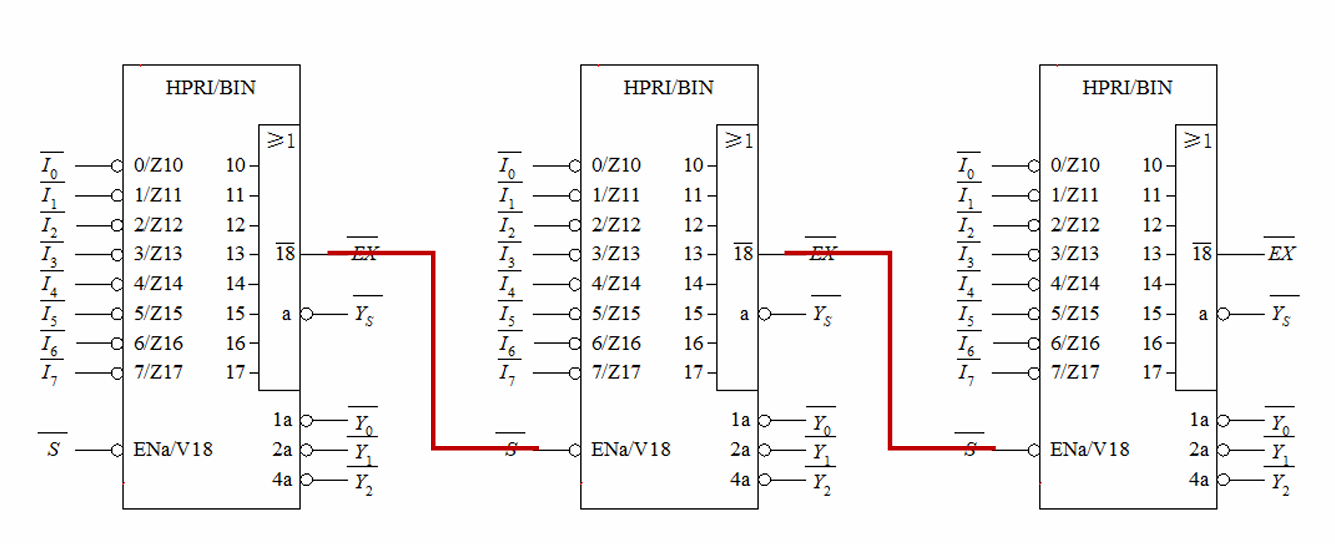

- 编码器扩展

数据选择器

从多个输入逻辑信号中选出一个逻辑信号送到输出端的器件,也称为多路器。

一个数据选择器连接\(m\)个输入和\(n\)个地址端(决定哪一个输入被送到输出端),有 \(m\le 2^n\)

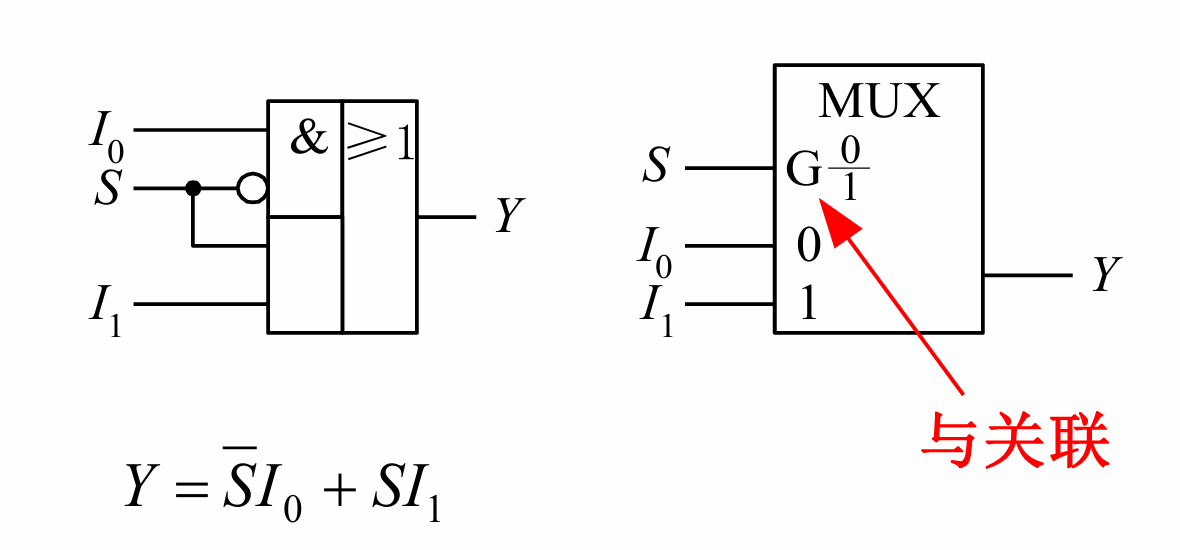

2选1数据选择器

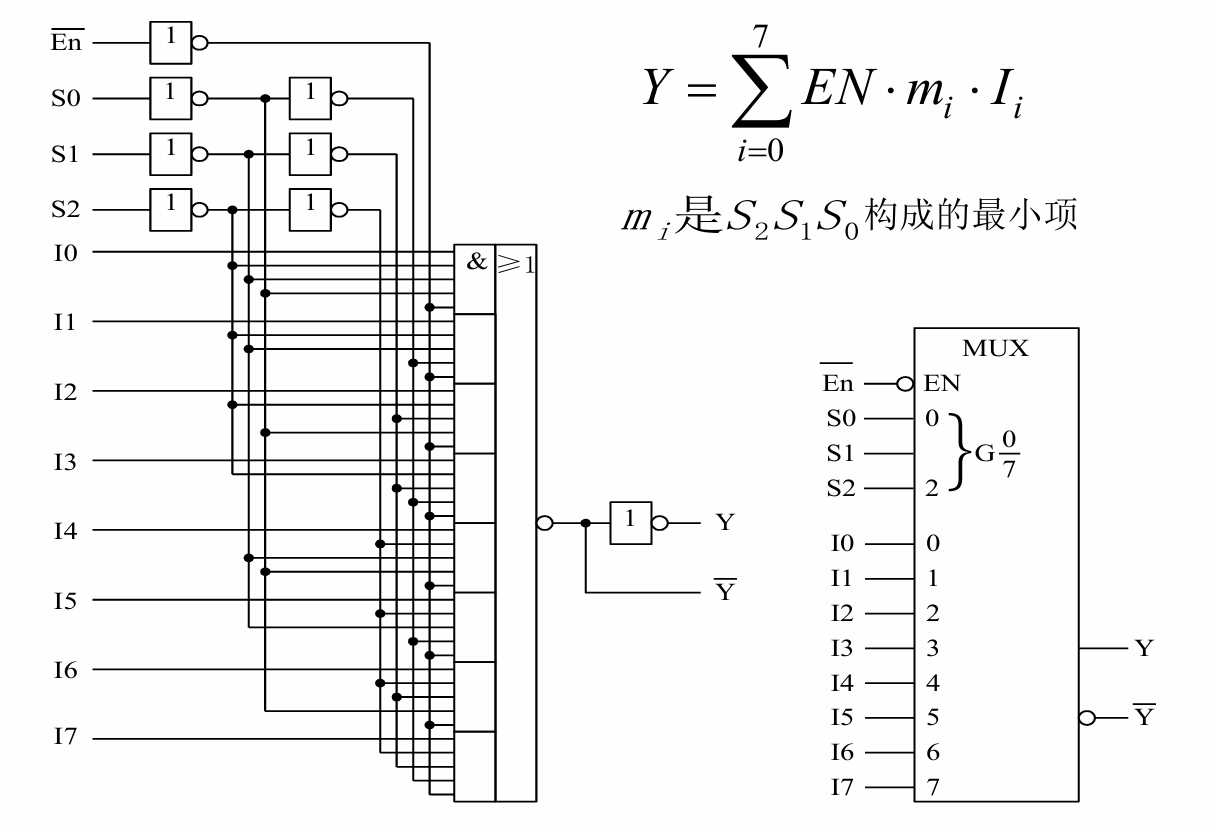

8选1数据选择器

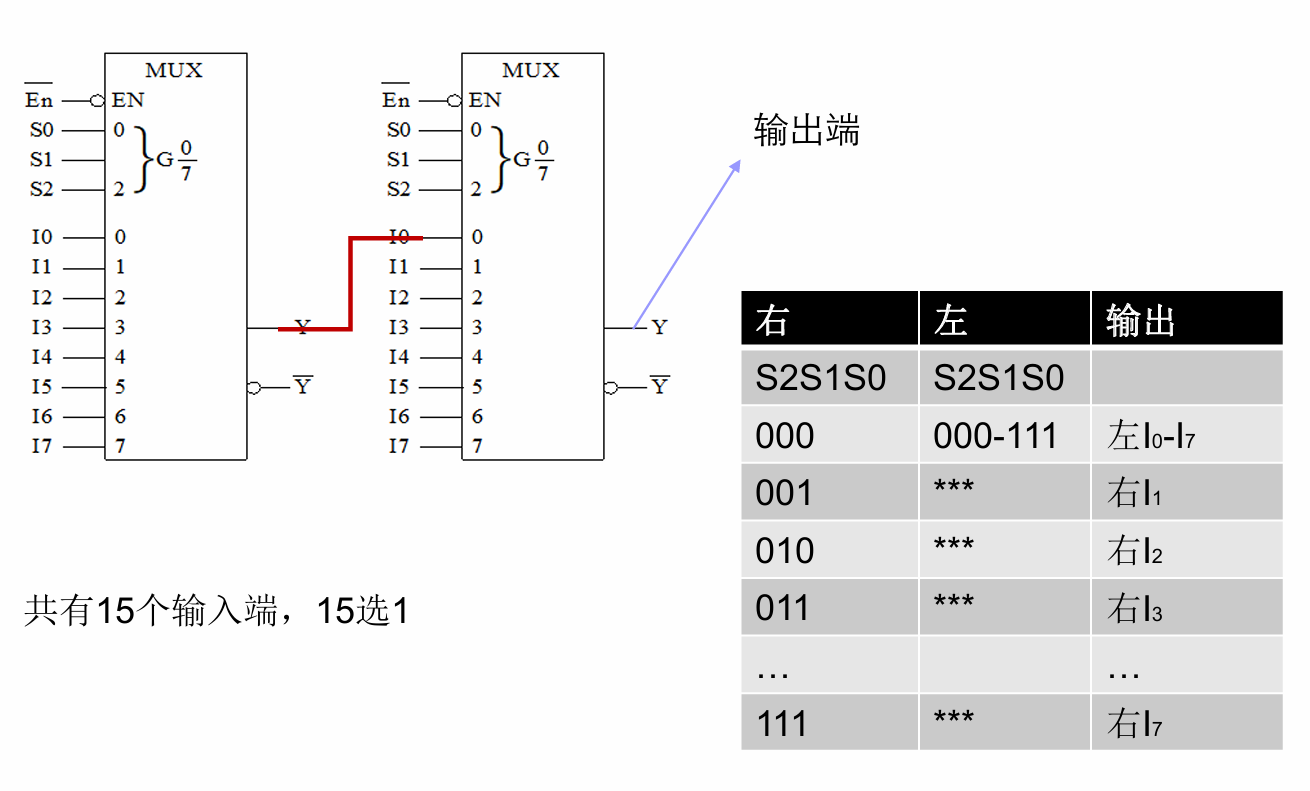

- 输入端扩展

组合电路设计流程

- 建立逻辑抽象。定义输入输出变量,确定输入输出关系。

- 写出真值表,建立逻辑函数表达式。

- 化简表达式。

- 画出逻辑图(电路图)。

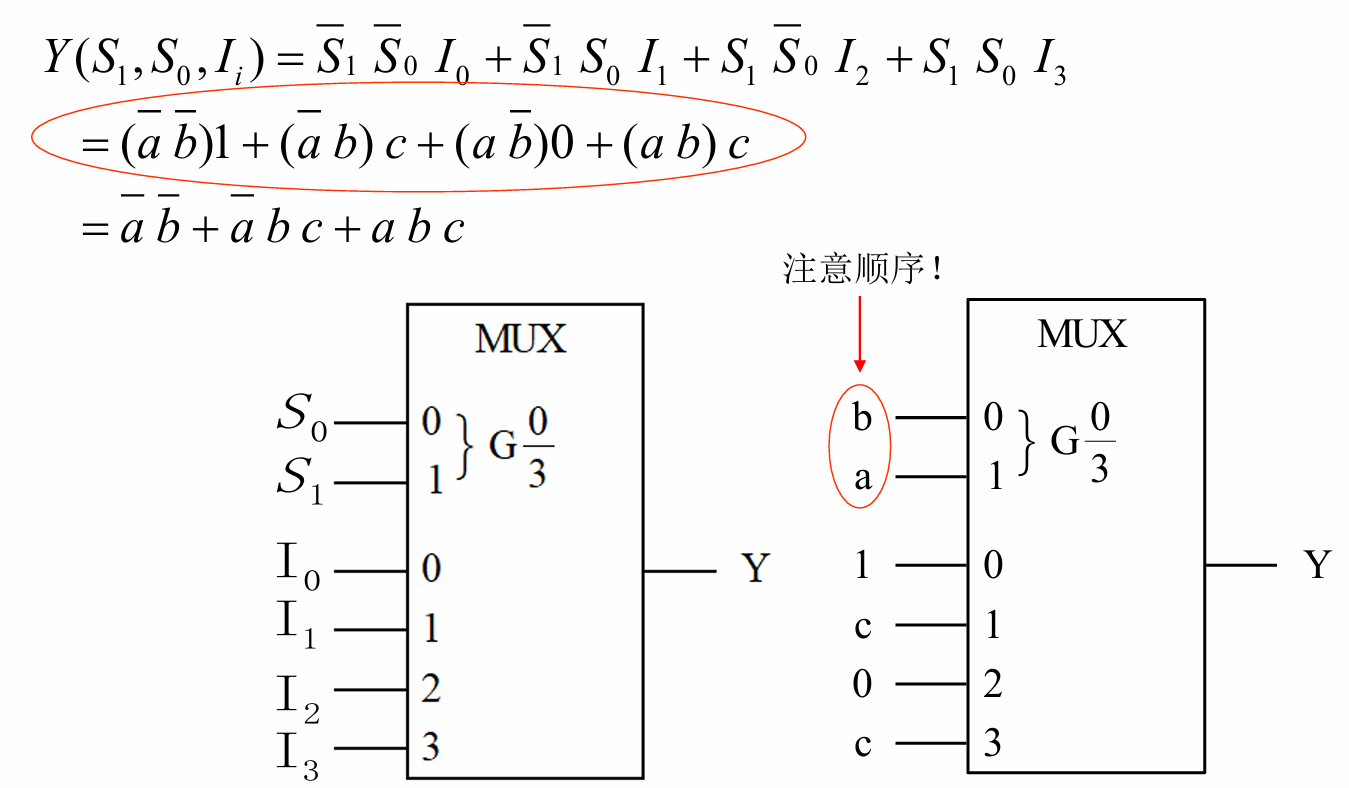

用数据选择器构建组合电路

将逻辑函数化为

的形式来使用数据选择器构造电路。

\(2^n\)选一的数据选择器可以构造有\(n+1\)个输入变量的逻辑函数。

- 如

有3个输入变量,可以将其中2个变量作为选择器的地址端,使用4选1数据选择器。

- 使用数据选择器构造函数的过程实际上与影射变量卡诺图类似,其中作为影射变量外的其他变量为数据选择器的地址端。

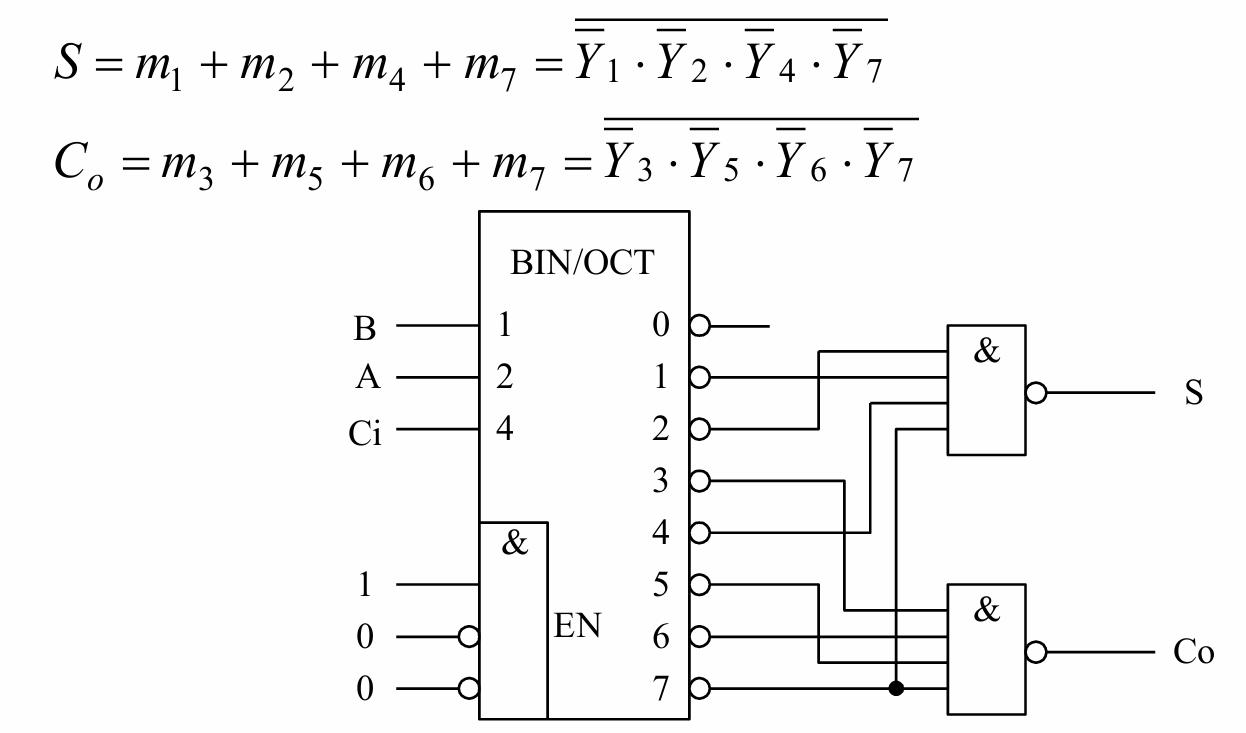

用译码器构建组合电路

由于译码器可以将二进制码转化成对应的事件,所以只要将逻辑函数化成含最小项的标准形式,将最小项对应的输出端连起来(由于输出时取反,所以最后使用与非门连起来实现或运算)即可。

加法器

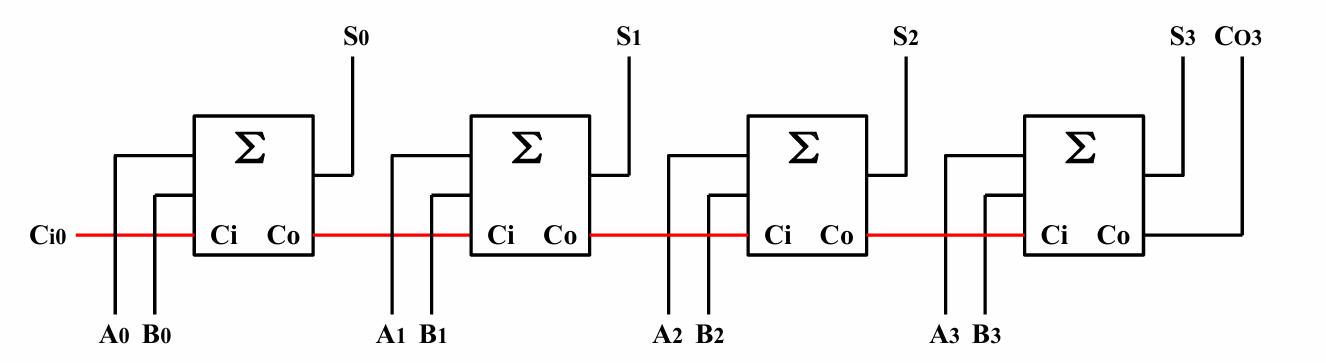

迭代设计

- 迭代设计思想:

将\(n\)个全加器连起来可以构造\(n\)位的加法器,但是时间代价会比较高,因为后面的全加器要等待前面的全加器运算完毕。

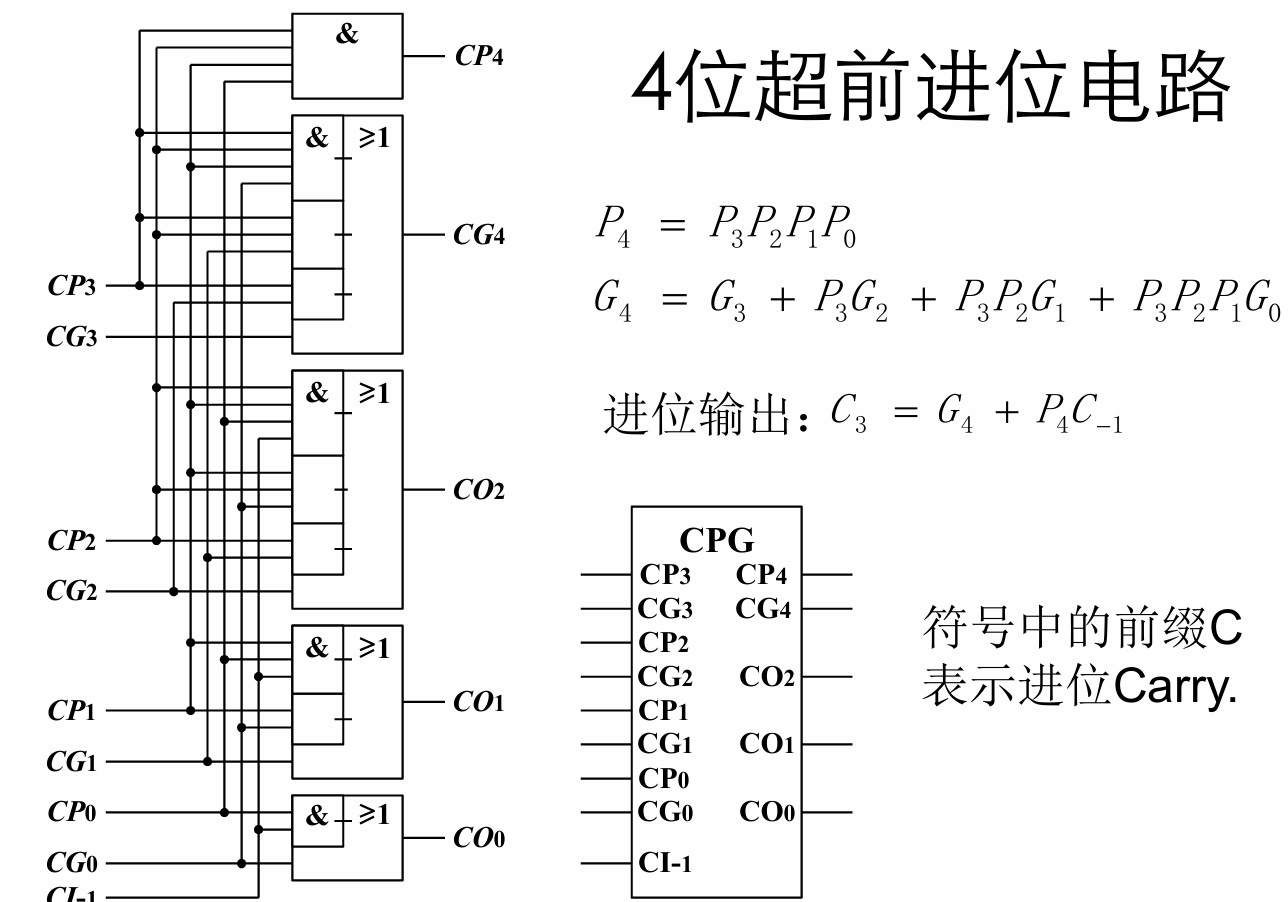

超前进位

- 进位产生信号:\(G_i=A_iB_i\)

- 进位传播信号:\(P_i =A_i+B_i\)

根据这个递推公式可以将任何\(C_i\)的表达式写成含有\(C_{-1},P_j,G_j (j\le i)\)的式子,由于这些组成部分在之前就已经计算过,所以确定了输入就可以确定\(C_i\),解决了延时问题。

数字集成电路的分类

按制作工艺的不同,数字集成电路分为两大类:

- 双极型(主要由晶体管构成):TTL(晶体管-晶体管逻辑电路),ECL(射极耦合逻辑电路)

- 单极型(主要由场效应管构成):CMOS(互补金属氧化物半导体),NMOS电路

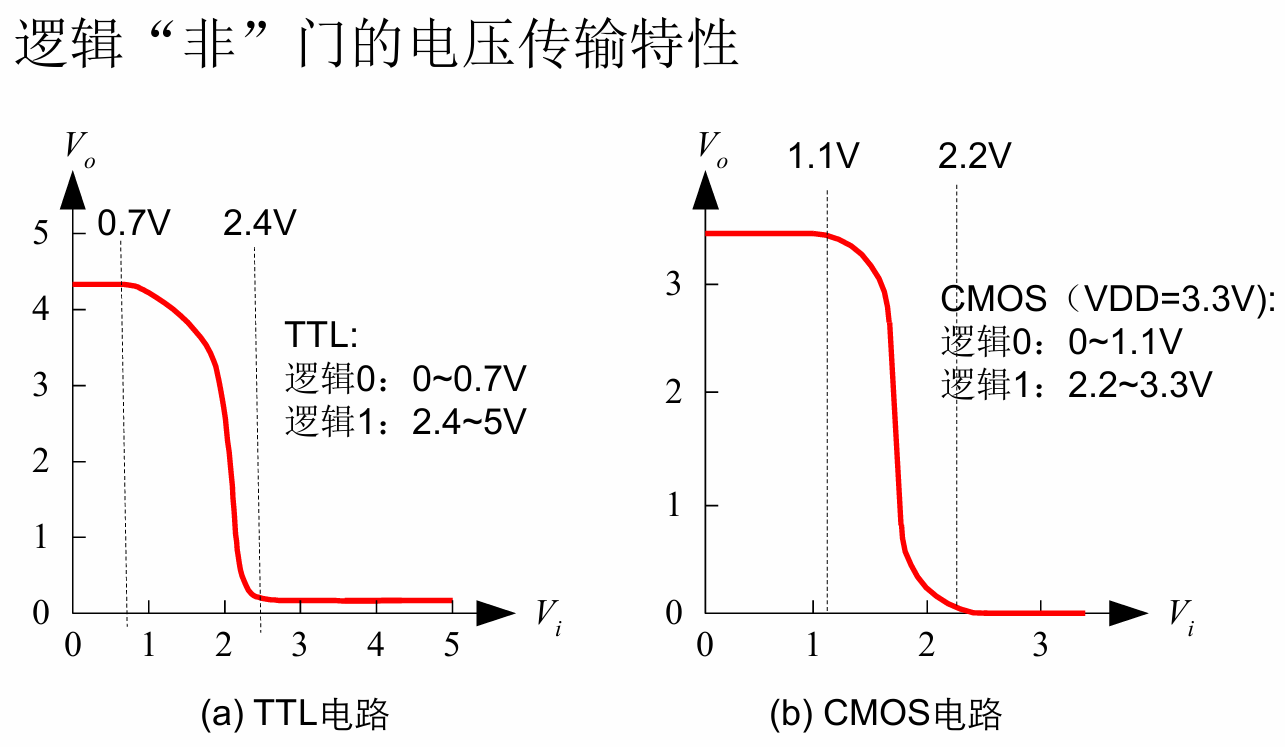

门电路的电压传输特性

- 门电路是数字集成电路的基本单元,门电路由更基本的二极管、晶体管、场效应管等半 导体元器件构成。

- 逻辑代数中用0、1表示二值逻辑的两个逻辑状态。 在实际电路中,以特定的电压范围来表示逻辑状态 ,该电压范围称为逻辑电平。

- 每个逻辑电平对应的电压具有一定的范围。当输入电压在一定范围内波动时,数字电路仍能正确区分输入的逻辑状态,因此数字电路具有一定的抗干扰能力

- 不同类型的数字电路可能具有不同的逻辑电平。(两种类型的电路连接时应考虑电平转换问题)

数字集成电路的静态特性

- 在实际的数字电路系统中,不可避免地会受到各种干扰和产生各种噪声,例如信号通过线路时会在线路上产生电压降,进而改变实际输入端的电平。 为了保证能正确地传输逻辑电平,数字电路的实际输出电压范围总是大于允许的输入电压范围。

- 参数:

- 最大允许输入(出)低电平\(V_{IL(max)}、V_{OL(max)}\)

- 最小允许输入(出)高电平\(V_{IH(min)}、V_{OH(min)}\)

- 噪声容限

- 低电平噪声容限:\(V_{NL} = V_{IL(max)}-V_{OL(max)}\)

- 高电平噪声容限:\(V_{NH} = V_{OH(min)} - V_{IH(min)}\)

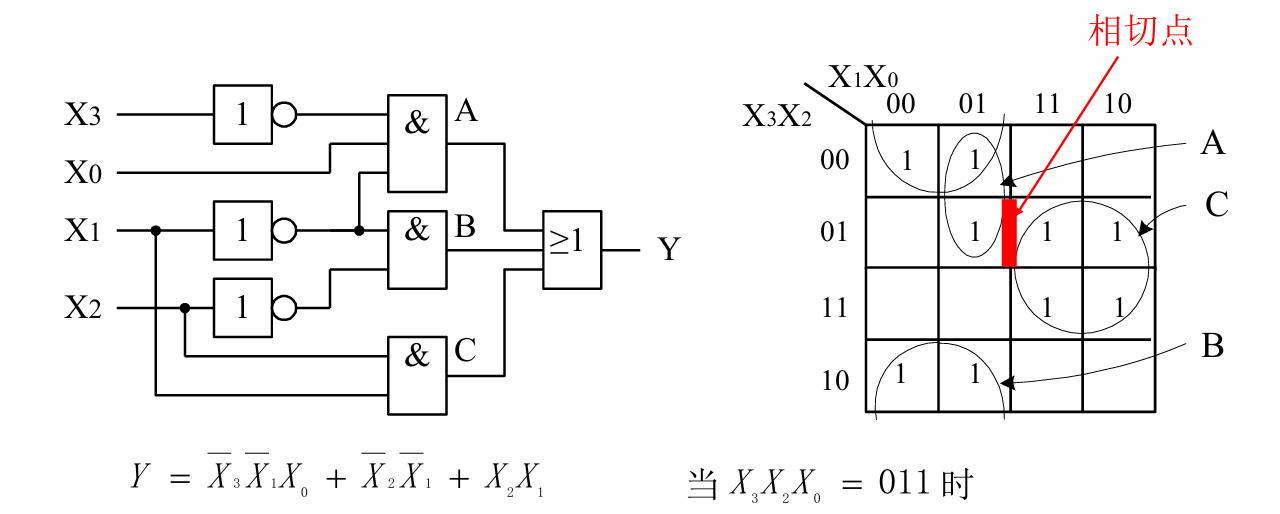

竞争与冒险

- 当一个门的输入有两个或两个以上变量发生改变时,由于这些变量(信号)是经过不同路径产生的,使得它们状态改变的时刻有先有后,这种时差引起的现象称为竞争。

- 竞争的结果若导致冒险(险象)发生(如毛刺),并造成错误的后果,则称这种竞争为 临界竞争;竞争的结果不导致冒险发生,或虽有冒险发生,但不影响系统的工作,则称这种竞争为非临界竞争。

- 从冒险的波形上,可分为静态和动态冒险。

- 输入信号变化前后,输出的稳态值是一样的,但在输入信号变化时,输出产生了毛刺,这种冒险称为静态冒险。若输出的稳态值为0,出现了正的尖脉冲毛刺,则称为静态0冒险;若输出稳态值为1,出现了负的尖脉冲毛刺,则称为静态1冒险。

- 输入信号变化前后,输出的稳态值不同,并在边沿处出现了毛刺称为动态冒险

检查竞争冒险

- 将输入转换为\(Y = A+\overline A\),或 \(Y = A \cdot \overline A\) 的形式。

- 在卡诺图上观察到相切的卡诺圈。

- 只有在每个瞬时只有一个输入发生状态改变的条件才适用。

- 如函数:

当$B=C=1$时,$F = \bar A +A$,电路可能出现险象

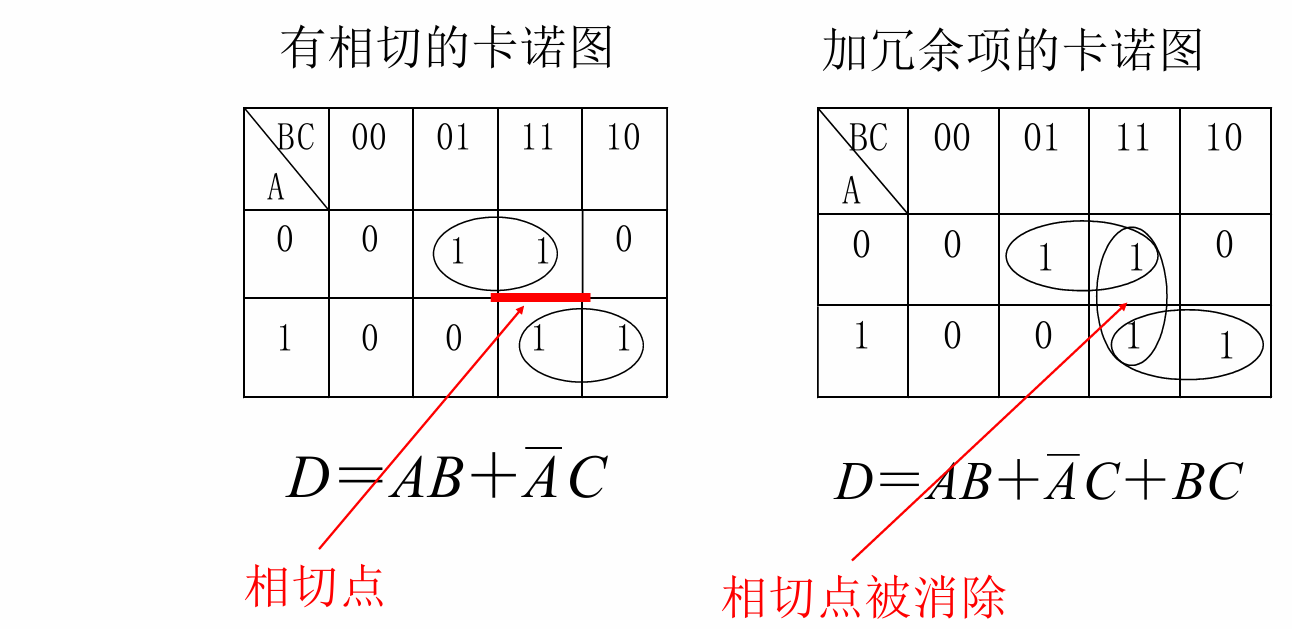

消除竞争冒险

增加冗余项消除冒险

- 消除相切的卡诺圈之间的相切点即可。

当\(B=C=1\)时,加冗余项之前,存在竞争冒险\(D = A + \bar A\),加完后\(D=A+\bar A + 1 = 1\),无竞争冒险。

浙公网安备 33010602011771号

浙公网安备 33010602011771号