从PT的报告中估算Tree长

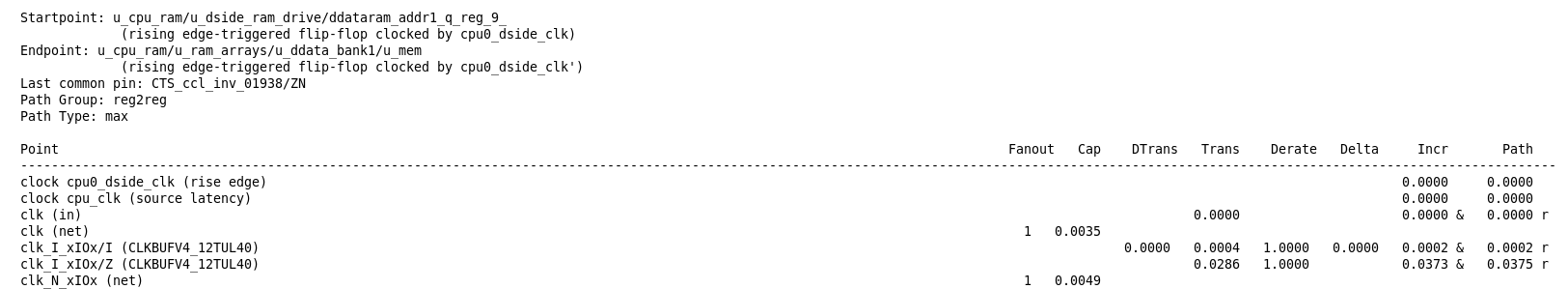

截取了PT报出来的一条reg2reg path,内容如下:

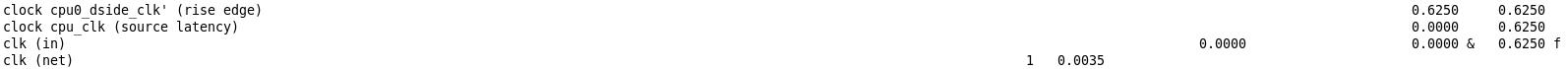

从图中可以看到时钟clk从source到第一个reg的CK端所用的时间是1.0323ns,时钟clk从source到SRAM的CLK端所用时间为(1.5652-0.625)/0.925=1.0164ns,由此可以计算出skew=1.0323-1.0164=0.0159ns,由此可见tree基本是平的。

需要注意的几个细节:第一是计算skew是看clk到reg/mem的时钟端口的时间,所以不要把多余的时间加上去。第二是时间起点问题,clk有从0时刻开始的,有从0.625ns开始的,到目标寄存器的ck端的时间应减去起点时间。第三是注意derate,这是根据signoff标准制定的悲观因子,需要用时间除以这个因子然后再对比skew。

浙公网安备 33010602011771号

浙公网安备 33010602011771号