具有快表的地址变换机构

具有快表的地址变换机构

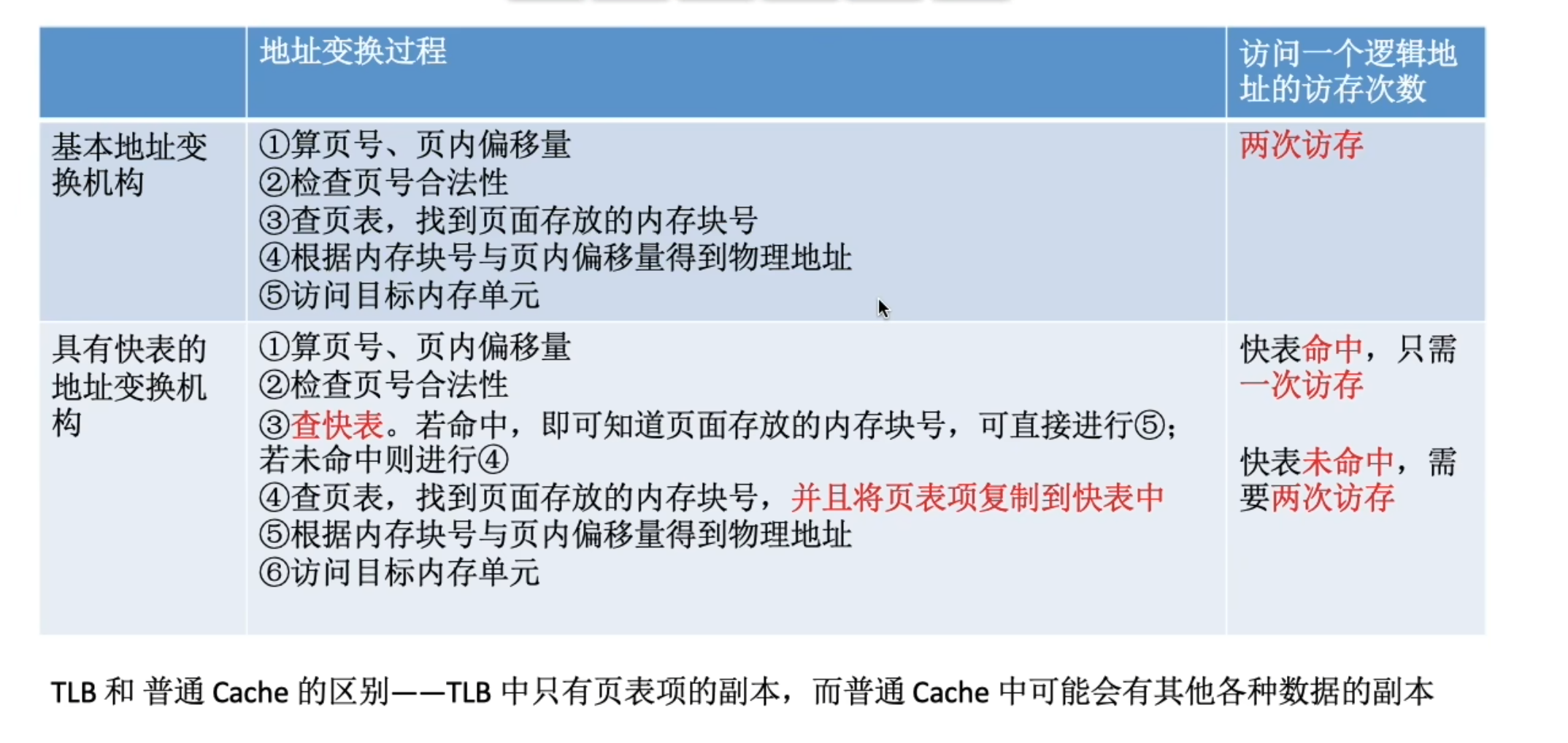

理解:是对基本地址变换机构的优化,减少访存次数来提高效率。

一、快表的概念

快表,又称联想寄存器(TLB ,translation lookaside buffer),是一种访问速度比内存快很多的高速缓存 (TLB 不是内存,类比 Cache ,但与 Cache 有所不同) ,用来存放最近访问的页表项的副本,可以加速地址变换的速度。与此对应,(上两节提到的与页面同样放在内存中的页表)内存中的页表常称为慢表。

理解:TLB 作用在逻辑地址到物理地址的转换阶段,而 Cache 作用在得到物理地址后要访存存取数据的阶段。二者都是高速缓存,设置的目的都是为了减少访存次数,提高机器效率。TLB 中只有页表项的副本,而普通 Cache 存放的是具体的指令(指令Cache)或数据(数据Cache)副本。

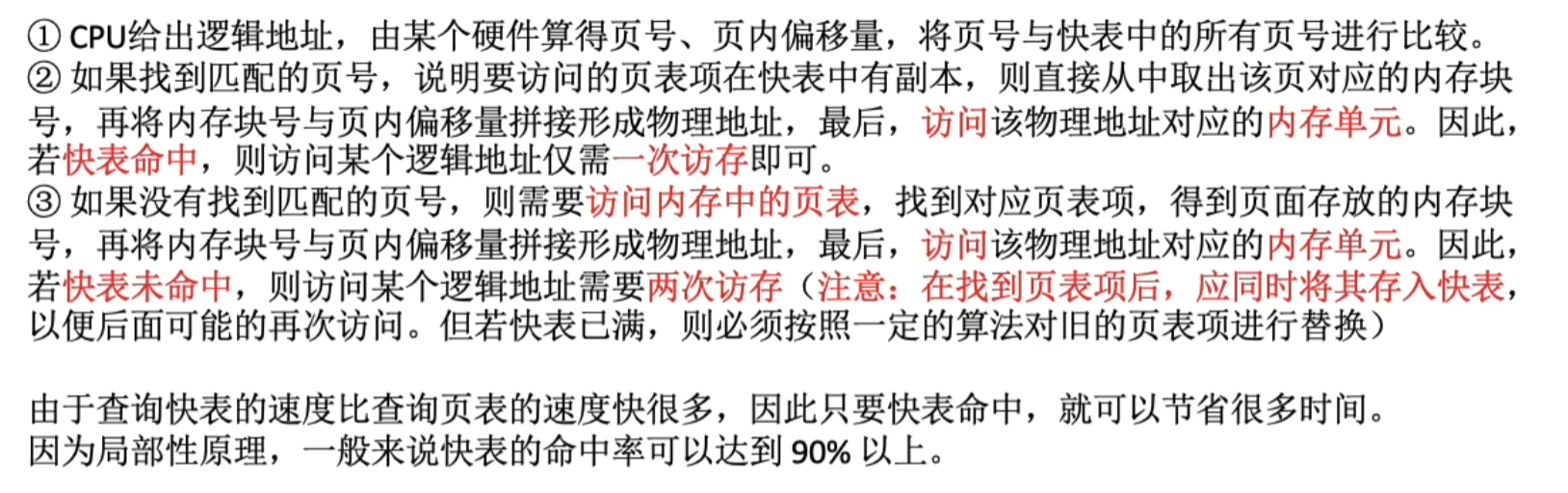

二、引入快表后的地址变换过程

——补充例题(区分两种方式的计算:快表查不到再查慢表和快慢表同时查询)

(甘特图)

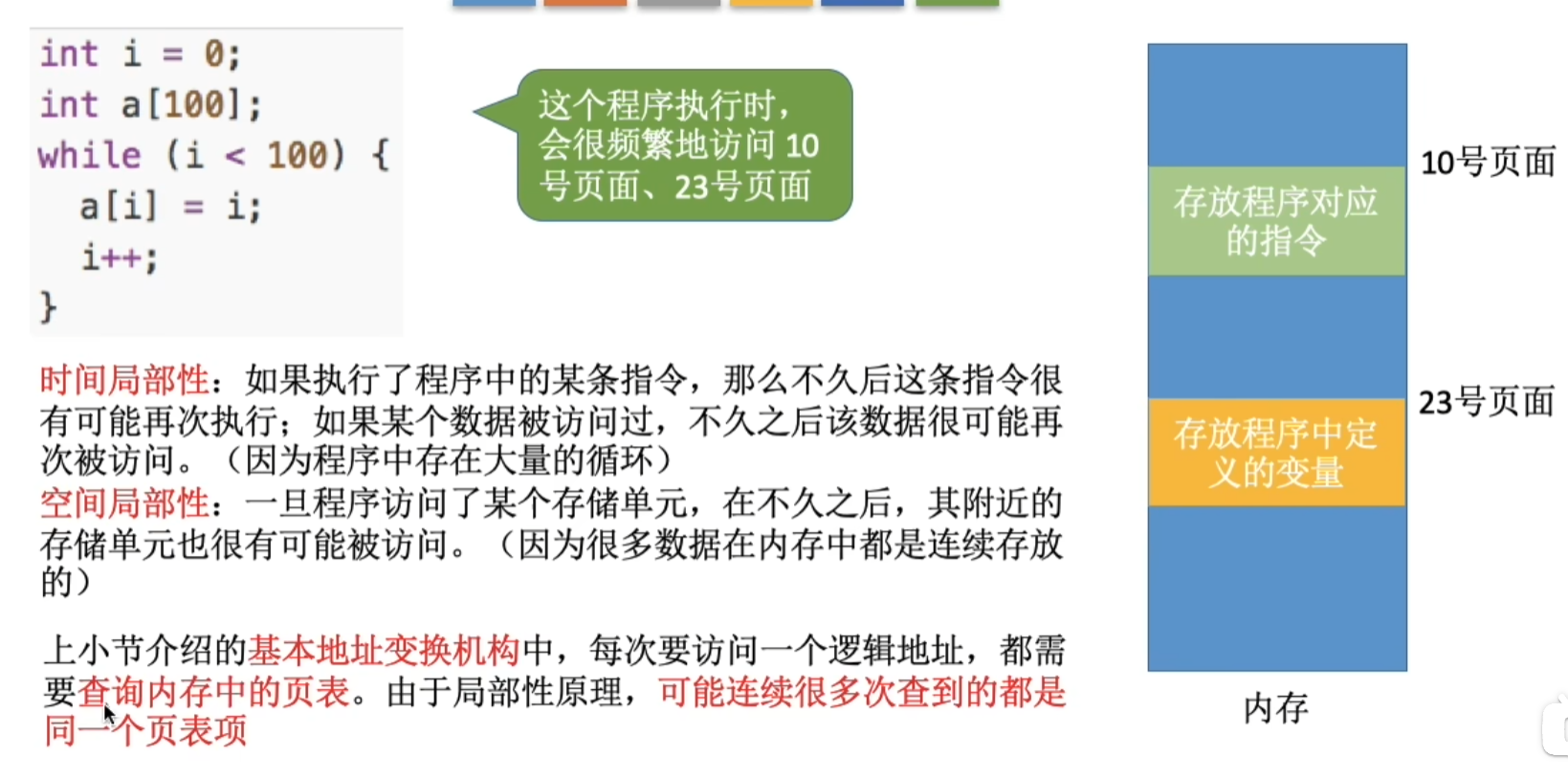

三、局部性原理

- 时间局部性

- 空间局部性

在这个案例中时间局部性体现于每一次的 while,空间局部性体现于数组 a 的连续存储。在同一进程下,局部性原理体现显著。

浙公网安备 33010602011771号

浙公网安备 33010602011771号