VL23 ROM的简单实现

- reg [3:0] rom [7:0];变量名称rom之前的[3:0]表示每个数据具有多少位,指位宽;变量名称rom之后的[7:0]表示需要多少个数据,指深度,注意这里深度为8(和输入地址addr一致);

- always 里面的else部分的写法是难点,这里是因为只需要初始化,其余状态就保持存储的原因,所以是赋值其本身。

- 理解“addr:8bit位宽的无符号数,输入到ROM的地址”。它的意思是rom[addr];

- 输出描述的“data:4bit位宽的无符号数,从ROM中读出的数据”。它的意思是data=rom[addr];

`timescale 1ns/1ns

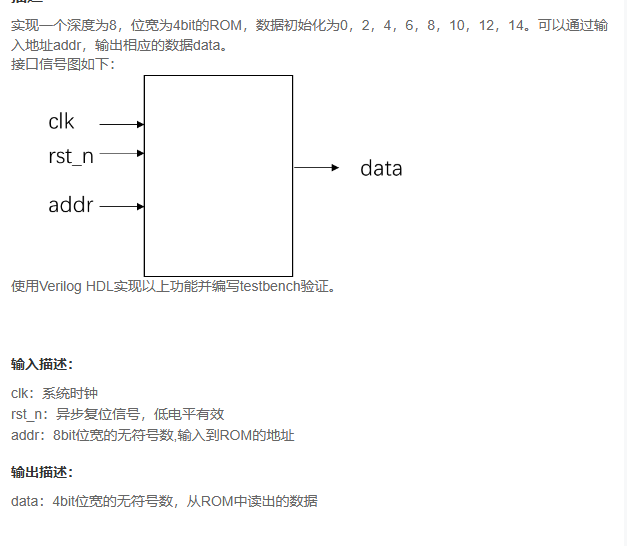

module rom(

input clk,

input rst_n,

input [7:0]addr,

output [3:0]data

);

reg [3:0] rom[7:0];

always @(posedge clk,negedge rst_n)begin

if(! rst_n)begin

rom[0]=4'd0;

rom[1]=4'd2;

rom[2]=4'd4;

rom[3]=4'd6;

rom[4]=4'd8;

rom[5]=4'd10;

rom[6]=4'd12;

rom[7]=4'd14;

end

else begin

rom[0]<=rom[0];

rom[1]<=rom[1];

rom[2]<=rom[2];

rom[3]<=rom[3];

rom[4]<=rom[4];

rom[5]<=rom[5];

rom[6]<=rom[6];

rom[7]<=rom[7];

end

end

assign data=rom[addr];

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号