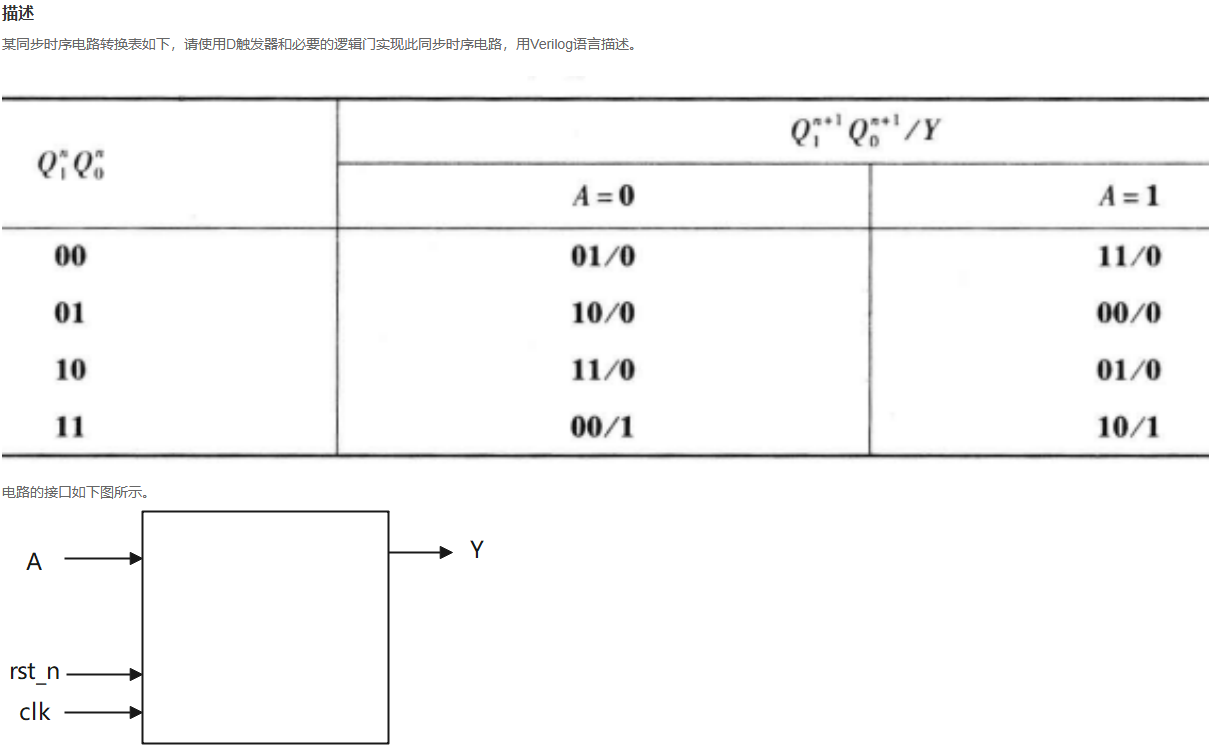

VL21 根据状态转移表实现时序电路

根据给的状态转移表知道有两个状态:第一列的为current_state,第二三列为next_state,且仅当current_state==11时候Y为1(使用()?:语法实现)。

三段式状态机的流程:

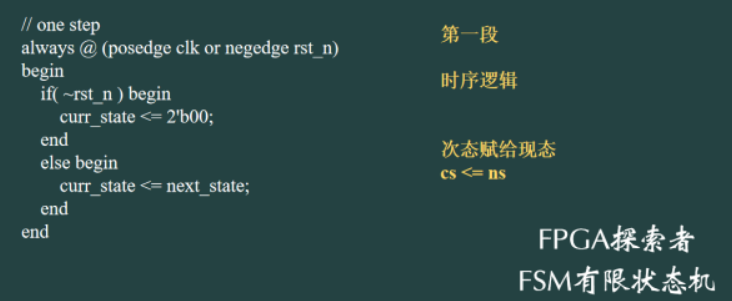

第一段:时序逻辑,公式化写法

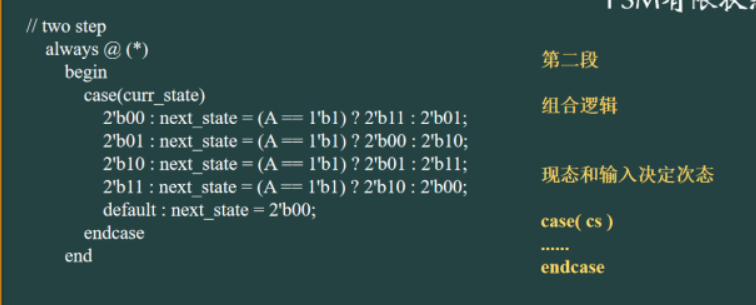

第二段:组合逻辑,这里要注意always @(*)是固定写法,不能像第一段写成时序。第二段写的是状态转移表,使用()?:语法实现。

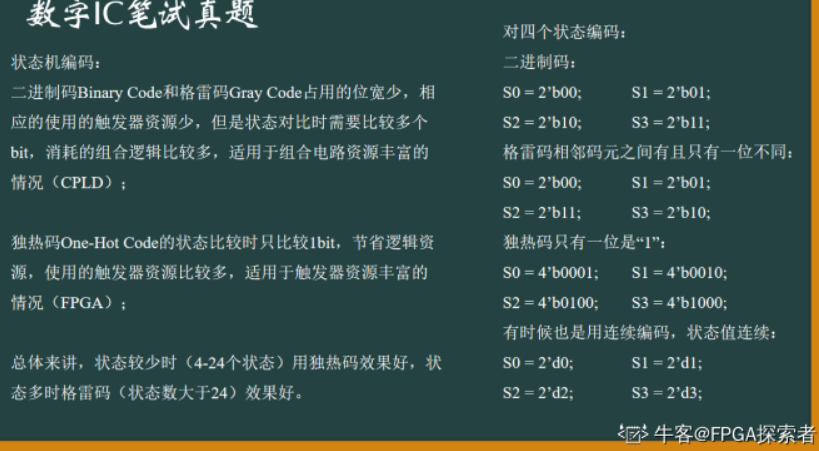

第三段:三个always块,一个always模块采用同步时序描述状态转移;一个always采用组合逻辑判断状态转移条件,描述状态转移规律;第三个always块使用同步时序描述状态输出,寄存器输出。。优点:三段式寄存器输出,不产生毛刺,有利于时序约束

这里使用的是两段式写法

`timescale 1ns/1ns

module seq_circuit(

input A ,

input clk ,

input rst_n,

output wire Y

);

reg [1:0] current_state;

reg [1:0] next_state;

always @(posedge clk,negedge rst_n)begin

if(!rst_n)begin

current_state<=2'b00;

next_state<=2'b00;

end

else

current_state<=next_state;

end

always @(*)begin

case(current_state)

2'b00 : next_state =(A==1'b0) ? 2'b01: 2'b11;

2'b01 : next_state =(A==1'b0) ? 2'b10: 2'b00;

2'b10 : next_state =(A==1'b0) ? 2'b11: 2'b01;

2'b11 : next_state =(A==1'b0) ? 2'b00: 2'b10;

default:next_state =2'b00;

endcase

end

assign Y=(current_state==2'b11) ? 1'b1 :1'b0;

endmodule

补充:

浙公网安备 33010602011771号

浙公网安备 33010602011771号