秋招准备

https://zhuanlan.zhihu.com/p/227876261

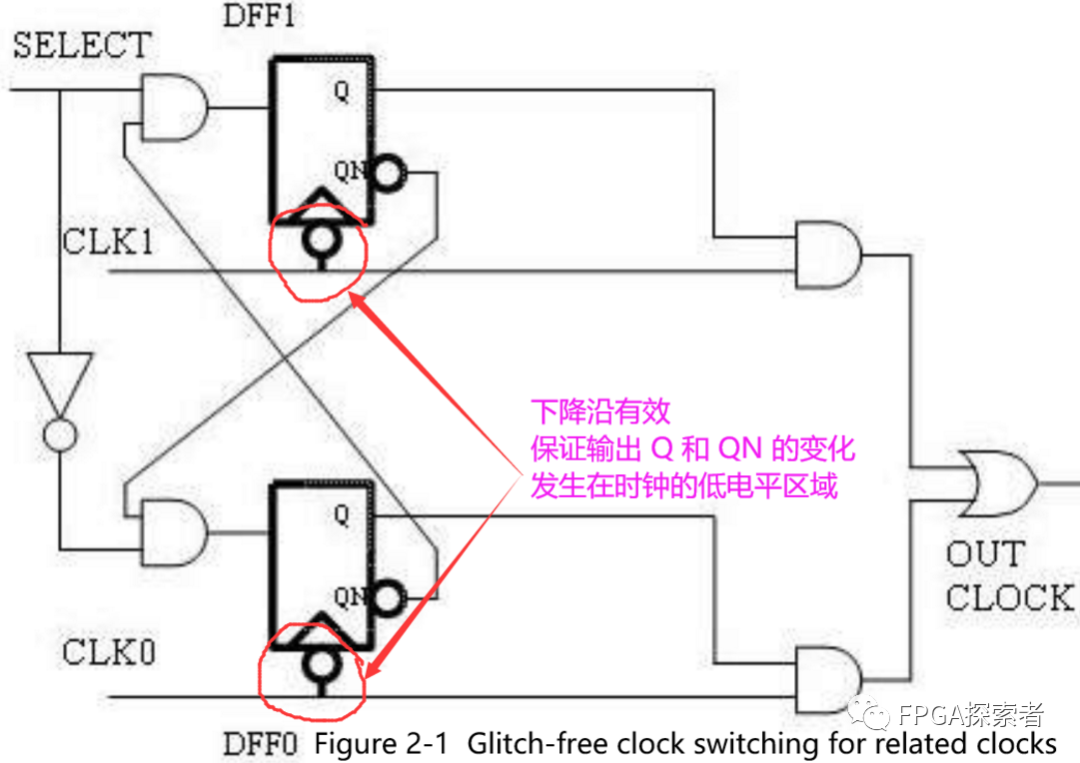

无毛刺时钟切换

门控时钟能够有效降低动态功耗,低功耗设计方法之一,在ASIC中使用较多,在FPGA使用较少(会影响时序分析)

核心思想 与门/与非门实现的门控时钟只能在时钟低电平处切换,也就是下降沿处切换;对于或门/或非门,高电平切换,也就是上升沿。

1.相关时钟之间

只需要在时钟源的选择路径加上一个下降沿有效的触发器(时钟输出是与门门控)用来接收另外一个时钟的选择信号的取反信号

2不相关时钟之间

在相关时钟无毛刺切换的基础上多加寄存器进行信号打两拍处理,降低亚稳态对信号的影响

时钟无毛刺切换代码

module clk_switch(

//sys

input clk1 ,

input clk2 ,

input rst_n ,

//input

input sel ,

//output

output clk_out

);

//=========================================

//================define===================

//=========================================

wire sel_1;

wire sel_2;

reg [1:0] dff1_r;

reg [1:0] dff2_r;

reg dff1_neg_out;

reg dff2_neg_out;

wire clk1_out,clk2_out;

//=========================================

//================main code================

//=========================================

assign sel_1 = sel & ~dff1_neg_out;

assign sel_2 = ~sel & ~dff2_neg_out;

always@(posedge clk1 or negedge rst_n)begin

if(!rst_n)

dff1_r <= 'd0;

else

dff1_r <= {dff1_r[1],sel_1};

end

always@(posedge clk2 or negedge rst_n)begin

if(!rst_n)

dff2_r <= 'd0;

else

dff2_r <= {dff2_r[1],sel_2};

end

always@(negedge clk1 or negedge rst_n)begin

if(!rst_n)

dff1_neg_out <= 'd0;

else

dff1_neg_out <= dff1_r[1];

end

always@(negedge clk2 or negedge rst_n)begin

if(!rst_n)

dff2_neg_out <= 'd0;

else

dff2_neg_out <= dff2_r[1];

end

assign clk1_out = dff1_neg_out & clk1;

assign clk2_out = dff2_neg_out & clk2;

assign clk_out = clk1_out | clk2_out;

endmodule时序约束

时序约束:就是设计者需要告诉软件(Quartus、Vivado、ISE等工具)应该从哪个引脚输入信号、输入信号需要延迟多长时间、时钟周期是多少。这样软件在布局布线的时候就知道怎么去操作,从而满足设计要求

主要包括:周期约束,偏移约束,静态时序路径约束

时序路径分为片内路径和片间路径

异步信号传输

单bit

慢到快 打两拍

快到慢 信号展宽

多bit

格雷码 握手 异步FIFO D-MUX同步器

时钟抖动

指的是芯片的某一给定点上时钟周期发生暂时性变化,也就是说时钟周期在不同的周期可能加长或者缩短,平均值0;

时序电路的延时

异步电路:一般通过加BUFFER、两级与非门实现;

同步电路:对于比较大的或者特殊要求的延时,一般通过计数器产生延时;较小的延时可以使用触发器打拍实现;

FPGA实现RAM/ROM/CAM存储资源

生成存储单元首选BLOCK RAM,一方面,由存储块构成,不占用FF和LUT资源;另一方面,可配置,,可靠性与速度比FF和LUT产生的分布式RAM更有优势;

IC设计中的寄生效应

寄生效应就是溜进PCB并在电路中影响性能且原因不明的小故障,是寄生电容和寄生电感引起的。理想情况下导线没有电阻电容电感的,但是导线足够长,电阻就相当可观。两条平行的导线之间有电压差异,就会形成平行板电容器,导线周围会产生磁场,进而产生感生电场,对电子的移动产生影响,这就是寄生电感。

在直流低频的情况下不明显,但是在交流特别是高频的情况下,会有很大的影响。这种寄生效应很难克服,只能通过优化线路,尽可能使用管脚短的SMT元器件,完全消除是不可能的。

上拉电阻

TTL驱动CMOS

OC门电路必须加上拉电阻,提高输出电平值

增大引脚驱动能力

提高总线抗干扰能力,总线悬空容易受到电磁干扰

阻值选择原则:

节约功耗方面:阻值应该足够大,电流小

驱动电流方面:阻值足够小

逻辑电平

TTL CMOS LVTTL LVDS LVCMOS

也可以说 1.2 3.3 5

TTL驱动CMOS不可以直接互联,TTL在0.3-3.6V CMOS有1.2和5V;如果需要互联,需要在输出端口加上拉电阻加到5V或者12V

CMOS驱动TTL可以直接互联

PMOS和NMOS

P管是空穴导电;N管是电子导电;电子的迁移率大于空穴,同样的电场下,N管电流大于P管,因此要增大P管的宽长比,使得两个管子的跳变时间、高低电平的噪声容限相等

反馈电路与应用

反馈就是在电路系统中将输出电路中的电量输入到输入电路

负反馈类型:电压电流串并联负反馈

负反馈优点:降低放大器的增益灵敏度、改变输入输出电阻、改善放大器的线性和非线性失真