IDDR

IDDR的工作模式

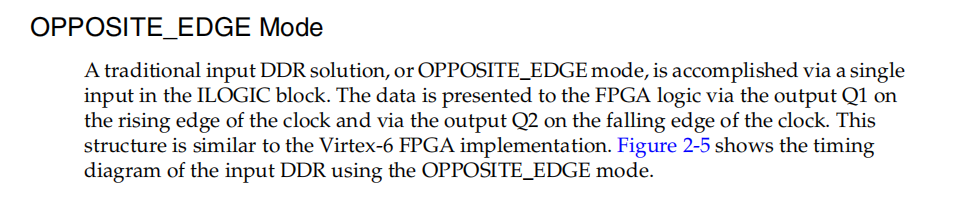

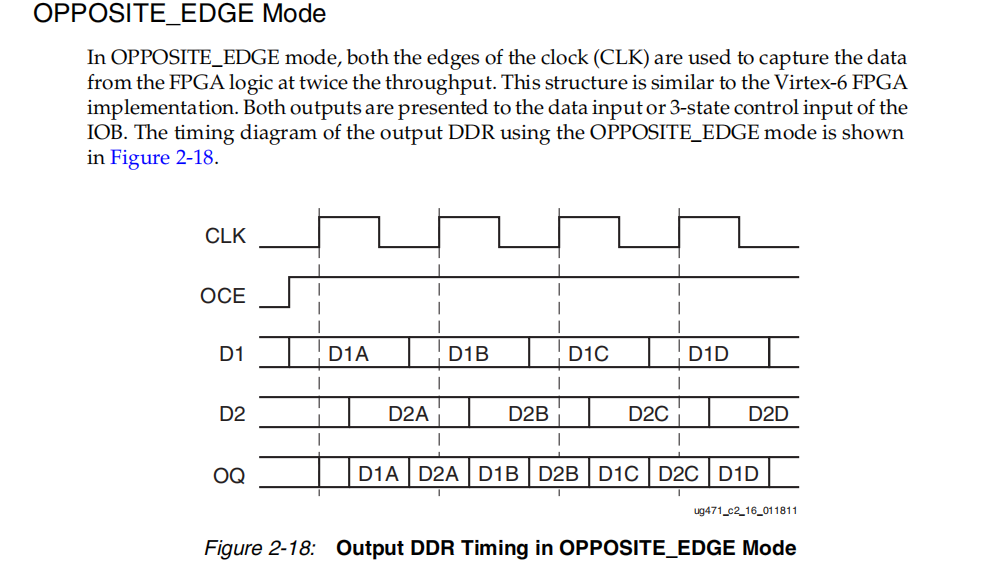

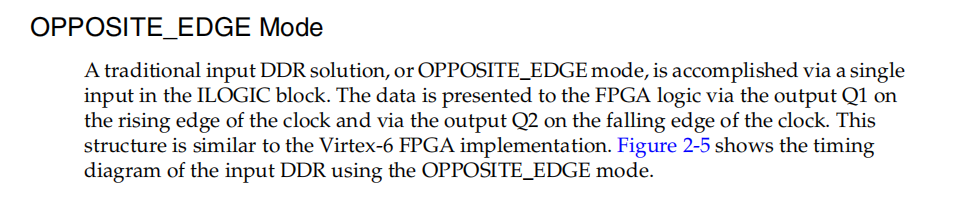

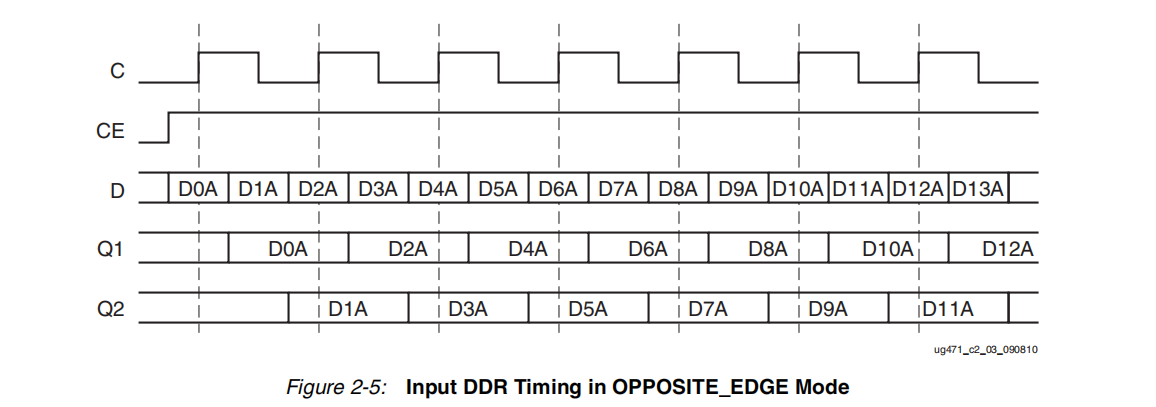

OPPOSITE_EDGE

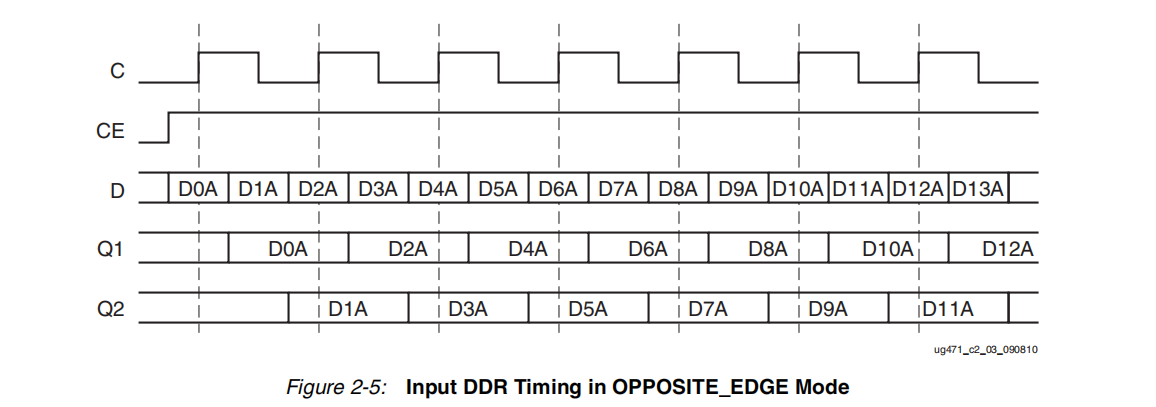

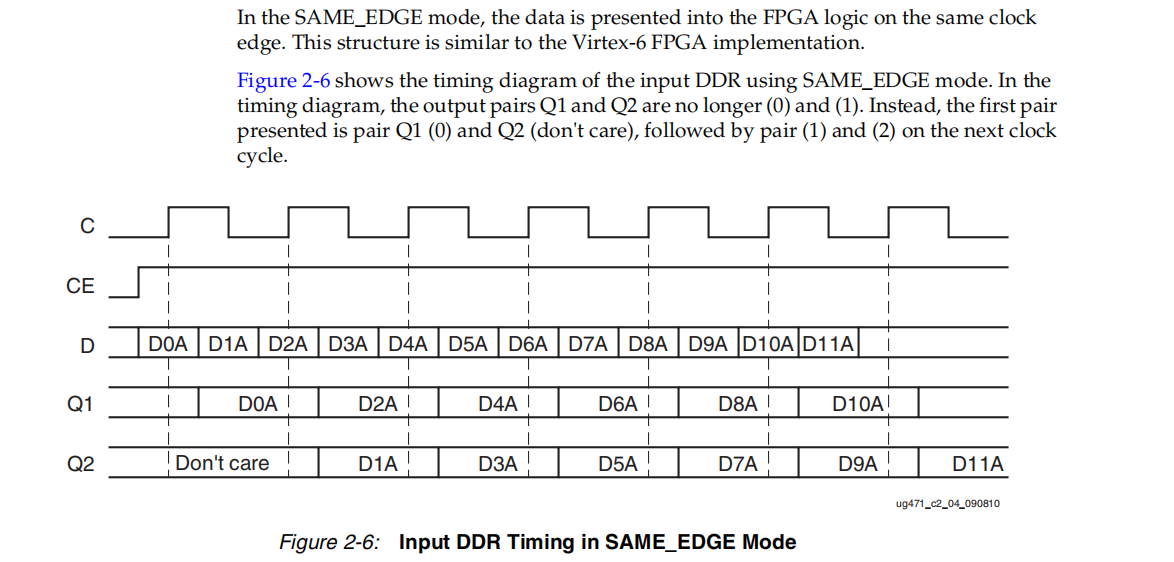

SAME_EDGE Mode

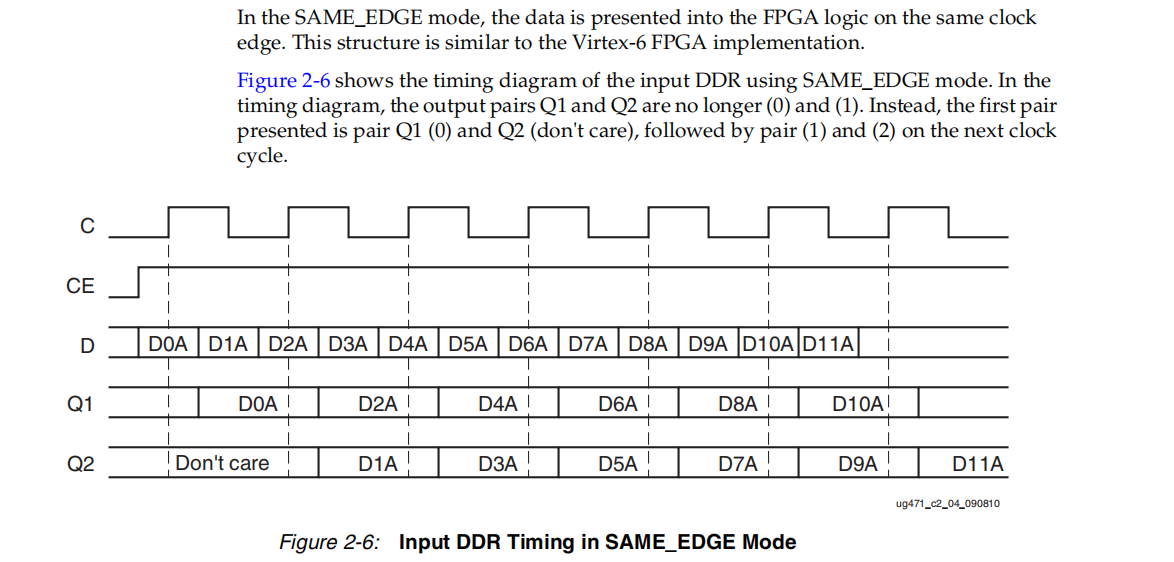

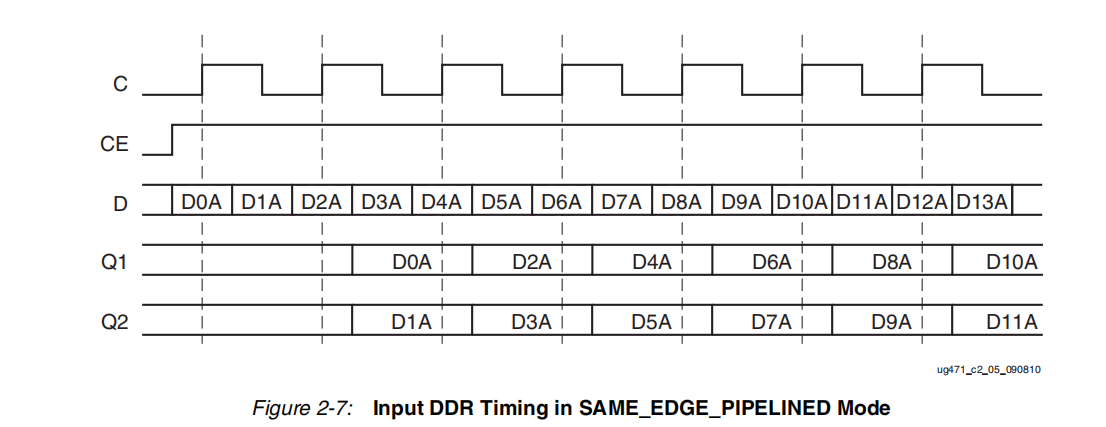

SAME_EDGE_PIPELINED Mode

参考使用:

generate

genvar i;

for(i = 0;i < 4;i = i + 1)begin:iddr_block

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1 ( eth_rxd_data[i] ), // 1-bit output for positive edge of clock

.Q2 ( eth_rxd_data[i+4] ), // 1-bit output for negative edge of clock

.C ( eth_rxc ), // 1-bit clock input

.CE ( 1'b1 ), // 1-bit clock enable input

.D ( eth_rxd[i] ), // 1-bit DDR data input

.R ( 1'b0 ), // 1-bit reset

.S ( 1'b0 ) // 1-bit set

);

end

endgenerate

// ctrl

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst_4_ctrl (

.Q1 ( eth_rxd_vaild ), // 1-bit output for positive edge of clock

.Q2 ( eth_rx_error ), // 1-bit output for negative edge of clock

.C ( eth_rxc ), // 1-bit clock input

.CE ( 1'b1 ), // 1-bit clock enable input

.D ( eth_rx_ctl ), // 1-bit DDR data input

.R ( 1'b0 ), // 1-bit reset

.S ( 1'b0 ) // 1-bit set

);

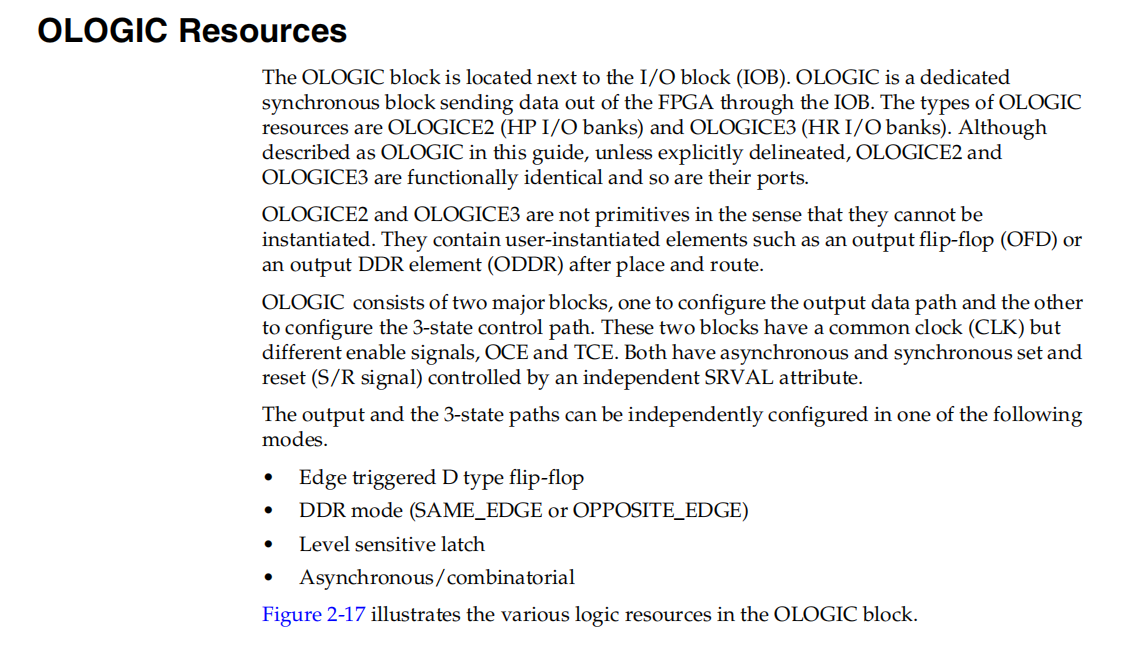

ODDR

基本:

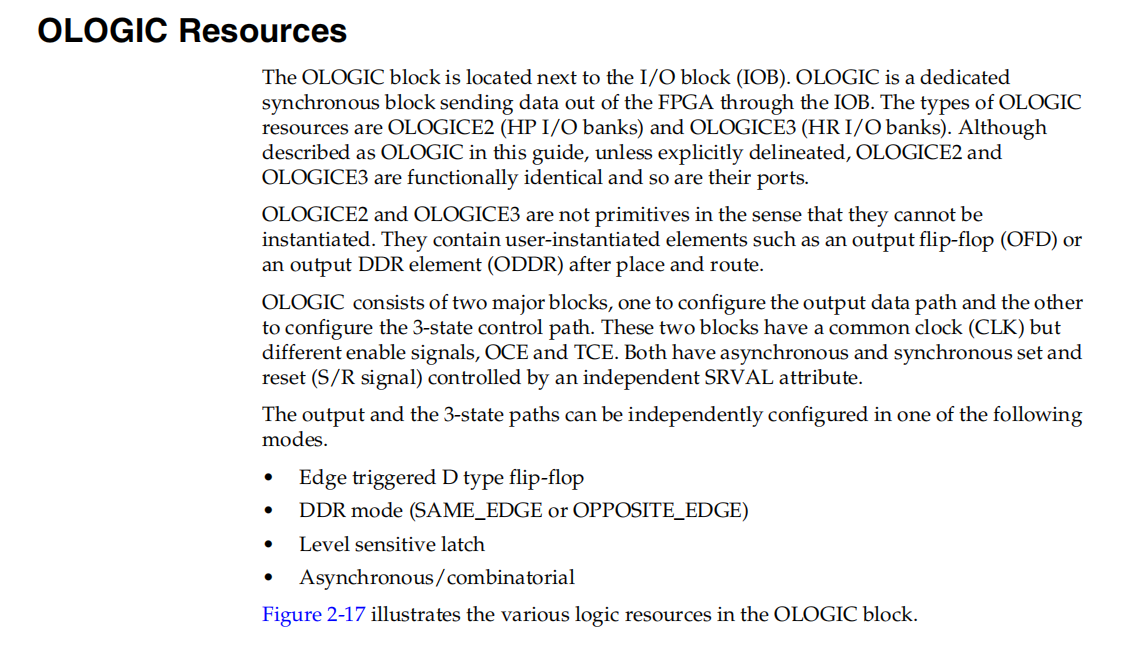

ODDR工作模式

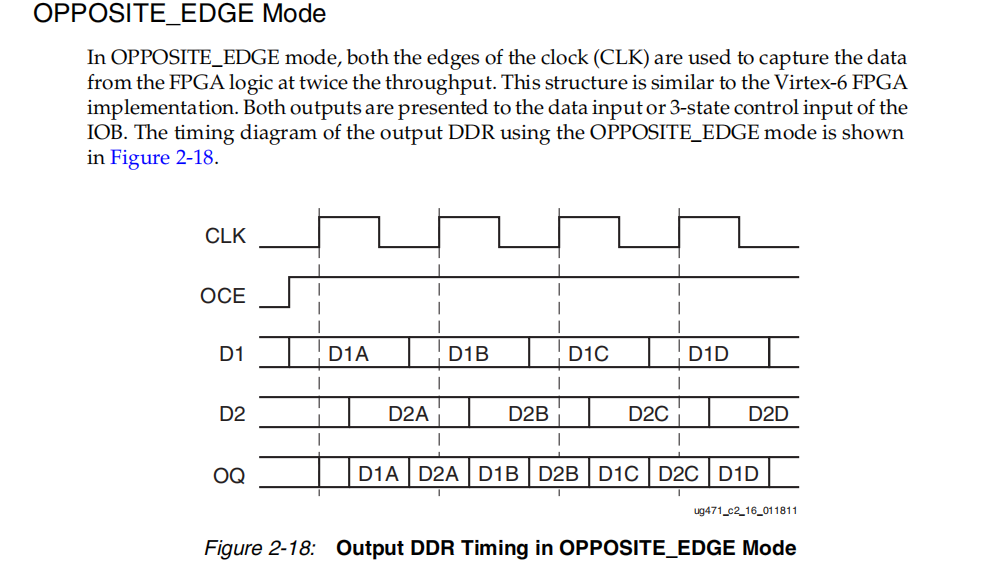

OPPOSITE_EDGE Mode

SAME_EDGE Mode

浙公网安备 33010602011771号

浙公网安备 33010602011771号