原语笔记:ICAP和在线升级

ICAP

描述:

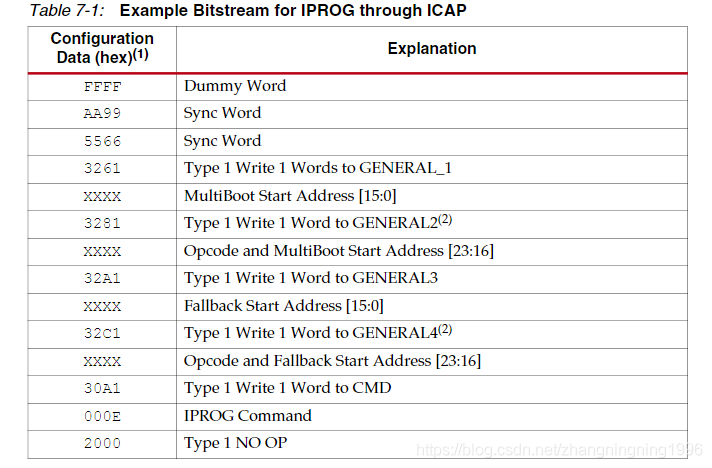

通过指定顺序向原语写入地址,以完成FPGA从指定存储器读取数据的目的;(此处是需要反转的)

Opcode:

Opcode的物理意义是对用flash的读命令代码,对应镁光的一般是0x03。

地址分为:

起始地址低位+起始地址高位

回调地址低位+回调地址高位

assign i_crop = {i_data[8],i_data[9],i_data[10],i_data[11],i_data[12],i_data[13],i_data[14],i_data[15],i_data[0],i_data[1],i_data[2],i_data[3],i_data[4],i_data[5],i_data[6],i_data[7]};

parameter DUM_WORD = 16'hFFFF; parameter SYNC_WORD1 = 16'hAA99; parameter SYNC_WORD2 = 16'h5566; parameter GEN_WORD1 = 16'h3261; parameter LOW_ADDR = 16'h0000; parameter GEN_WORD2 = 16'h3281; parameter HIG_ADDR = 16'h0310; parameter GEN_WORD3 = 16'h32A1; parameter LOW_ADDR_BACK = 16'h0000; parameter GEN_WORD4 = 16'h32C1; parameter HIG_ADDR_BACK = 16'h0300; parameter GEN_CMD_WORD = 16'h30A1; parameter IPROG_CMD = 16'h000E; parameter NOP_CMD = 16'h2000;

笔记:SP6

在线升级之ICAP,ISP,BIN,HEX,MCS_icap ip核 flash读写-CSDN博客

代码:

1、DEVICE_ID:不同芯片的DEVICE_ID不相同,在使用该原语时,一定要查找对用芯片的ID,具体查找的数据手册UG380 ;

2、SIM_CFG_FILE_NAME:仿真使用,默认即可。

3、BUSY:原语对应的忙信号

4、O:配置数据的输出

5、CE:原语的使能信号,低电平有效

6、CLK:原语的时钟信号

7、I:原语配置数据的输入信号

8、WRITE:读写原语的使能信号,低电平有效

ICAP_SPARTAN6 #( .DEVICE_ID(0'h4000093), // Specifies the pre-programmed Device ID value .SIM_CFG_FILE_NAME("NONE") // Specifies the Raw Bitstream (RBT) file to be parsed by the simulation // model ) ICAP_SPARTAN6_inst ( .BUSY(BUSY), // 1-bit output: Busy/Ready output .O(O), // 16-bit output: Configuartion data output bus .CE(CE), // 1-bit input: Active-Low ICAP Enable input .CLK(CLK), // 1-bit input: Clock input .I(I), // 16-bit input: Configuration data input bus .WRITE(WRITE) // 1-bit input: Read/Write control input ); // End of ICAP_SPARTAN6_inst instantiation

icap_delay Flash_ICAP_WAIT_inst0(

.sclk ( Sys_clk ),

.rst ( Rst_P ),

.rx_flag ( rx_done ),

.rx_data ( data_receive),

.icap_flag ( icap_flag ),

.led ( led )

);

icap_ctrl Flash_ICAP_CTL_inst0(

.sclk ( Sys_clk ),

.rst_n ( Rst_n ),

.pi_flag ( icap_flag )

);

module Flash_top ( input wire Sys_clk, input wire Rst_n , input wire rx , output wire tx , output wire Slave_CLK , output wire Slave_CS_N , output wire Slave_data_out, input wire Slave_data_in , output wire led ); //rx wire [7:0] data_receive; wire rx_done ; //tx wire [7:0] tx_data_in ; wire uart_en ; wire done_flag ; //SE wire SE_flag ; wire [23:0] SE_ADDR ; wire SE_Slave_CLK ; wire SE_Slave_CS_N ; wire SE_Slave_data_out; //PP wire PP_flag ; wire [23:0] PP_ADDR ; wire PP_WR_EN ; wire [7:0] PP_WR_DATA ; wire PP_Slave_CLK ; wire PP_Slave_CS_N ; wire PP_Slave_data_out; //RD wire RD_flag ; wire [23:0] RD_ADDR ; wire [10:0] RD_data_length ; wire FIFO_RD_EN ; wire FIFO_RD_ready ; wire [7:0] RD_DATA ; wire RD_Slave_CLK ; wire RD_Slave_CS_N ; wire RD_Slave_data_out; //ICAP wire icap_flag ; wire Rst_P ; assign Rst_P = ~Rst_n; tx_driver tx_driver_inst0( .Sys_clk ( Sys_clk ), .Rst_n ( Rst_n ), .data_in ( tx_data_in ), .uart_en ( uart_en ), .data_out ( tx ), .done_flag ( done_flag ) ); rx_teach rx_teach_inst0( .Sys_clk ( Sys_clk ), .Rst_n ( Rst_n ), .data_in ( rx ), .data_receive ( data_receive ), .rx_done ( rx_done ) ); Flash_CTL Flash_CTL_inst0( .Sys_clk ( Sys_clk ), .Rst_n ( Rst_n ), .rx_done ( rx_done ), .data_receive ( data_receive ), .done_flag ( done_flag ), .SE_Slave_CLK ( SE_Slave_CLK ), .SE_Slave_CS_N ( SE_Slave_CS_N ), .SE_Slave_data_out ( SE_Slave_data_out ), .PP_Slave_CLK ( PP_Slave_CLK ), .PP_Slave_CS_N ( PP_Slave_CS_N ), .PP_Slave_data_out ( PP_Slave_data_out ), .FIFO_RD_ready ( FIFO_RD_ready ), .RD_DATA ( RD_DATA ), .RD_Slave_CLK ( RD_Slave_CLK ), .RD_Slave_CS_N ( RD_Slave_CS_N ), .RD_Slave_data_out ( RD_Slave_data_out ), .Slave_CLK ( Slave_CLK ), .Slave_CS_N ( Slave_CS_N ), .Slave_data_out ( Slave_data_out ), .tx_data_in ( tx_data_in ), .uart_en ( uart_en ), .SE_flag ( SE_flag ), .SE_ADDR ( SE_ADDR ), .PP_flag ( PP_flag ), .PP_ADDR ( PP_ADDR ), .PP_WR_EN ( PP_WR_EN ), .PP_WR_DATA ( PP_WR_DATA ), .RD_flag ( RD_flag ), .RD_ADDR ( RD_ADDR ), .RD_data_length ( RD_data_length ), .FIFO_RD_EN ( FIFO_RD_EN ) ); Flash_SE Flash_SE_inst0( .Sys_clk ( Sys_clk ), .Rst_n ( Rst_n ), .SE_flag ( SE_flag ), .SE_ADDR ( SE_ADDR ), .Slave_data_out ( SE_Slave_data_out ), .Slave_CS_N ( SE_Slave_CS_N ), .Slave_CLK ( SE_Slave_CLK ) ); // flash_se flash_se_inst0( // .sclk ( Sys_clk ), // .rst ( Rst_n ), // .se_flag ( SE_flag ), // .se_addr ( SE_ADDR ), // .sck ( SE_Slave_CLK ), // .cs_n ( SE_Slave_CS_N ), // .sdi ( SE_Slave_data_out ) // ); Flash_PP Flash_PP_inst0( .Sys_clk ( Sys_clk ), .Rst_n ( Rst_n ), .PP_flag ( PP_flag ), .PP_ADDR ( PP_ADDR ), .WR_EN ( PP_WR_EN ), .WR_DATA ( PP_WR_DATA ), .Slave_data_out ( PP_Slave_data_out ), .Slave_CS_N ( PP_Slave_CS_N ), .Slave_CLK ( PP_Slave_CLK ) ); Flash_RD Flash_RD_inst0( .Sys_clk ( Sys_clk ), .Rst_n ( Rst_n ), .RD_flag ( RD_flag ), .RD_ADDR ( RD_ADDR ), .RD_data_length ( RD_data_length ), .Slave_data_in ( Slave_data_in ), .FIFO_RD_EN ( FIFO_RD_EN ), .Slave_CLK ( RD_Slave_CLK ), .Slave_CS_N ( RD_Slave_CS_N ), .Slave_data_out ( RD_Slave_data_out ), .FIFO_RD_ready ( FIFO_RD_ready ), .RD_DATA ( RD_DATA ) ); icap_delay Flash_ICAP_WAIT_inst0( .sclk ( Sys_clk ), .rst ( Rst_P ), .rx_flag ( rx_done ), .rx_data ( data_receive), .icap_flag ( icap_flag ), .led ( led ) ); icap_ctrl Flash_ICAP_CTL_inst0( .sclk ( Sys_clk ), .rst_n ( Rst_n ), .pi_flag ( icap_flag ) ); endmodule

这个原语在后续的芯片信号中升级为:

ICAPE2

和ICAP的操作顺序是不同的。

可参考转载:FPGA中ICAP原语的使用——Multiboot功能的实现_icap源语-CSDN博客

整体Flash升级操作步骤:

参考之前写的笔记:

在线升级之ICAP,ISP,BIN,HEX,MCS_icap ip核 flash读写-CSDN博客

1.JTAG的方式烧入Flash读写擦除程序;

2.通过上位机软件将BIN文件烧入Flash中指定好的地址(步骤1烧入的程序接受并处理);

Flash操作和ICAP相关代码:

浙公网安备 33010602011771号

浙公网安备 33010602011771号