3.19 运算方法和运算部件

1 补码加法运算部件

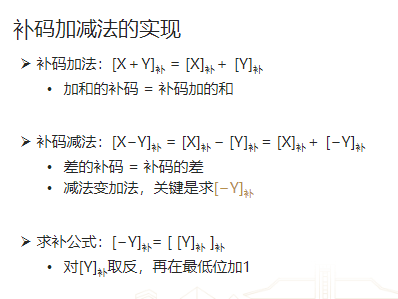

1.1 补码加减法的实现

(1)例:a=

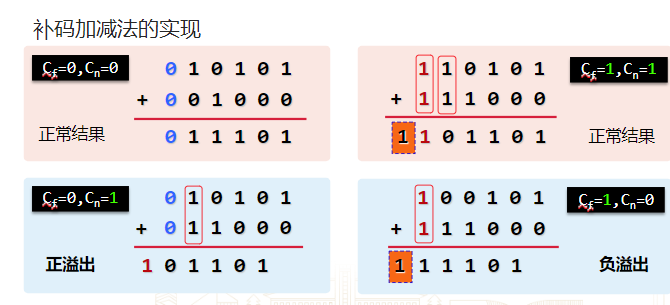

1.2 溢出

判断逻辑:负负得正/正正得负 就是溢出

定义检测溢出的信号位

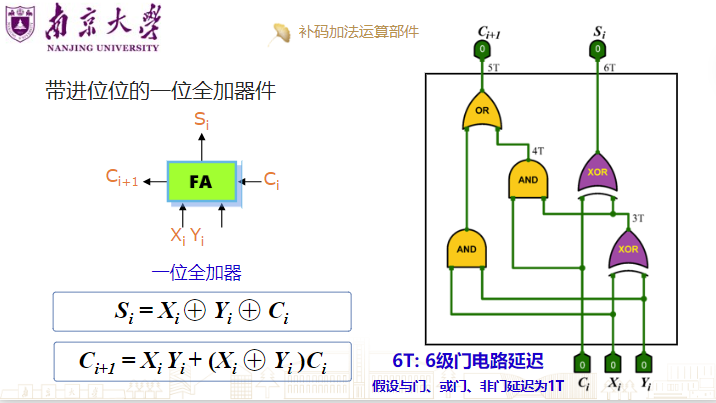

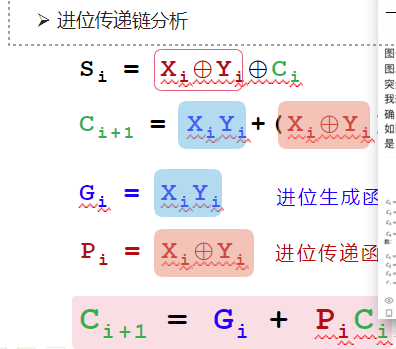

1.3 加法器的实现

n位加法器的实现

实现带符号位

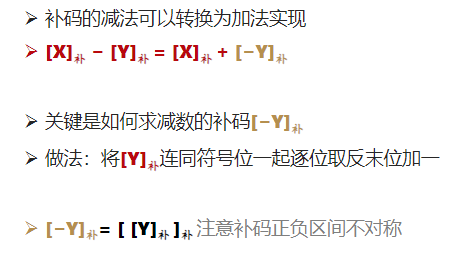

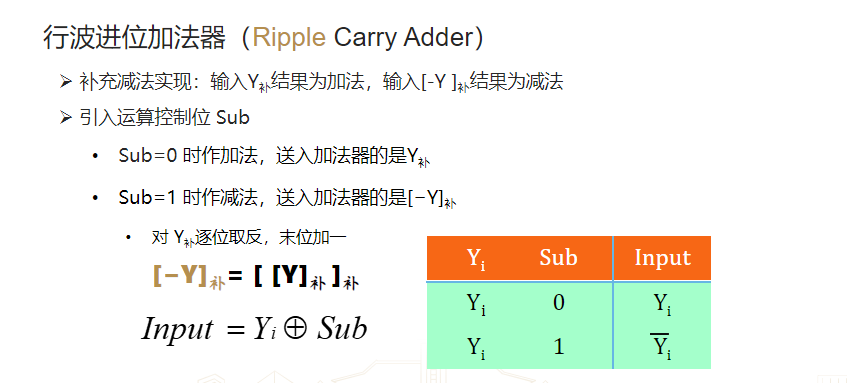

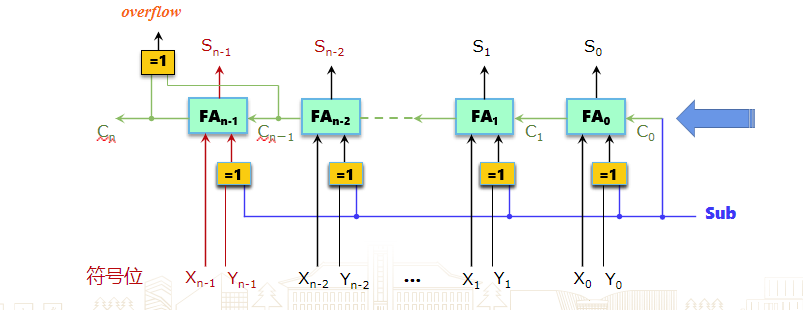

1.4 减法器的实现

可以把减法转化成加号

与1异或就是进行逐位取反

最后再让C0+1(c0正常是毫无意义的)

1.4.1 无符号数的溢出判断:加法变小,减法变大

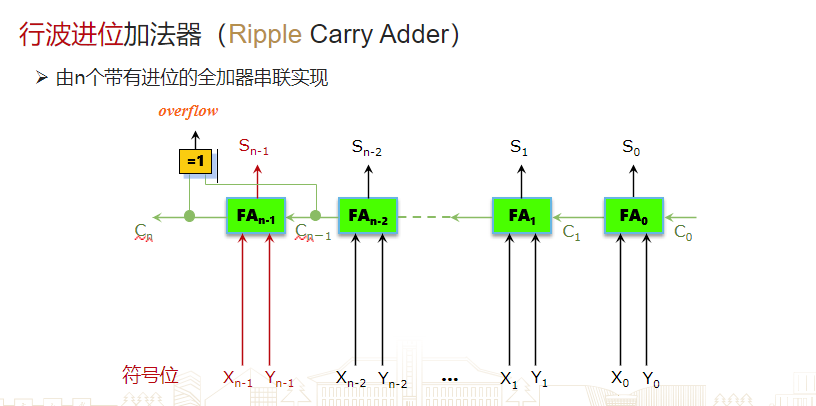

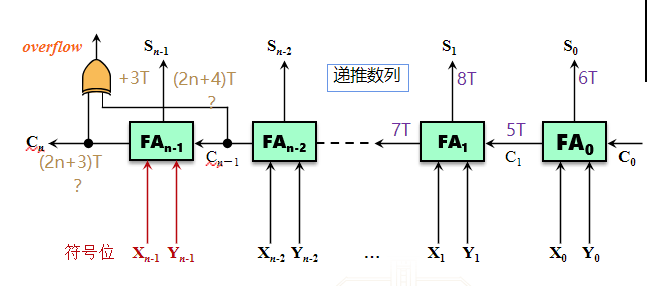

1.5 n位加法器的门级延迟(行波加法器)

(从一个c到下一个c只需要两个门级延迟)

(一个异或运算是三个门级延迟)

1.5.1 如何减少延迟

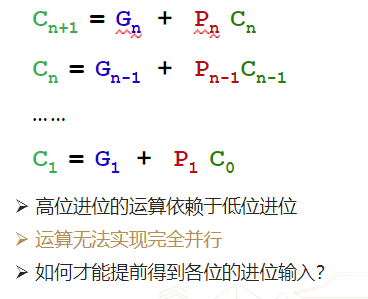

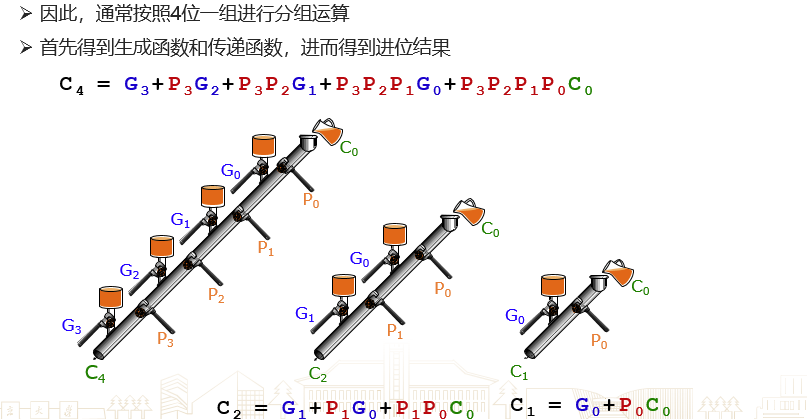

观察发现:延迟瓶颈在于进位运算

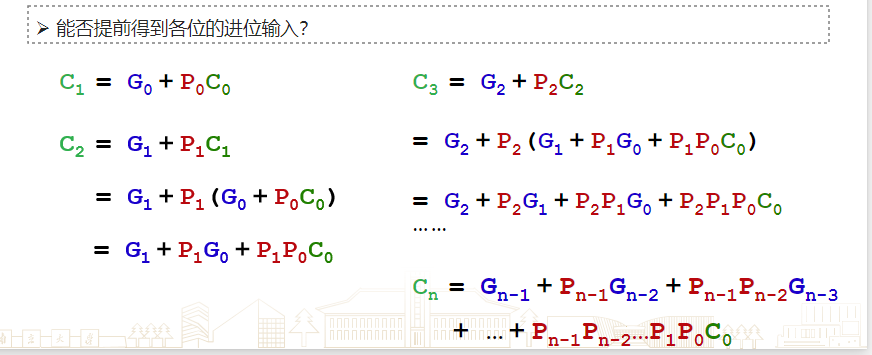

改进思路:能否提前产生各位的进位输入,使得各个位置上的加法运算能并行起来

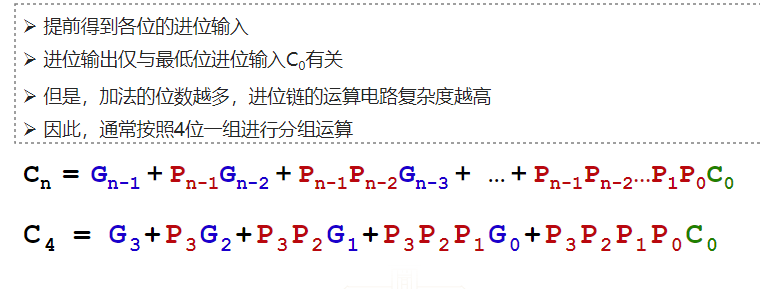

通过代入表达式简化运算

但是仍然存在问题,代入后的表达式复杂度也会提高

最终形成的运算部件

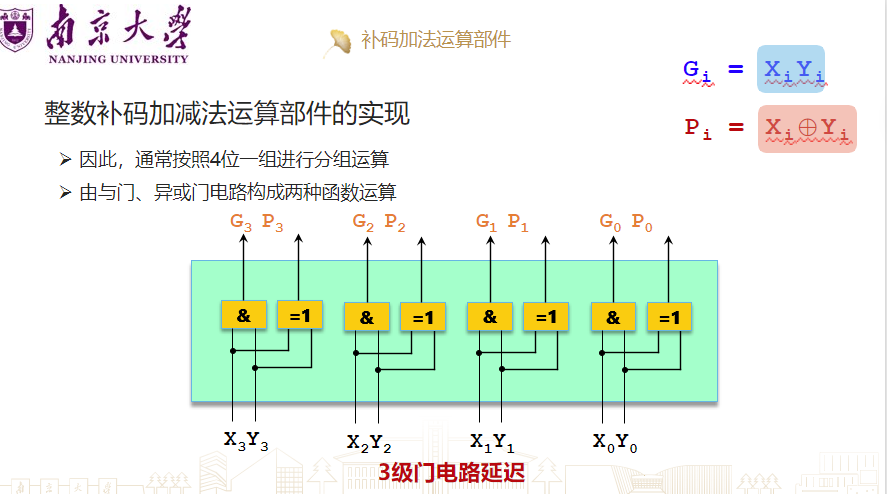

生成p的门级延迟是3位(=1代表异或)

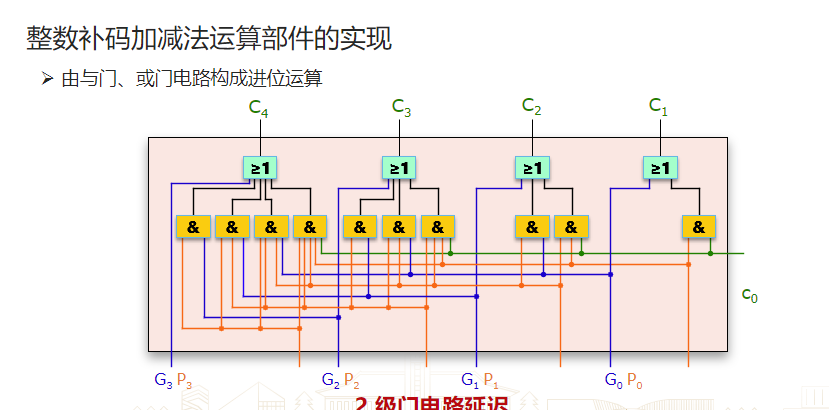

再通过p0,g0得到c

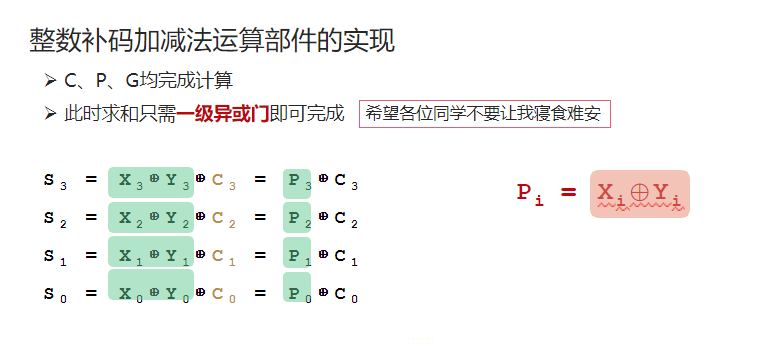

最后完成对S的计算

C:对下一位的进位;S:本位的值

最终效果:4位的门级进位将12级的门级延迟降到8级的门级延迟(3+2+3)

3:从x,y输入形成G,P

2:g,p形成c

3:c,p异或形成s

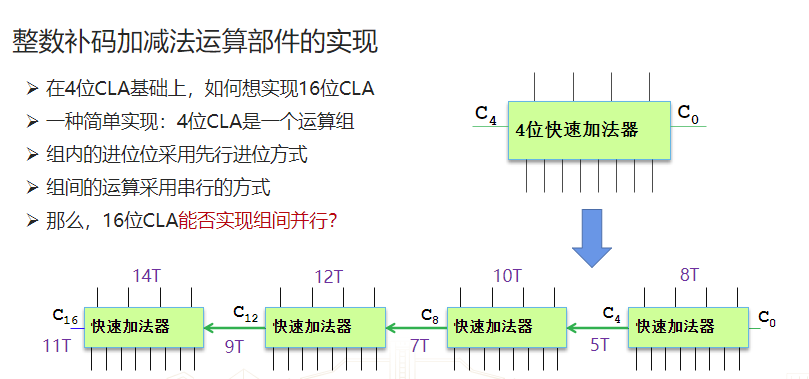

1.5.2 快速加法器串联

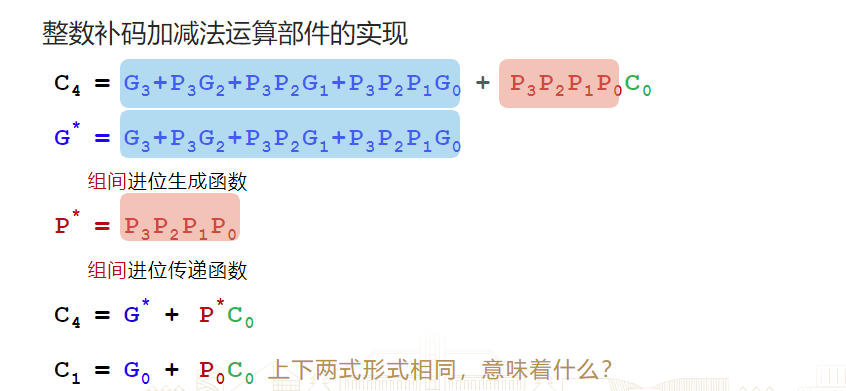

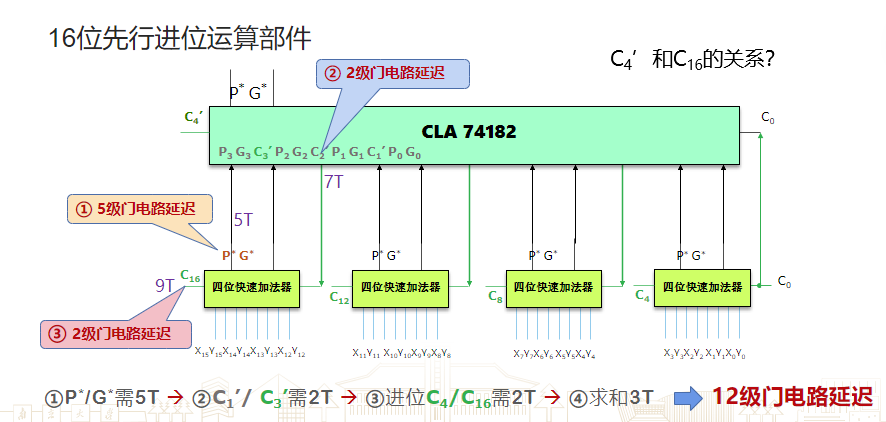

1.5.3 继续!

5:生成p/g需要3,p/g做&运算需要2

2:p,g生成c需要2

2:生成c4需要p,g,c ?

浙公网安备 33010602011771号

浙公网安备 33010602011771号