3.5 数字逻辑电路

7.1 二进制逻辑运算

7.1.1 与函数(只有两个输入都为真,结果才为真),按位与运算

7.1.1.1 与函数应用:掩码:

例:A的最右边两位有特殊的重要性,就可以设置一个掩码00000011,(即前六位都被屏蔽了,最后两位被保留)

7.1.2 或函数 (两个输入都为真,结果就为真)

7.1.3 非函数(单输入取反)

7.1.4 异或函数(相异为1,相同为0)

7.1.5 三种基本符号表示

与:·

或:+

非:-

7.1.6 逻辑完备性:任何一种逻辑都可以由上面三种基本逻辑实现

7.2 晶体管和门电路

7.2.1 N型和P型(都起到开关的作用

)

如果N型晶体管的栅极加高电压,源极到漏极相当于电线,如果加低电压,就相当于断路;P型晶体管与之相反

7.2.2 门电路

7.2.2.1 非门

7.2.2.2 或非门,或门

7.2.2.3 与门,与非门

7.2.2.4 多个输入的与/或门

只要有一个输入为1/0结果就为1/0

tip:设计电路时先观察真值表,看看什么情况下输出为1

7.3 组合逻辑电路

7.3.1 译码器

功能:只有一个输出为1,其余输入都为0

用处:可以用来判断某位组合

输入,输出:通常,译码器有n个输出,2^n个输出

7.3.2 多路选择器

构成:多路选择器由n条选择线和2^n个输入组成

通过对S的(1,0;0,1;1,1;0,0)表示四种选择

tip:假设一个路有四个位,也不影响选择线的个数,只是输出也要四条线

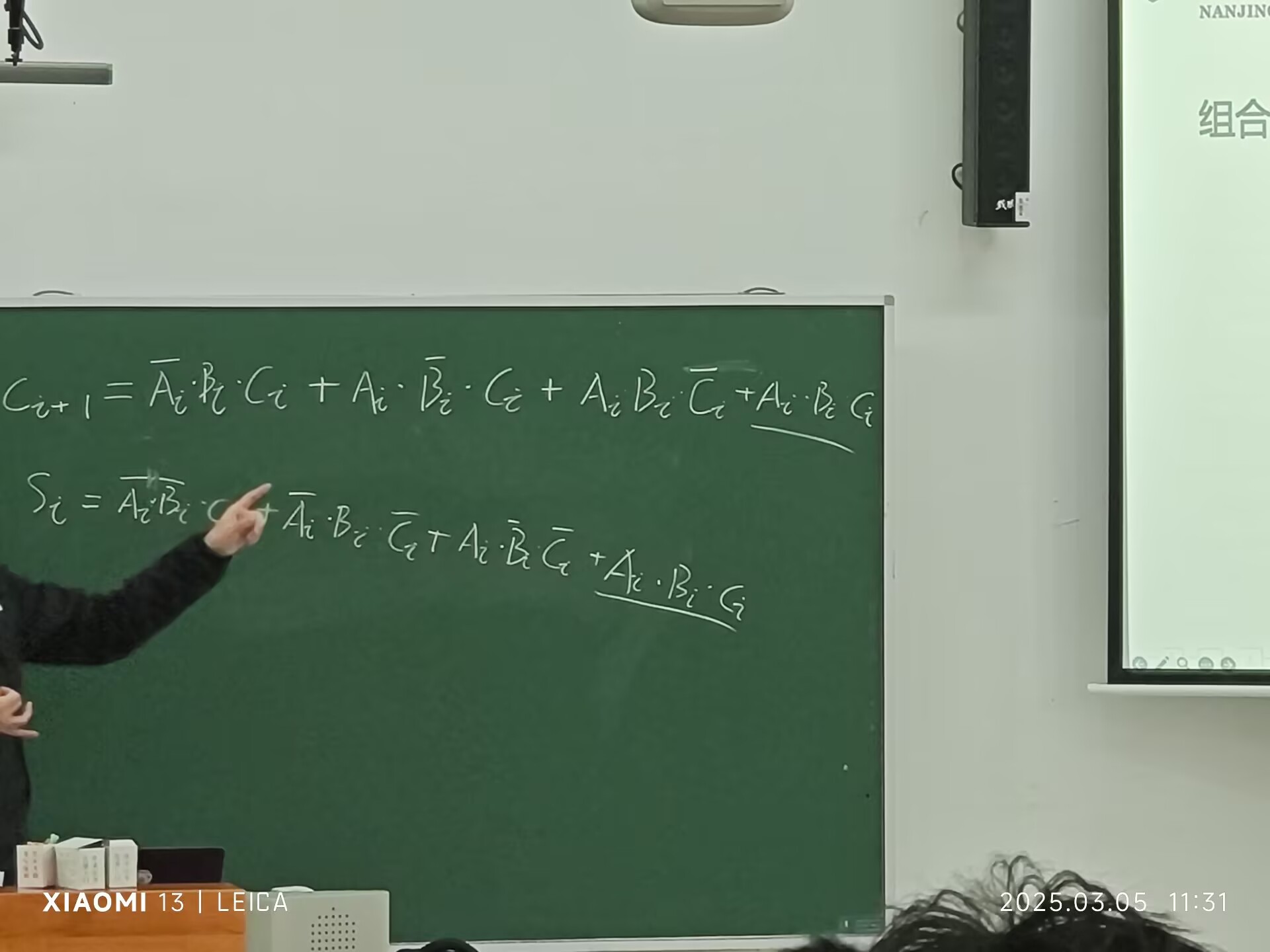

7.3.3 加法运算器

确定真值表中为1的,列出来对应的真值,(然后用非+或+与 就可以实现全加法器)

7.3.4 逻辑完备性

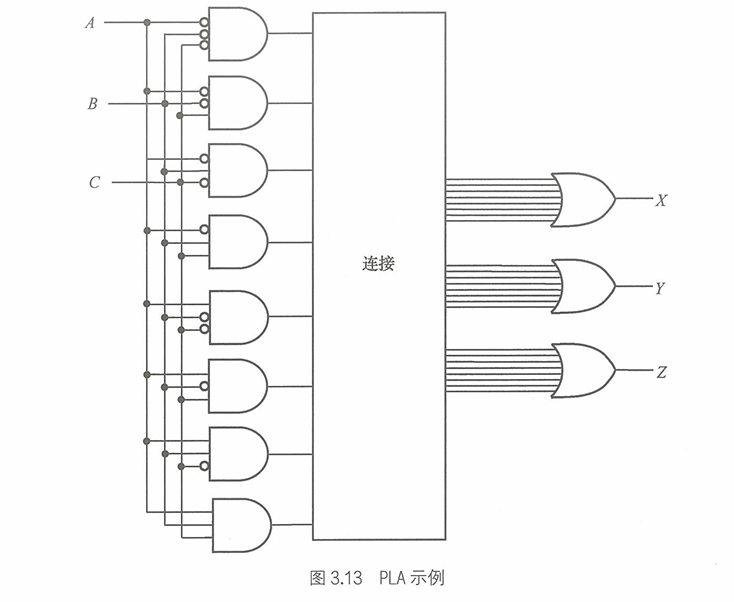

可编程逻辑阵列(PLA)(集合了与/或/非门)

通过连接不同的门,不同顺序连接的门,即可实现任意在PLA范围之内的器件

7.3.5 布尔代数和逻辑电路

通过布尔代数定律进行逻辑等价变化,可减少门的数目

注:此处的+表示或门,·表示与门

浙公网安备 33010602011771号

浙公网安备 33010602011771号