ADC

1、ADC 简介

ADC 即模拟数字转换器,英文详称 Analog-to-digital converter,可以将外部的模拟信号转换为数字信号。

STM32F407IGT6 芯片拥有 3 个 ADC, 都可以独立工作,其中 ADC1 和 ADC2 还可以组成双重模式(提高采样率)。 这些 ADC 都是 12 位、 10 位、 8 位和 6 位可选的逐次逼近型的模拟数字转换器, 有 19 个通道,可测量 16 个外部信号源、 2 个内部信号源和 Vbat 通道的信号。 ADC 中的各个通道的 A/D转换可以单次、连续、扫描或间断模式执行。 ADC 的结果可以以左对齐或者右对齐存储在 16位数据寄存器中。 ADC 具有独立模式、双重模式和三重模式,对于不同 AD 转换要求几乎都有合适的模式可选。 ADC功能非常强大,具体的我们在功能框图中分析每个部分的功能。

STM32F407 的 ADC 主要特性我们可以总结为以下几条:

(1)、12 位分辨率

(2)、转换结束、注入转换结束和发生模拟看门狗事件时产生中断

(3)、单次和连续转换模式

(4)、自校准

(5)、带内嵌数据一致性的数据对齐

(6)、采样间隔可以按通道分别编程

(7)、规则转换和注入转换均有外部触发选项

(8)、间断模式

(9)、双重模式(带 2 个或以上 ADC 的器件)

(10)、 ADC 供电要求: 2.4V 到 3.6V

(11)、 ADC 输入范围: VREF– ≤ VIN ≤ VREF+

(12)、规则通道转换期间有 DMA 请求产生

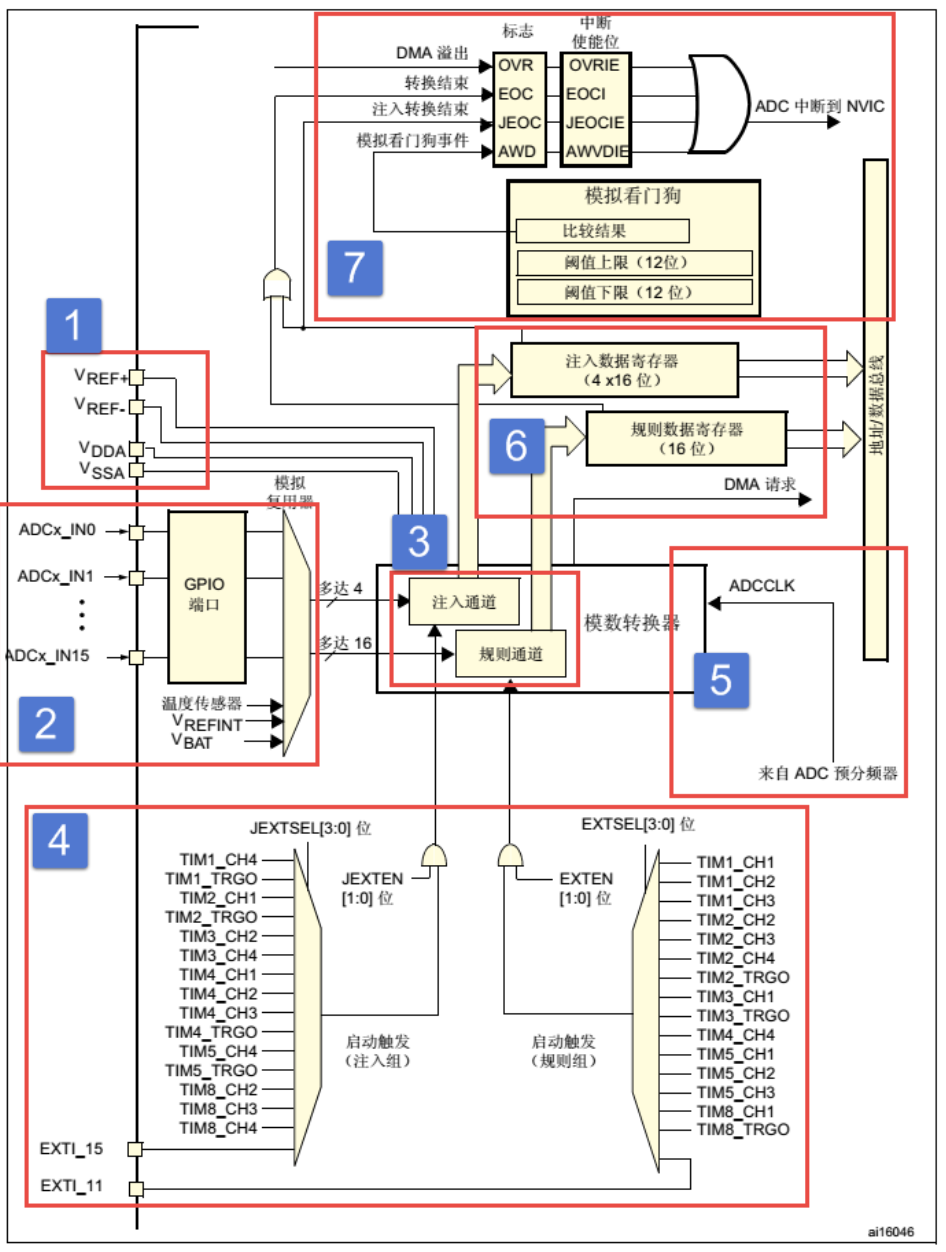

下面来介绍 ADC 的框图:

掌握了 ADC 的功能框图,就可以对 ADC 有一个整体的把握,在编程的时候可以做到了然如胸,不会一知半解。框图讲解采用从左到右的方式,跟 ADC 采集数据,转换数据,传输数据的方向大概一致。

(1). ①电压输入范围

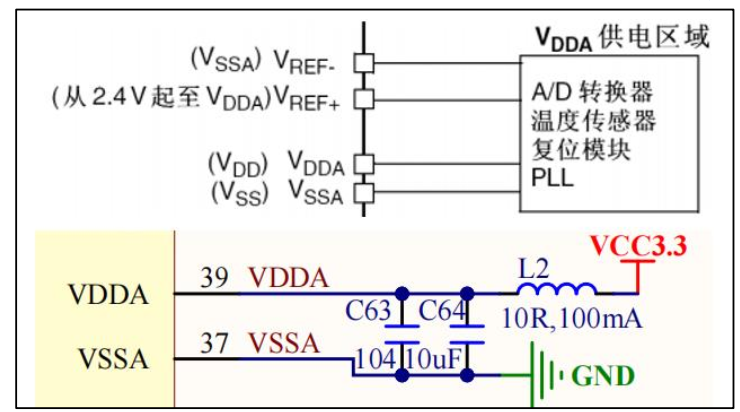

ADC 输入范围为: VREF- ≤ VIN ≤ VREF+。由 VREF-、 VREF+ 、 VDDA 、 VSSA、这四个外部引脚决定。

我们在设计原理图的时候一般把 VSSA和 VREF-接地,把 VREF+和 VDDA 接 3V3,得到ADC 的输入电压范围为: 0~3.3V。

如果我们想让输入的电压范围变宽,去到可以测试负电压或者更高的正电压,我们可以在外部加一个电压调理电路,把需要转换的电压抬升或者降压到 0~3.3V,这样 ADC 就可以测量了。

下面看一下这几个参数的关系:

从上图可以知道, VDDA和 VREF+接 VCC3.3,而 VSSA 和 VREF-是接地,所以 ADC 的输入范围即 0~3.3V。

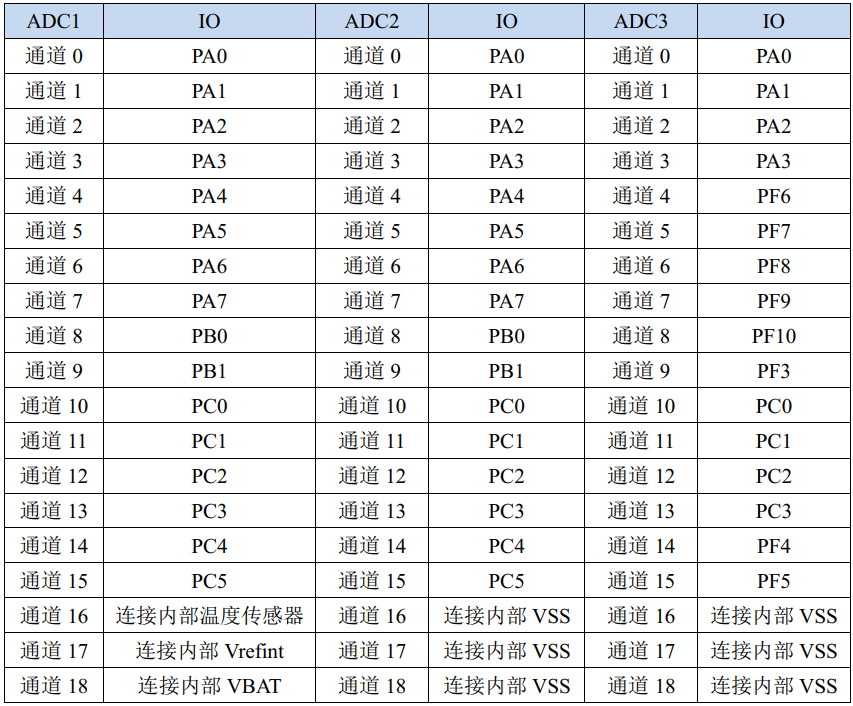

(2). ②输入通道

我们确定好 ADC 输入电压之后,那么电压怎么输入到 ADC?这里我们引入通道的概念, STM32 的 ADC 多达 19 个通道,其中外部的 16 个通道就是框图中的 ADCx_IN0、ADCx_IN1...ADCx_IN5。这 16 个通道对应着不同的 IO 口, 具体是哪一个 IO 口可以从手册查询到。其中 ADC1/2/3 还有内部通道: ADC1 的通道 ADC1_IN16 连接到内部的 VSS,通道 ADC1_IN17 连接到了内部参考电压 VREFINT 连接,通道 ADC1_IN18 连接到了芯片内部的温度传感器或者备用电源 VBAT。 ADC2 和 ADC3 的通道 16、 17、 18 全部连接到了内部的 VSS。

图 31-2 STM32F407ZGT6 ADC 通道

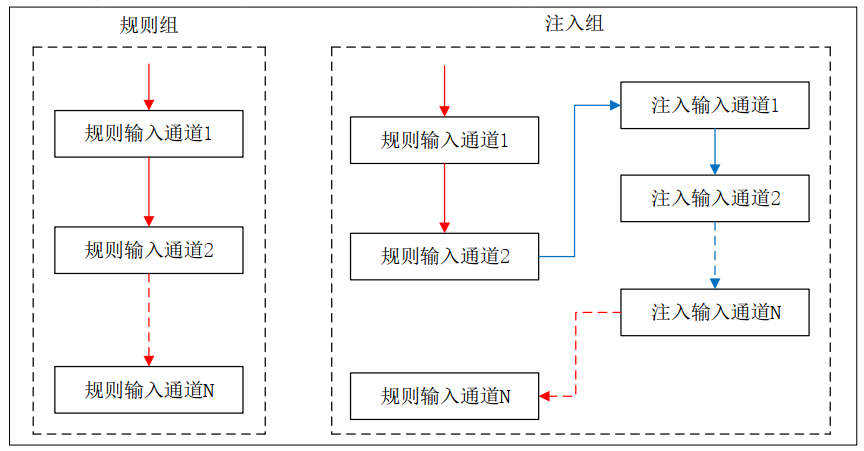

外部的 16 个通道在转换的时候又分为规则通道和注入通道,其中规则通道最多有 16路,注入通道最多有 4 路。那这两个通道有什么区别?在什么时候使用?

规则通道:顾名思意,规则通道就是很规矩的意思,我们平时一般使用的就是这个通道,或者应该说我们用到的都是这个通道,没有什么特别要注意的可讲。

注入通道:注入,可以理解为插入,插队的意思,是一种不安分的通道。它是一种在规则通道转换的时候强行插入要转换的一种。如果在规则通道转换过程中,有注入通道插队,那么就要先转换完注入通道,等注入通道转换完成后,再回到规则通道的转换流程。这点跟中断程序很像,都是不安分的主。所以,注入通道只有在规则通道存在时才会出现。

为了便于理解,下面看一下规则组和注入组的执行优先级对比图,如下图所示:

在STM32的ADC模块中,规则通道(Regular Channels)和注入通道(Injected Channels)的使用场景不同,具体选择哪个取决于应用需求。以下是它们的典型使用场景和区别:

1)规则通道(Regular Channels)

用途:用于常规、顺序采样的多通道转换。

特点:

最多支持16个通道(具体取决于型号)。

按预设顺序依次采样(通过SQRx寄存器配置)。

转换结果存储在单一的ADC_DR(数据寄存器)中,需及时读取以避免覆盖。

通常用于周期性采样(如传感器数据采集、电池电压监测等)。

典型场景:

多路传感器(如温度、光敏、电位器)轮流采样。

需要DMA传输的连续采样(因规则通道支持DMA)。

2)注入通道(Injected Channels)

用途:用于高优先级、突发插入的采样(类似“中断”)。

特点:

最多支持4个通道(具体取决于型号)。

可打断规则通道的转换,立即执行注入通道的采样(优先级更高)。

转换结果存储在独立的ADC_JDRx寄存器(每个注入通道有专用寄存器)。

支持硬件触发(如定时器、外部事件)。

典型场景:

紧急信号采集(如过压、过流保护)。

需要低延迟的关键信号(如电机控制中的故障检测)。

与规则通道配合使用,实现“后台常规采样+事件触发紧急采样”。

(3). ③转换顺序

规则序列

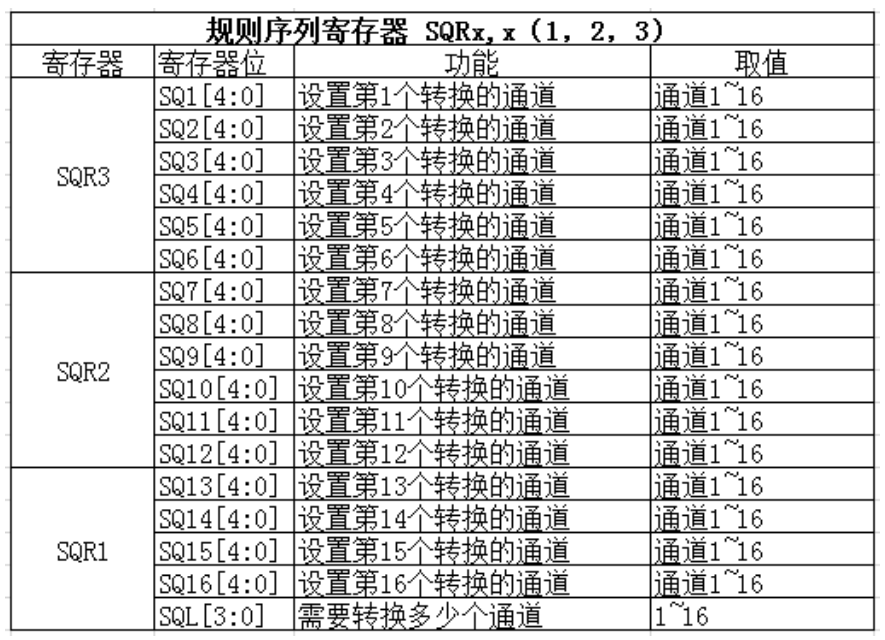

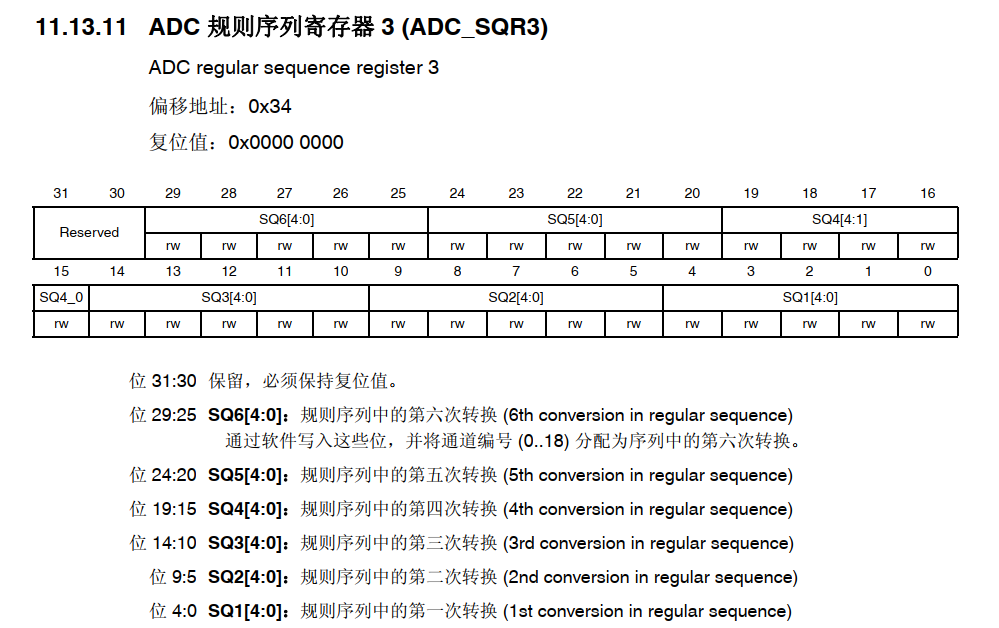

规则序列寄存器有 3 个,分别为 SQR3、 SQR2、 SQR1。 SQR3 控制着规则序列中的第一个到第六个转换,对应的位为: SQ1[4:0]~SQ6[4:0],第一次转换的是位 4:0 SQ1[4:0],如果通道 16 想第一次转换,那么在 SQ1[4:0]写 16 即可。 SQR2 控制着规则序列中的第 7 到第12 个转换,对应的位为: SQ7[4:0]~SQ12[4:0],如果通道 1 想第 8 个转换,则 SQ8[4:0]写 1即可。 SQR1 控制着规则序列中的第 13 到第 16 个转换,对应位为: SQ13[4:0]~SQ16[4:0],如果通道 6 想第 10 个转换,则 SQ10[4:0]写 6 即可。具体使用多少个通道,由 SQR1 的位L[3:0]决定,最多 16 个通道。

图 31-3 规则序列寄存器

注入序列

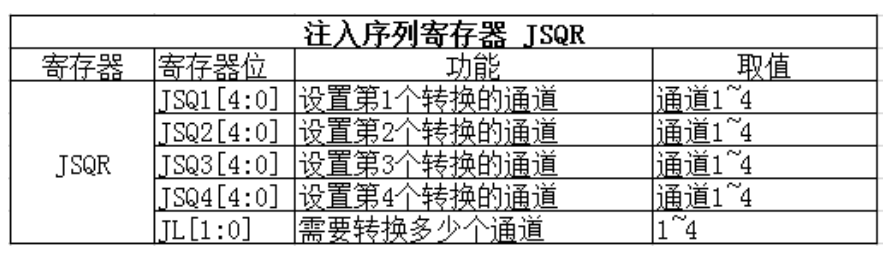

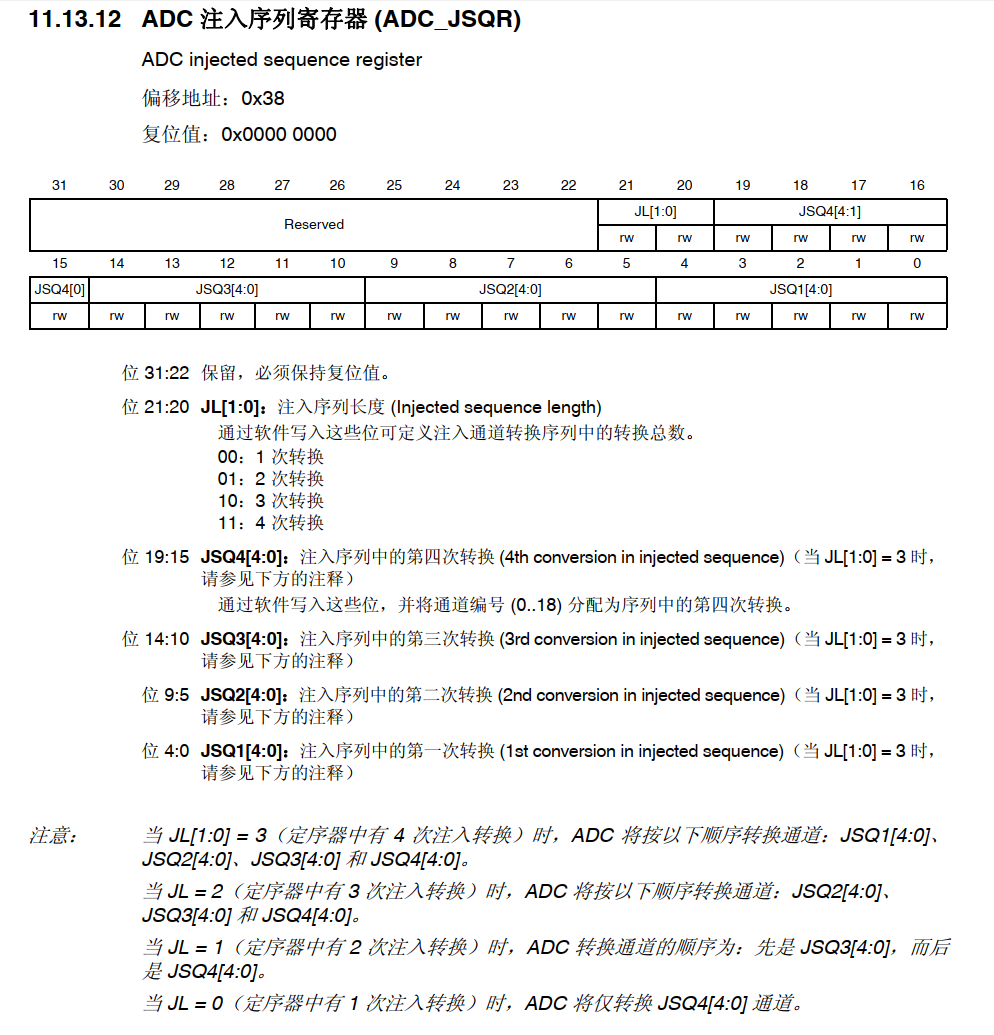

注入序列寄存器 JSQR 只有一个,最多支持 4 个通道,具体多少个由 JSQR 的 JL[1:0]决定。如果 JL 的 值小于 4 的话,则 JSQR 跟 SQR 决定转换顺序的设置不一样,第一次转换的不是 JSQR1[4:0],而是 JCQRx[4:0] , x = (4-JL),跟 SQR 刚好相反。比如 JL=01(2个转换),那么转换的顺序是从 JSQR3[4:0]开始,而不是从 JSQR1[4:0]开始,这个要注意,编程的时候不要搞错。

图 31-4 注入序列寄存器

(4). ④触发源

通道选好了,转换的顺序也设置好了,那接下来就该开始转换了。 ADC 转换可以由ADC 控制寄存器 2: ADC_CR2 的 ADON 这个位来控制,写 1 的时候开始转换,写 0 的时候停止转换,这个是最简单也是最好理解的开启 ADC 转换的控制方式,理解起来没啥技术含量。

除了这种庶民式的控制方法, ADC 还支持外部事件触发转换,这个触发包括内部定时器触发和外部 IO 触发。触发源有很多,具体选择哪一种触发源,由 ADC 控制寄存器2:ADC_CR2 的 EXTSEL[2:0]和 JEXTSEL[2:0]位来控制。 EXTSEL[2:0]用于选择规则通道的触发源, JEXTSEL[2:0]用于选择注入通道的触发源。选定好触发源之后,触发源是否要激活,则由 ADC 控制寄存器 2:ADC_CR2 的 EXTTRIG 和 JEXTTRIG 这两位来激活。

如果使能了外部触发事件,我们还可以通过设置 ADC 控制寄存器 2:ADC_CR2 的EXTEN[1:0]和 JEXTEN[1:0]来控制触发极性,可以有 4 种状态,分别是:禁止触发检测、上升沿检测、下降沿检测以及上升沿和下降沿均检测。

(5). ⑤转换时间

ADC 时钟

ADC 输入时钟 ADC_CLK 由 PCLK2 经过分频产生,最大值是 36MHz,典型值为30MHz,分频因子由 ADC 通用控制寄存器 ADC_CCR 的 ADCPRE[1:0]设置,可设置的分频系数有 2、 4、 6 和 8,注意这里没有 1 分频。对于 STM32F429IGT6 我们一般设置PCLK2=HCLK/2=84MHz。所以程序一般使用 4 分频或者 6 分频。

采样时间

ADC 需要若干个 ADC_CLK 周期完成对输入的电压进行采样,采样的周期数可通过ADC 采样时间寄存器 ADC_SMPR1 和 ADC_SMPR2 中的 SMP[2:0]位设置, ADC_SMPR2控制的是通道 0~9, ADC_SMPR1 控制的是通道 10~17。每个通道可以分别用不同的时间采样。其中采样周期最小是 3 个,即如果我们要达到最快的采样,那么应该设置采样周期为 3 个周期,这里说的周期就是 1/ADC_CLK。

ADC 的总转换时间跟 ADC 的输入时钟和采样时间有关,公式为:Tconv = 采样时间 + 12 个周期

当 ADCCLK = 30MHz,即 PCLK2 为 60MHz, ADC 时钟为 2 分频,采样时间设置为 3个周期,那么总的转换时为: Tconv = 3 + 12 = 15 个周期 =0.5us。

一般我们设置 PCLK2=84MHz,经过 ADC 预分频器能分频到最大的时钟只能是 21M,采样周期设置为 3 个周期,算出最短的转换时间为 0.7142us,这个才是最常用的。

(6). ⑥数据寄存器

一切准备就绪后, ADC 转换后的数据根据转换组的不同,规则组的数据放在ADC_DR 寄存器,注入组的数据放在 JDRx。 如果是使用双重或者三重模式那规矩组的数据是存放在通用规矩寄存器 ADC_CDR 内的。

规则数据寄存器 ADC_DR

ADC 规则组数据寄存器 ADC_DR 只有一个,是一个 32 位的寄存器, 只有低 16 位有效并且只是用于独立模式存放转换完成数据。因为 ADC 的最大精度是 12 位, ADC_DR 是16 位有效, 这样允许 ADC 存放数据时候选择左对齐或者右对齐,具体是以哪一种方式存放,由 ADC_CR2 的 11 位 ALIGN 设置。 假如设置 ADC 精度为 12 位,如果设置数据为左对齐,那 AD 转换完成数据存放在 ADC_DR 寄存器的[4:15]位内;如果为右对齐,则存放在 ADC_DR 寄存器的[0:11]位内。

规则通道可以有 16 个这么多,可规则数据寄存器只有一个, 如果使用多通道转换, 那转换的数据就全部都挤在了 DR 里面,前一个时间点转换的通道数据,就会被下一个时间点的另外一个通道转换的数据覆盖掉,所以当通道转换完成后就应该把数据取走,或者开启 DMA 模式,把数据传输到内存里面,不然就会造成数据的覆盖。 最常用的做法就是开启 DMA 传输。

如果没有使用 DMA 传输,我们一般都需要使用 ADC 状态寄存器 ADC_SR 获取当前ADC 转换的进度状态,进而进行程序控制。

注入数据寄存器 ADC_JDRx

ADC 注入组最多有 4 个通道,刚好注入数据寄存器也有 4 个,每个通道对应着自己的寄存器,不会跟规则寄存器那样产生数据覆盖的问题。 ADC_JDRx 是 32 位的,低 16 位有效,高 16 位保留,数据同样分为左对齐和右对齐,具体是以哪一种方式存放,由ADC_CR2 的 11 位 ALIGN 设置。

通用规则数据寄存器 ADC_CDR

规则数据寄存器 ADC_DR 是仅适用于独立模式的,而通用规则数据寄存器 ADC_CDR是适用于双重和三重模式的。独立模式就是仅仅适用三个 ADC 的其中一个,双重模式就是同时使用 ADC1 和 ADC2,而三重模式就是三个 ADC 同时使用。在双重或者三重模式下一般需要配合 DMA 数据传输使用。

(7). ⑦中断

中断分为四种:规则通道转换结束中断,注入转换通道转换结束中断,模拟看门狗中断和溢出中断。

转换结束中断

数据转换结束后,可以产生中断,转换结束中断很好理解,跟我们平时接触的中断一样,有相应的中断标志位和中断使能位,我们还可以根据中断类型写相应配套的中断服务程序。

模拟看门狗中断

当被 ADC 转换的模拟电压低于低阈值或者高于高阈值时,就会产生中断,前提是我们开启了模拟看门狗中断,其中低阈值和高阈值由 ADC_LTR 和 ADC_HTR 设置。例如我们设置高阈值是 2.5V,那么模拟电压超过 2.5V 的时候,就会产生模拟看门狗中断,反之低阈值也一样。

溢出中断

如果发生 DMA 传输数据丢失,会置位 ADC 状态寄存器 ADC_SR 的 OVR 位,如果同时使能了溢出中断,那在转换结束后会产生一个溢出中断。

DMA 请求

规则和注入通道转换结束后,除了产生中断外,还可以产生 DMA 请求,把转换好的数据直接存储在内存里面。 对于独立模式的多通道 AD 转换使用 DMA 传输非常有必须要,程序编程简化了很多。对于双重或三重模式使用 DMA 传输几乎可以说是必要的。 有关DMA 请求需要配合《STM32F4xx 中文参考手册》 DMA 控制器这一章节来学习。一般我们在使用 ADC 的时候都会开启 DMA 传输。

(8). ⑧电压转换

模拟电压经过 ADC 转换后,是一个相对精度的数字值,如果通过串口以 16 进制打印出来的话,可读性比较差,那么有时候我们就需要把数字电压转换成模拟电压,也可以跟实际的模拟电压(用万用表测)对比,看看转换是否准确。

我们一般在设计原理图的时候会把 ADC 的输入电压范围设定在: 0~3.3v, 如果设置ADC 为 12 位的,那么 12 位满量程对应的就是 3.3V, 12 位满量程对应的数字值是: 2^12。数值 0 对应的就是 0V。 如果转换后的数值为 X , X 对应的模拟电压为 Y,那么会有这么一个等式成立: 2^12 / 3.3 = X / Y, => Y = (3.3 * X ) / 2^12。

2、 ADC 初始化结构体详解

HAL 库函数对每个外设都建立了一个初始化结构体 xxx _HandleTypeDef (xxx 为外设名称),结构体成员用于设置外设工作参数,并由 HAL 库函数 HAL_xxx_Init() 调用这些设定参数进入设置外设相应的寄存器,达到配置外设工作环境的目的。

结构体 xxx__HandleTypeDef 和库函数 HAL_xxx_Init 配合使用是 HAL 库精髓所在,理解了结构体xxx_HandleTypeDef 每个成员意义基本上就可以对该外设运用自如了。结构体 xxx_HandleTypeDef定义在 stm32f4xx_hal_xxx.h 文件中,库函数 HAL_xxx_Init 定义在 stm32f4xx_hal_xxx.c 文件中,编程时我们可以结合这两个文件内注释使用。

2.1、ADC_HandleTypeDef 结构体

ADC_HandleTypeDef 结构体定义在 stm32f4xx_adc.h 文件内,具体定义如下:

typedef struct {

ADC_TypeDef *Instance; /* 寄存器基地址指针 */

ADC_InitTypeDef Init; /*ADC 初始化参数结构体 */

__IO uint32_t NbrOfCurrentConversionRank;//正在转换序列的 ADC 数目

DMA_HandleTypeDef *DMA_Handle; /* DMA 处理程序指针 */

HAL_LockTypeDef Lock; /*ADC 锁定对象 */

__IO uint32_t State; /*ADC 通信状态 */

__IO uint32_t ErrorCode; /*ADC 错误码 */

} ADC_HandleTypeDef;

*Instance: ADC 寄存器基地址指针,所有参数都是指定基地址后才能正确写入寄存器。

Init: ADC 初始化结构体,下面会详细讲解每一个成员。

*DMA_Handle: DMA 处理程序指针。

Lock: ADC 锁定对象。

State: ADC 转换状态。

ErrorCode: ADC 错误码。

2.2 、ADC_InitTypeDef 结构体

ADC_InitTypeDef 初始化结构体被 ADC_HandleTypeDef 结构体引用。

ADC_InitTypeDef 结构体定义在 stm32f4xx_hal_adc.h 文件内,具体定义如下:

typedef struct {

uint32_t ClockPrescaler; /*ADC 时钟分频系数 */

uint32_t Resolution; /*ADC 分辨率选择 */

uint32_t DataAlign; /* 输出数据对齐方式 */

uint32_t ScanConvMode; /* 扫描转换模式 */

uint32_t EOCSelection; /* 转换结束标志使用轮询或者中断 */

uint32_t ContinuousConvMode; /* 连续转换模式 */

uint32_t NbrOfConversion; /* 规格转换序列数目 */

uint32_t DiscontinuousConvMode; /* 不连续采样模式 */

uint32_t NbrOfDiscConversion; /* 不连续采样通道 */

uint32_t ExternalTrigConv; /* 外部事件触发选择 */

uint32_t ExternalTrigConvEdge; /* 外部事件触发极性 */

uint32_t DMAContinuousRequests; /*DMA 连续请求转换 */

} ADC_InitTypeDef;

ADC_Prescaler: ADC 时钟分频系数选择, ADC 时钟是有 PCLK2 分频而来,分频系数决定 ADC时钟频率,可选的分频系数为 2、 4、 6 和 8。 ADC 最大时钟配置为 36MHz。

ADC_Resolution:配置 ADC 的分辨率,可选的分辨率有 12 位、 10 位、 8 位和 6 位。分辨率越高,AD 转换数据精度越高,转换时间也越长;分辨率越低, AD 转换数据精度越低,转换时间也越短。

ADC_DataAlign:转换结果数据对齐模式,可选右对齐 ADC_DataAlign_Right 或者左对齐

ADC_DataAlign_Left。一般我们选择右对齐模式。

ScanConvMode:可选参数为 ENABLE 和 DISABLE,配置是否使用扫描。如果是单通道 AD 转换使用 DISABLE,如果是多通道 AD 转换使用 ENABLE。

EOCSelection:可选参数为 ENABLE 和 DISABLE,指定通过轮询和中断来使用 EOC(转换结束)标志进行转换。

ContinuousConvMode:可选参数为 ENABLE 和 DISABLE,配置是启动自动连续转换还是单次转换。使用 ENABLE 配置为使能自动连续转换;使用 DISABLE 配置为单次转换,转换一次后停止需要手动控制才重新启动转换。

NbrOfConversion: AD 规则转换通道数目。

DiscontinuousConvMode:不连续采样模式。一般为禁止模式。

NbrOfDiscConversion: ADC 不连续转换通道数目。

ExternalTrigConv:外部触发选择, 图 29_1 中列举了很多外部触发条件,可根据项目需求配置触发来源。实际上,我们一般使用软件自动触发。

ExternalTrigConvEdge:外部触发极性选择,如果使用外部触发,可以选择触发的极性,可选有禁止触发检测、上升沿触发检测、下降沿触发检测以及上升沿和下降沿均可触发检测。

DMAContinuousRequests: DMA 请求连续转换,开启 DMA 传输时用到。

2.3、ADC_ChannelConfTypeDef 结构体

ADC_ChannelConfTypeDef 结构体定义在 stm32f4xx_adc.h 文件内,具体定义如下:

typedef struct {

uint32_t Channel; /*ADC 转换通道 */

uint32_t Rank; /*ADC 序列数目 */

uint32_t SamplingTime; /*ADC 采样时间 */

uint32_t Offset; /* 预留未用到,设为 0 即可 */

} ADC_HandleTypeDef;

Channel: ADC 转换通道。

Rank: ADC 序列数目

SamplingTime: ADC 采样时间。

3、ADC使用方法

3.1、中断和DMA

在STM32的ADC应用中,中断(Interrupt)和DMA(Direct Memory Access)的选择取决于数据量、实时性要求和系统资源占用。以下是它们的适用场景和对比:

(1). 使用中断(Interrupt)的场景

适用情况:

单次采样或低频率采样:每次ADC转换完成后需要手动处理数据(如读取ADC_DR)。

注入通道的紧急事件:高优先级任务(如过压保护)需要立即响应。

非连续采样:仅在特定事件(如按键按下)触发ADC转换。

资源受限:当DMA通道被其他外设占用时。

优点:

实现简单,适合小数据量或非周期性任务。

可灵活处理单次转换结果(例如触发后续逻辑)。

缺点:

频繁中断会占用CPU资源,高频率采样时可能导致系统卡顿。

多通道连续采样时需频繁读取数据,效率低。

(2). 使用DMA的场景

适用情况:

连续高速采样:如音频信号采集、高频传感器数据(如IMU)。

多通道规则通道扫描:需自动存储多路ADC数据到数组。

低CPU占用需求:希望ADC数据传输不干扰主程序运行。

大数据量传输:配合定时器触发实现固定频率采样(如PWM+ADC+DMA)。

优点:

零CPU干预:DMA自动将ADC数据搬运到内存(如数组或缓冲区)。

高效支持多通道、连续采样(如配合ADC_ScanMode)。

适合实时性要求高的应用(如电机控制、示波器)。

缺点:

需要配置DMA通道,占用一定的内存资源(需预分配缓冲区)。

对简单任务可能“杀鸡用牛刀”。

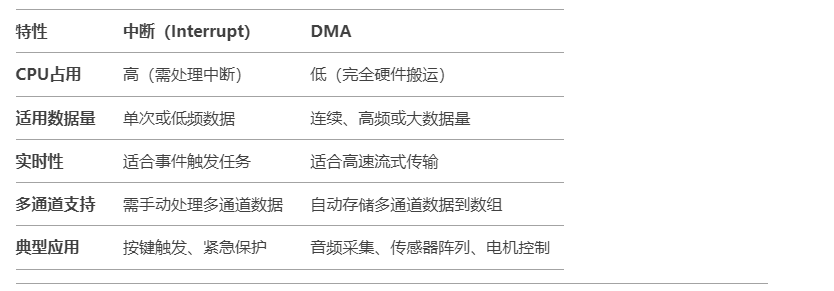

(3). 中断 vs DMA 对比总结

(4). 组合使用的高级场景

DMA+双缓冲(Double Buffer):

在高速采样时,配置DMA循环填充两个缓冲区,结合中断通知CPU切换缓冲区(避免数据覆盖)。

注入通道中断+规则通道DMA:

规则通道用DMA连续采样,注入通道用中断处理紧急事件(如STM32的电机驱动库常用此模式)。

选择建议

优先DMA:若需连续采样或多通道数据搬运(尤其是配合定时器触发)。

选择中断:若采样频率低(如每秒几次)或需灵活处理单次事件。

混合使用:对实时性要求苛刻的场景(如故障检测用中断,常规数据用DMA)。

3.2、独立、双重、三重

AD 转换包括采样阶段和转换阶段,在采样阶段才对通道数据进行采集;而在转换阶段只是将采集到的数据进行转换为数字量输出,此刻通道数据变化不会改变转换结果。独立模式的 ADC 采集需要在一个通道采集并且转换完成后才会进行下一个通道的采集。双重或者三重 ADC 的机制使用两个或以上 ADC 同时采样两个或以上不同通道的数据或者使用两个或以上 ADC 交叉采集同一通道的数据。双重或者三重 ADC 模式较独立模式一个最大的优势就是转换速度快。

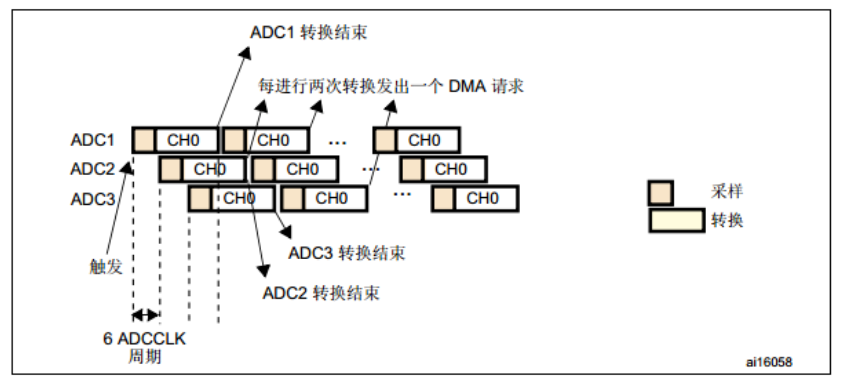

我们这里只介绍三重 ADC 交替模式,关于双重或者三重 ADC 的其他模式与之类似,可以参考三重 ADC 交替模式使用。三重 ADC 交替模式是针对同一通道的使用三个 ADC 交叉采集,就是在 ADC1 采样完等几个时钟周期后 ADC2 开始采样,此时 ADC1 处在转换阶段,当 ADC2 采样完成再等几个时钟周期后 ADC3 就进行采样此时 ADC1 和 ADC2 处在转换阶段,如果 ADC3 采样完成并且 ADC1 已经转换完成那么就可以准备下一轮的循环,这样充分利用转换阶段时间达到增快采样速度的效果。 AD 转换过程见图 29_6,利用 ADC 的转换阶段时间另外一个 ADC 进行采样,而不用像独立模式必须等待采样和转换结束后才进行下一次采样及转换。

图 29‑6 三重 ADC 同步规则模式

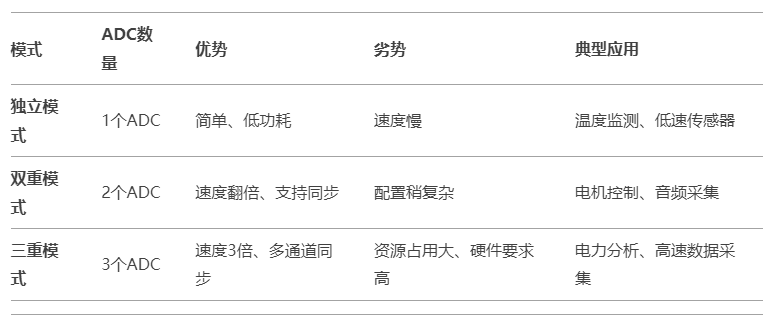

在STM32的ADC模块中,独立模式(Independent)、双重模式(Dual)和三重模式(Triple)的选择主要取决于采样速度、同步需求和系统复杂度。以下是它们的详细对比和使用场景:

(1). 独立模式(Independent Mode)

特点:

单个ADC独立工作,无与其他ADC的协同。

适用于简单的单路或多路顺序采样。

资源占用最少,配置简单。

适用场景:

低速率、单通道或多通道轮流采样(如温度、电池电压监测)。

对采样速度要求不高(如每秒几次采样)。

项目初期验证或资源受限时。

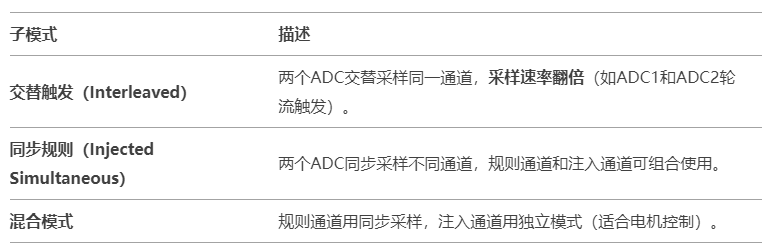

(2). 双重模式(Dual Mode)

特点:

两个ADC协同工作(如ADC1+ADC2),可同步采样或交替采样。

提高采样速率:通过并行采样或交替触发,实现更高频率的数据采集。

支持多种子模式(如交替触发、同步规则通道等)。

常见子模式:

适用场景:

高速信号采集(如音频信号、振动传感器)。

需要同步采样的多通道系统(如三相电流检测)。

电机控制中同步采样电流和电压(配合PWM触发)。

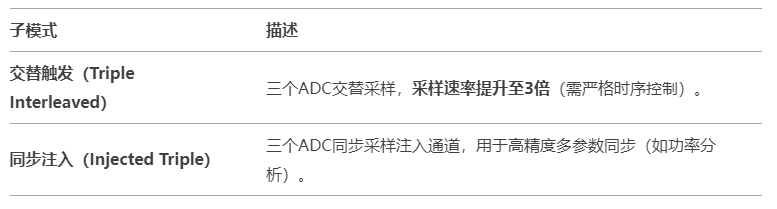

(3). 三重模式(Triple Mode)

特点:

三个ADC协同工作(ADC1+ADC2+ADC3),进一步提速或增强同步能力。

适用于超高精度或超高速场景(如电力分析仪、专业示波器)。

资源占用大,配置复杂(需平衡触发时序和DMA设置)。

常见子模式:

适用场景:

超高频信号采集(如射频信号、高速示波器)。

多参数严格同步(如三相电力系统的电压、电流、相位同步检测)。

专业测量设备(如医疗仪器、工业质检)。

(4). 模式对比总结

(5). 选择建议

独立模式:

适用于大多数低复杂度应用(如环境监测、简单控制回路)。

优先在资源受限或低功耗场景使用。

双重模式:

需要提高采样率或同步多通道时选择(如电机驱动的电流电压同步采样)。

推荐子模式:

交替触发:单通道高速采样(如示波器)。

同步规则+注入:电机控制中的实时保护(如过流检测)。

三重模式:

仅用于专业级高速、高精度设备(如电力谐波分析、多通道示波器)。

需注意硬件支持和时序校准(可能需硬件触发同步)。

(6). 实际案例

案例1:电机控制(双重模式)

需求:同步采样三相电流(Ia, Ib, Ic)和母线电压。

方案:

ADC1和ADC2配置为同步规则模式,分别采样电流和电压。

注入通道用于过流保护(中断触发)。

使用PWM定时器触发ADC采样,确保与PWM波形同步。

案例2:音频采集(交替双重模式)

需求:采集麦克风信号(采样率48kHz)。

方案:

ADC1和ADC2设置为交替触发模式,实际采样率提升至96kHz。

通过DMA将数据存入环形缓冲区,供后续数字信号处理(如FFT)。

总结

独立模式是默认选择,满足大多数基础需求。

双重/三重模式用于突破性能瓶颈或实现多参数同步,但需权衡硬件资源和配置复杂度。

在电机控制、能源计量等实时性要求高的领域,双重模式尤为常见。

浙公网安备 33010602011771号

浙公网安备 33010602011771号