1、搭建

![]()

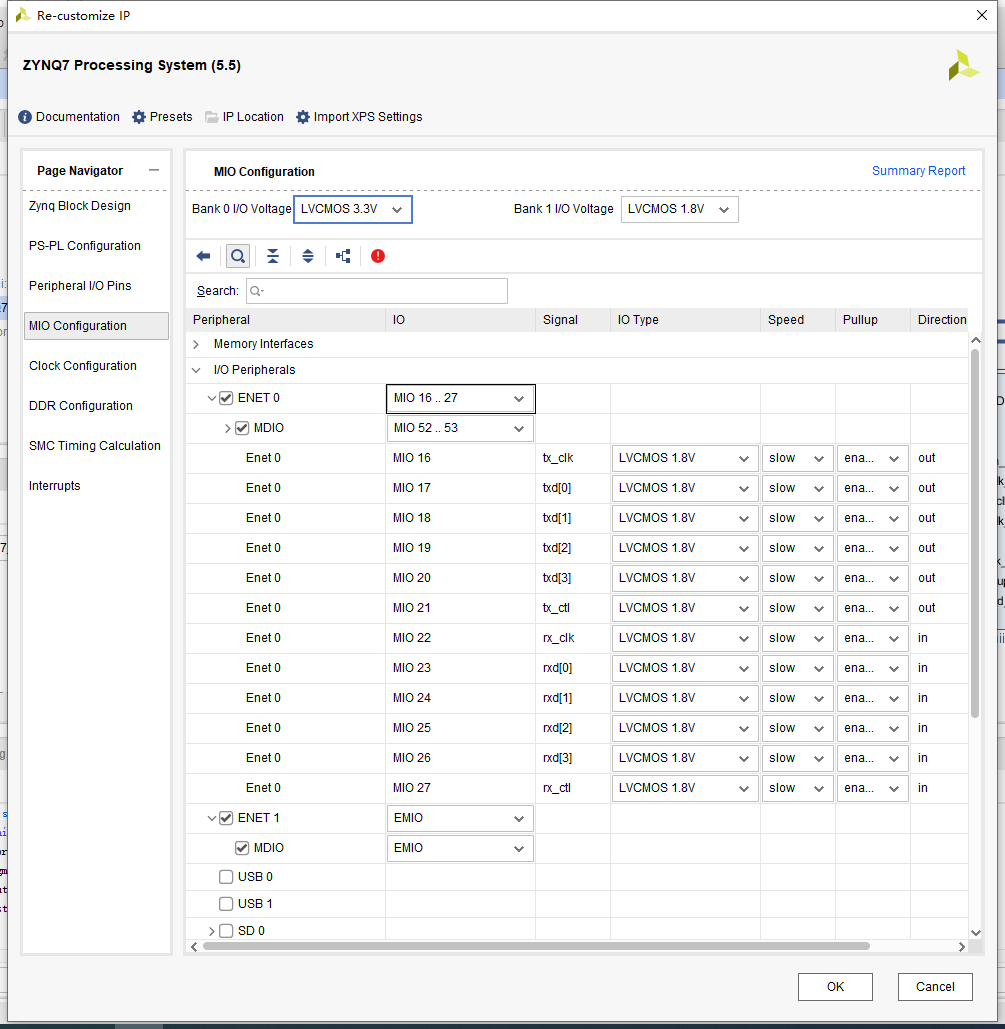

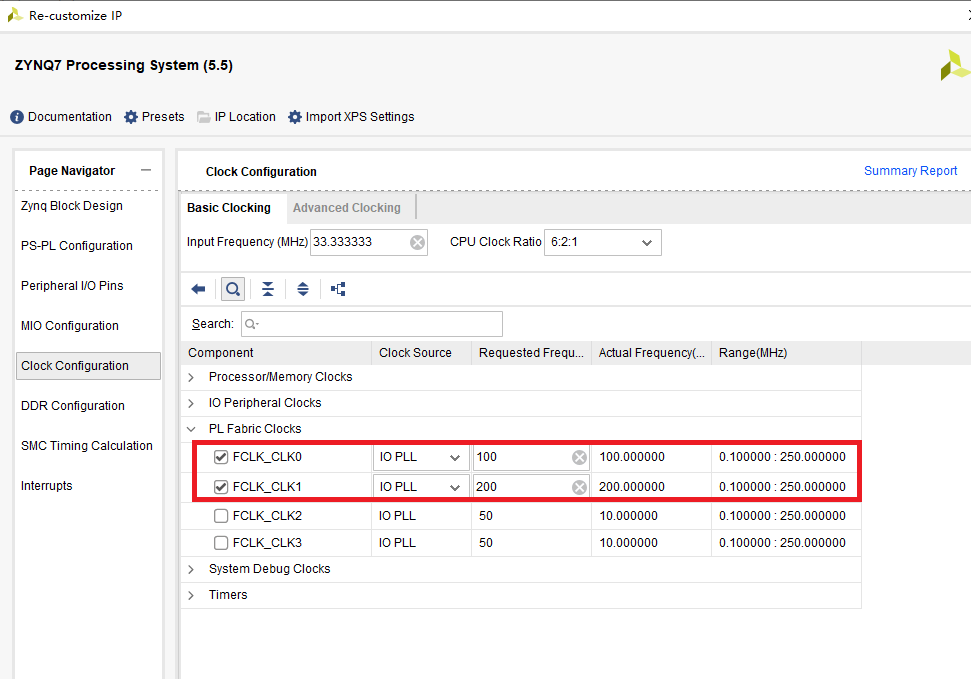

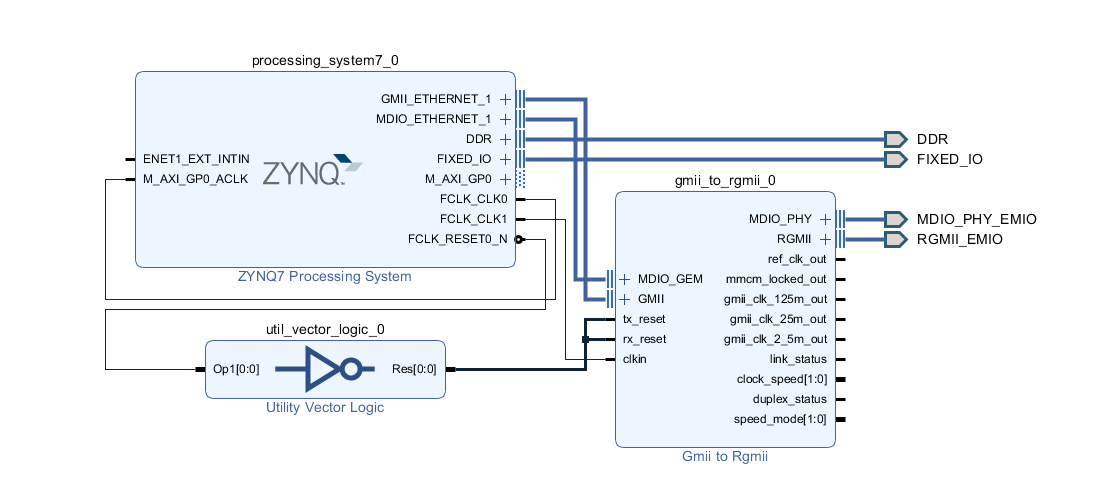

将 FCLK_CLK0 设置为 200M,作为 GMII to RGMII IP 核内部 IDELAYCTRL 的参考时钟。

![]()

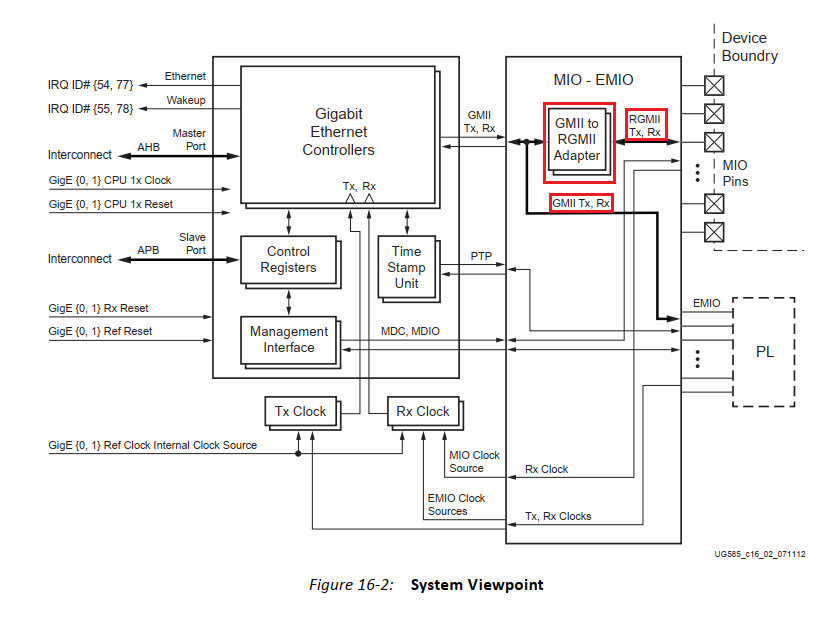

如下图所示,由于zynq ps端网络在使用EMIO引脚时引出的是GMII,所以需要添加一个GMII to RGMII IP 核。

![]()

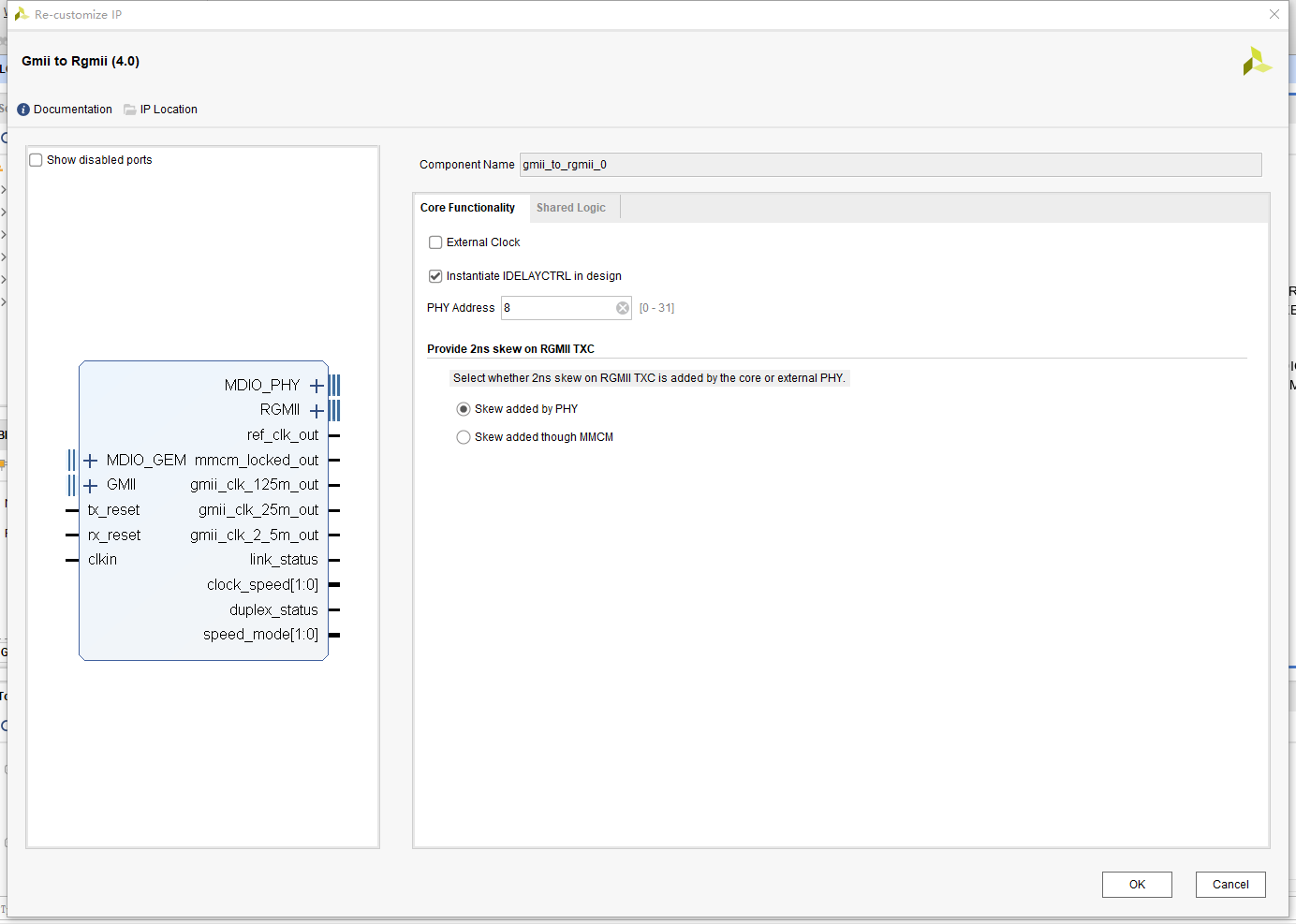

GMII to RGMII IP 核配置:

在 HR BANK 中,IP 核中 RGMII 接口的接收数据信号和控制信号需要通过 IDELAYE2 来调整信号输入延时,使其时序满足建立和保持时间约束。因此需要在 IP 核包含与 IDELAYE2 相关的 IDELAYCTRL,用来校准 IDELAYE2 每个延时 tap 的延时值。

将本 IP 核的 PHY address 设置为 8(该值可任意设置,但不能与现有的 PHY address 相同,否则将产生冲突使 IP 核工作异常)。

![]()

选择 shared logic 包含在 IP 核内部。

![]()

Utility Vector Logic 添加:

配置 Utility Vector Logic 为非门,将 FCLK_RESET0_N 通过后作为 GMII to RGMII IP 核的复位信号,因为GMII to RGMII IP 核为高电平复位。

![]()

![]()

2、引脚配置

set_property PACKAGE_PIN V5 [get_ports MDIO_PHY_EMIO_mdc]

set_property PACKAGE_PIN H17 [get_ports MDIO_PHY_EMIO_mdio_io]

set_property PACKAGE_PIN Y7 [get_ports RGMII_EMIO_rxc]

set_property PACKAGE_PIN Y6 [get_ports RGMII_EMIO_rx_ctl]

set_property PACKAGE_PIN Y9 [get_ports {RGMII_EMIO_rd[0]}]

set_property PACKAGE_PIN Y8 [get_ports {RGMII_EMIO_rd[1]}]

set_property PACKAGE_PIN V8 [get_ports {RGMII_EMIO_rd[2]}]

set_property PACKAGE_PIN W8 [get_ports {RGMII_EMIO_rd[3]}]

set_property PACKAGE_PIN Y12 [get_ports RGMII_EMIO_txc]

set_property PACKAGE_PIN W9 [get_ports RGMII_EMIO_tx_ctl]

set_property PACKAGE_PIN Y13 [get_ports {RGMII_EMIO_td[0]}]

set_property PACKAGE_PIN W11 [get_ports {RGMII_EMIO_td[1]}]

set_property PACKAGE_PIN Y11 [get_ports {RGMII_EMIO_td[2]}]

set_property PACKAGE_PIN W10 [get_ports {RGMII_EMIO_td[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports MDIO_PHY_EMIO_mdc]

set_property IOSTANDARD LVCMOS33 [get_ports MDIO_PHY_EMIO_mdio_io]

set_property IOSTANDARD LVCMOS18 [get_ports RGMII_EMIO_rxc]

set_property IOSTANDARD LVCMOS18 [get_ports RGMII_EMIO_rx_ctl]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_rd[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_rd[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_rd[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_rd[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports RGMII_EMIO_txc]

set_property IOSTANDARD LVCMOS18 [get_ports RGMII_EMIO_tx_ctl]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_td[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_td[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_td[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGMII_EMIO_td[3]}]

set_property SLEW FAST [get_ports RGMII_EMIO_txc]

set_property SLEW FAST [get_ports RGMII_EMIO_tx_ctl]

set_property SLEW FAST [get_ports {RGMII_EMIO_td[*}]

create_clock -period 8.000 -name RGMII_EMIO_rx_clk [get_ports RGMII_EMIO_rxc]

set_input_delay -clock [get_clocks RGMII_EMIO_rx_clk] -max 2.800 [get_ports {{RGMII_EMIO_rd[*]} RGMII_EMIO_rx_ctl}]

set_input_delay -clock [get_clocks RGMII_EMIO_rx_clk] -min 1.200 [get_ports {{RGMII_EMIO_rd[*]} RGMII_EMIO_rx_ctl}]

set_input_delay -clock [get_clocks RGMII_EMIO_rx_clk] -clock_fall -max -add_delay 2.800 [get_ports {{RGMII_EMIO_rd[*]} RGMII_EMIO_rx_ctl}]

set_input_delay -clock [get_clocks RGMII_EMIO_rx_clk] -clock_fall -min -add_delay 1.200 [get_ports {{RGMII_EMIO_rd[*]} RGMII_EMIO_rx_ctl}]

3、程序配置

lwip配置见https://www.cnblogs.com/The-explosion/p/18778629

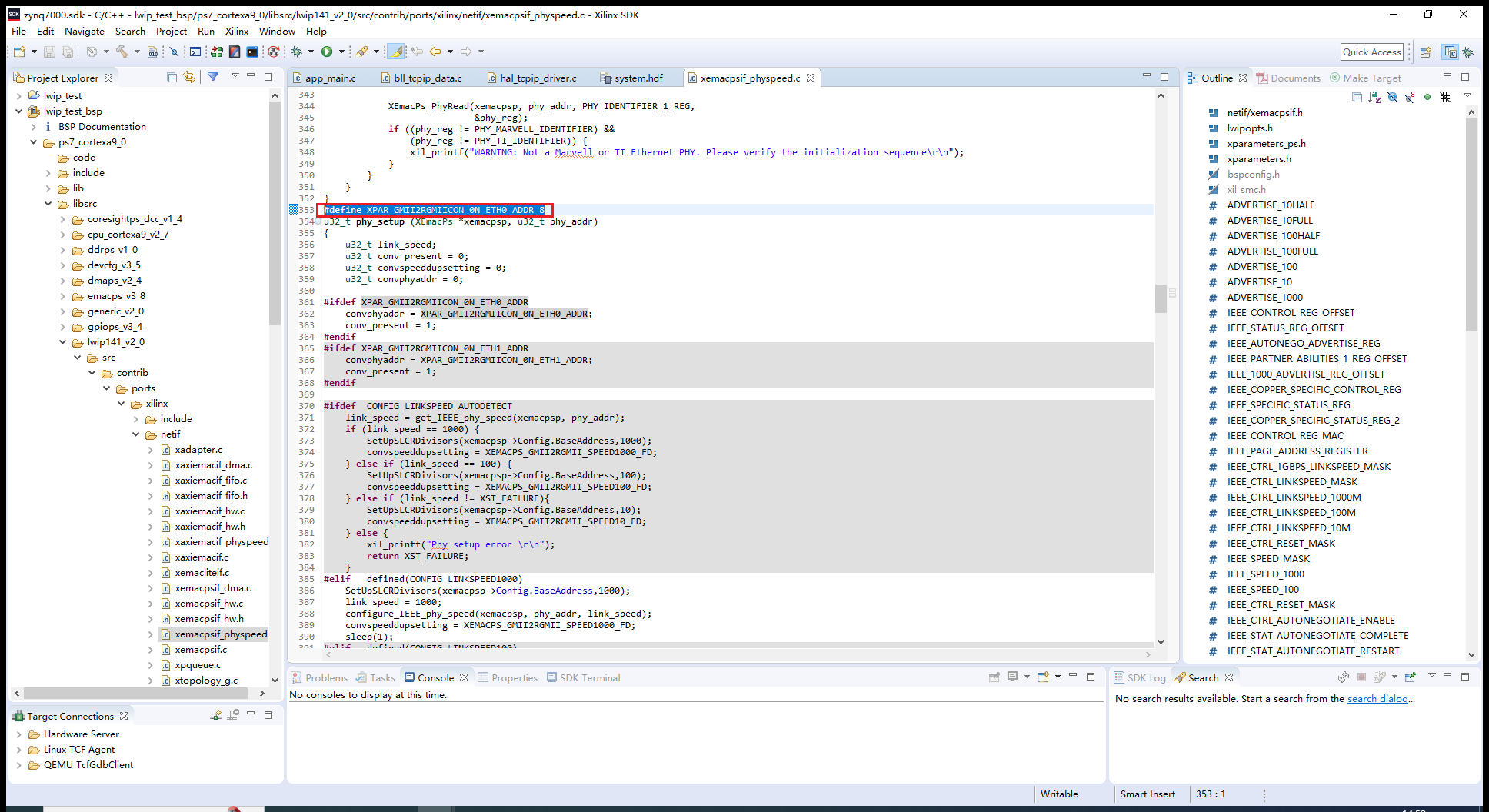

在使用lwip时要在phy_setup()函数前面加上宏定义#define XPAR_GMII2RGMIICON_0N_ETH0_ADDR 8,即GMII to RGMII IP 核的地址

![]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号