DCache的使用

1、APU(应用处理器单元)

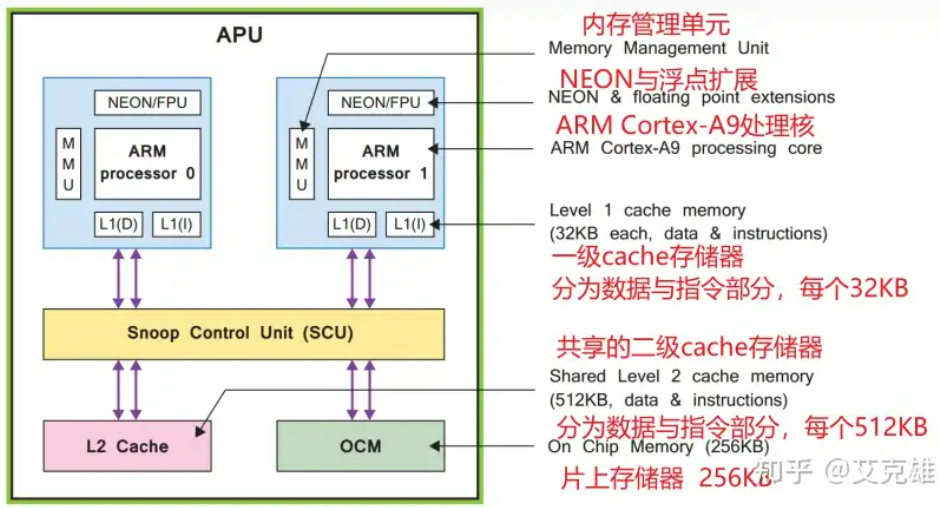

如上图所示是 APU 的简化框图。APU 主要是由两个 ARM 处理器核组成的,每个都关联了一些可计算的单元:一个 NEONTM 媒体处理引擎(Media Processing Engine,MPE)和浮点单元(Floating PointUnit,FPU);一个内存管理单元(Memory Management Unit,MMU);和一个一级 cache 存储器(分为指令和数据两个部分)。APU 里还有一个二级 cache 存储器,再往下还有片上存储器(On Chip Memory,OCM),这些是两个 ARM 处理器共用的。最后,由一个一致性控制单元(Snoop Control Unit,SCU)在ARM 核和二级 cache 及 OCM 存储器之间形成了桥连接。SCU 还部分负责与 PL 对接,图中没有标出这个接口。

PS通过DMA向PL写数据

1)调用:Xil_DCacheFlushRange(INTPTR adr, u32 len);

2)DMA写PL:XAXIDMA_DMA_TO_DEVICE

PS通过DMA从PL读数据

1)DMA读PL:XAXIDMA_DEVICE_TO_DMA

2)调用:Xil_DCacheInvalidateRange(INTPTR adr, u32 len)

浙公网安备 33010602011771号

浙公网安备 33010602011771号