STM32简介

1、STM32 分类

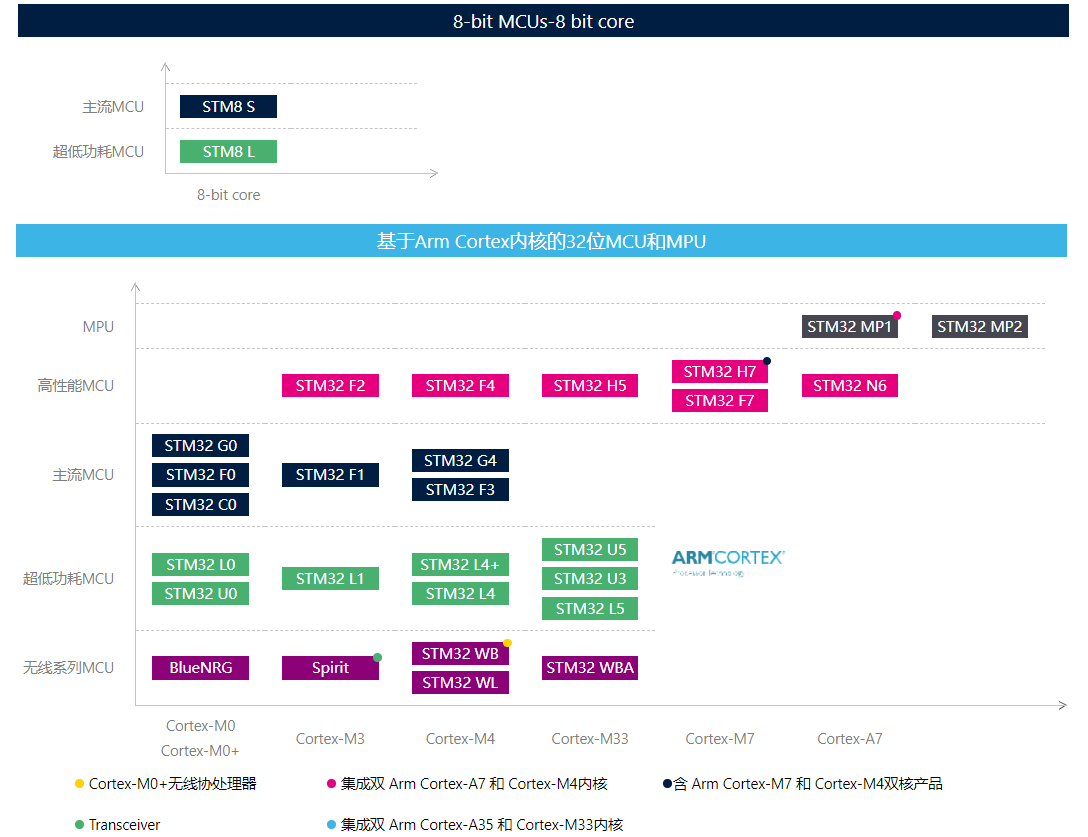

STM32 系列是目前嵌入式开发中应用最广泛的 ARM Cortex-M 微控制器平台之一,覆盖从入门级控制器到高性能边缘处理器的多种应用场景。STM32 有很多系列,可以满足市场的各种需求,从内核上分有 Cortex-M0、 M3、 M4和 M7 这几种,每个内核又大概分为主流、高性能和低功耗。单纯从学习的角度出发,可以选择 F1 和 F4, F1 代表了基础型,基于 Cortex-M3 内核,主频为 72MHZ,F4 代表了高性能,基于 Cortex-M4 内核,主频F407 168M,F429 180M。至于 F1, F4(429 系列以上)除了内核不同和主频的提升外,升级的明显特色就是带了 LCD 控制器和摄像头接口,支持 SDRAM,这个区别在项目选型上会被优先考虑。

1.1、STM32 平台家族总览:F/L/G/H/U/W 系列全景

STM32 是 STMicroelectronics(意法半导体)基于 ARM Cortex-M 内核开发的 32 位 MCU 平台,自 2007 年推出以来,已形成多个产品子系列,涵盖从入门级、主流型到高性能与低功耗的各类应用场景。系列划分遵循以字母命名的方式,具有鲜明的功能定位和性能层级。

(1)STM32F 系列:经典通用型 MCU 代表

定位:应用最广泛的通用型系列,适合大多数裸机或轻量级 RTOS 应用。

代表型号:

STM32F0:Cortex-M0,超低成本,适合简易控制器(如继电器控制)

STM32F1:Cortex-M3,工业控制经典型号(如 STM32F103)

STM32F3:Cortex-M4,集成模拟功能(如高精度 ADC、OpAmp)

STM32F4:Cortex-M4,高主频(最高 180MHz)、广泛应用于音频、传感

STM32F7:Cortex-M7,面向图形 UI、边缘计算与音视频处理

特性小结:

Flash 从 16KB 到 2MB,RAM 最多可达 512KB

支持外设种类齐全,开发生态最完善

适合绝大多数需要稳定性与性价比的嵌入式系统

(2)STM32L 系列:超低功耗优化专用

定位:主打电池供电、能耗敏感场景的超低功耗设计。

代表型号:

STM32L0:Cortex-M0+,低频低功耗,适合 IoT 节点

STM32L1:Cortex-M3,支持 EEPROM 模拟

STM32L4:Cortex-M4,平衡功耗与性能(如 STM32L432)

STM32L5:Cortex-M33,带 TrustZone 安全扩展

特性小结:

内建多种低功耗工作模式(Sleep / Stop / Standby)

电流最低可至 50nA(Standby),运行功耗仅 30μA/MHz

常用于可穿戴设备、智能表计、环境监测等领域

(3)STM32G 系列:高性价比 + 安全性强化

定位:新一代通用系列,结合 F1 的通用性与 L4 的低功耗特性,并引入硬件安全模块。

代表型号:

STM32G0:Cortex-M0+,GPIO 数多,集成度高,适合家电控制

STM32G4:Cortex-M4,具备高精度模拟外设(OpAmp、DAC、Comp)

特性小结:

全面替代 F0/F1 的优选方案

引入 AES、真随机数发生器(TRNG)、写保护等安全机制

成本优化型工业、消费电子应用首选

(4)STM32H 系列:高性能边缘计算平台

定位:面向边缘 AI 推理、复杂运算、多媒体接口的高性能 MCU。

代表型号:

STM32H7:Cortex-M7(或双核 M7+M4),频率高达 550MHz,带 DCache/ICache

支持 32-bit SDRAM、LCD、Camera、Ethernet、CAN FD 等复杂外设

特性小结:

Flash 可达 2MB,RAM 可达 1MB+

支持图像加速、硬件浮点、DSP 运算指令

常用于工业视觉、边缘智能控制、HMI 系统

(5)STM32U 系列:下一代超低功耗 MCU

定位:更先进的低功耗架构,补足 L 系列性能不足的问题。

代表型号:

STM32U5:Cortex-M33,结合低功耗与高性能,符合最新安全标准

特性小结:

高达 160MHz 主频,低至 19uA/MHz 功耗

引入高级安全机制(PSA 认证)

适用于医疗、金融安全认证、IoT 终端等场景

(6)STM32W 系列:无线通信集成 MCU

定位:集成 BLE、Zigbee、Thread 等无线协议栈的 SoC 方案。

代表型号:

STM32WB:双核 Cortex-M4 + M0,适合 BLE Mesh、Zigbee 网关

STM32WL:Cortex-M4 + Sub-GHz 射频(LoRa/FSK)

特性小结:

原生支持无线协议,无需外挂模块

封装紧凑,成本控制优秀

适合智能门锁、无线传感器网络、智能仪表等无线嵌入式场景

(7)系列选型导航总结

1.2、核心架构与性能差异:Cortex-M0 / M3 / M4 / M7 核心对比

在 STM32 各子系列的型号选择过程中,理解其底层所采用的 ARM Cortex-M 核心架构是进行合理选型与系统性能评估的关键。Cortex-M0、M3、M4、M7 是目前嵌入式领域广泛应用的主力核心,各自有着不同的性能、指令集支持、外设集成能力与功耗特性。

(1) Cortex-M0 / M0+:极简内核设计,主打低成本与低功耗

特性简述:

架构:ARMv6-M

主频范围:24MHz ~ 64MHz(具体取决于芯片)

不支持浮点运算(无 FPU)

指令集:仅支持 Thumb(16-bit)指令,指令数量少,执行快但功能受限

中断机制:基本 NVIC 支持,最多支持 32 个外部中断

典型应用:

简单 IO 控制、继电器驱动、电机启动逻辑、低速传感器采样等

STM32G0、STM32L0、STM32F0 等广泛使用此内核

优势总结:

芯片封装小、成本低、电流小(适用于电池供电系统)

代码体积小,启动时间快

(2)Cortex-M3:嵌入式工业控制的里程碑内核

特性简述:

架构:ARMv7-M

主频范围:最多可达 100MHz

更强的中断控制能力,支持更复杂的异常处理

支持 Thumb-2 指令集(16/32-bit 混合),兼顾代码密度与功能扩展

无 FPU,需软件模拟浮点运算

典型应用:

工业自动化、智能仪表、家电主控系统

STM32F1(如 F103)与 STM32L1 使用此核心

对比优势:

相比 M0 性能提升 1.5~2 倍,支持更复杂控制任务

稳定性和兼容性高,是众多老旧工业设备的首选架构

(3)Cortex-M4:嵌入式数字信号处理的黄金平衡点

特性简述:

架构:ARMv7E-M

主频范围:最高至 180MHz(STM32F4 系列)

支持单精度 FPU(浮点硬件加速)

增加了 DSP 指令集(MAC、SIMD 操作等)

NVIC 中断数量扩展,系统响应能力增强

典型应用:

语音识别、振动分析、实时控制系统

STM32F3/F4/G4/L4 系列为主力采用 M4 架构

优势总结:

功能覆盖广:支持信号处理任务的同时保持良好功耗比

与 CMSIS-DSP、TensorFlow Lite Micro 等生态兼容性强

在大多数 RTOS 场景下表现优秀(如 FreeRTOS)

(4) Cortex-M7:高性能嵌入式核心,支持边缘智能运算

特性简述:

架构:ARMv7E-M(增强版)

主频高达 550MHz(STM32H7 系列)

支持双精度 FPU(FPU-D)与增强 DSP 指令

具备 I-Cache、D-Cache,多级 Bus Matrix 接口

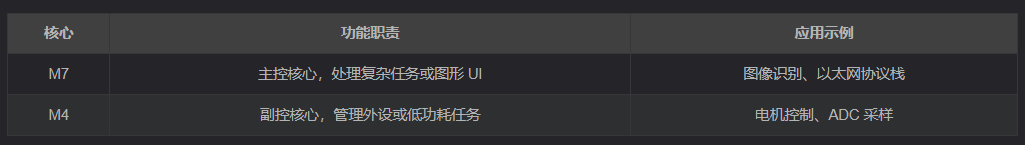

可选多核(如 STM32H747 的 M7+M4 架构)

典型应用:

HMI(图形交互)、实时 AI 推理、语音识别前处理、工业图像处理

STM32H7 是高性能 MCU 的代表

对比优势:

运算密集型任务可在 MCU 内直接运行,无需外部 MPU 或 DSP

在裸机系统下就具备非常强的实时运算能力

支持异构多核协同运算场景(如主控与低功耗子系统并行处理)

2.5 多核结构引入的调度模型(以 STM32H747 为例)

STM32H7 系列部分型号引入双核结构(M7 + M4),典型架构如下:

通过共享 SRAM、互斥机制(如硬件信号量 HSEM)、双核 RTOS(如 OpenAMP)等技术手段,支持分布式任务调度与资源复用。

(6)性能对比小结(CoreMark / MHz 参考)

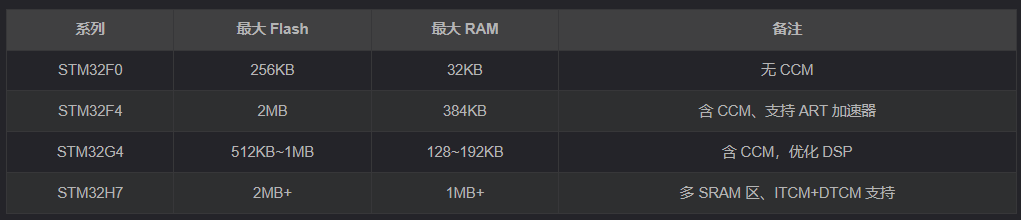

1.3、存储资源与封装选型策略(Flash / RAM / 封装兼容性)

在 STM32 平台的实际项目部署中,SoC 的选型不仅仅关乎主频与内核性能,Flash 与 RAM 的大小分配、存储类型结构,以及芯片封装兼容性往往决定了后续软件架构的灵活度、系统稳定性和量产过程的复杂性。本章将围绕 STM32 的典型存储体系与封装策略展开实战分析。

(1)STM32 Flash / RAM 架构基本模型

STM32 MCU 通常包含以下几类存储区域:

Main Flash:代码与常量数据存储区,支持 XIP(execute-in-place)

SRAM(内部 RAM):运行时数据区,分为多个 bank(如 SRAM1 / SRAM2)

CCM RAM(core-coupled memory):与 Cortex-M 核心耦合的高速 RAM,仅供核心访问,不支持 DMA

ITCM / DTCM(M7 专用):指令/数据 tightly-coupled memory,高性能片上缓存

EEPROM / Data Flash(部分 L 系列):专用数据持久化区

资源对比示例(部分 STM32 系列):

(2)Flash 容量选型:程序规模 + OTA + 配置空间预算

程序代码大小估算应结合以下因素:

启动代码 + 外设初始化(通常 < 16KB)

RTOS + 应用逻辑体积(取决于模块数量)

OTA 升级需求:留足备用镜像空间(至少双倍程序区)

字符串 / 配置表 / 常量表等存储区预留

实战建议:

STM32F103 开发板搭载 128~512KB Flash 足以完成 RTOS + 通讯协议栈 + 常规 UI

若需集成 BLE、USB Host 或图形库,建议选择 ≥1MB Flash(如 STM32F407、STM32G4)

(3)RAM 容量规划:栈、堆、缓冲区与外设交互的资源管理

RAM 使用常见分布:

系统栈(~1KB per task)

堆空间(如 new/delete、malloc 分配)

DMA 缓冲区、音频数据、图像帧缓存

配置缓存与状态表

常见瓶颈:图像缓存(QVGA 320x240 = 150KB)/ 语音采集(16KHz × 2ch × 秒级缓存)

工程建议:

嵌入式语音识别或视频分析推荐选择 STM32H7(>512KB RAM)

RAM 不足时可考虑外扩 PSRAM 或 SRAM 芯片 + FSMC 接口(需 MCU 支持)

(4)ROM 常量组织策略:利用 const + section 定位到 Flash 区

所有 const 全局变量将默认放入 Flash(.rodata 段)

可配合链接脚本进行手动段定位(如 section(".constdata"))

配合 BootLoader 与配置分区管理提升可维护性

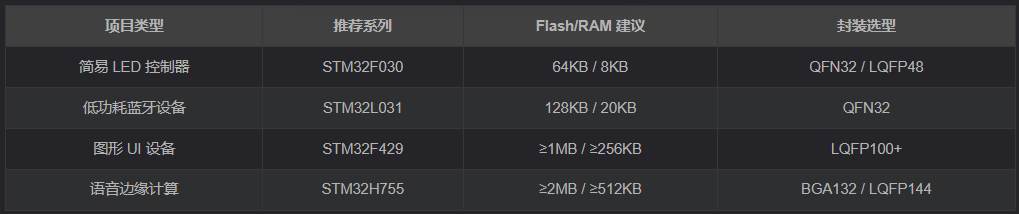

(5)封装类型选择:引脚复用、焊接方式与兼容系列策略

常见封装形式:

选型策略:

预留扩展方案:如初期选择 LQFP64,未来可替换为 LQFP100 同内核兼容版本

避免“资源浪费”:小项目选择 QFN32/48 能控制成本与功耗

大项目优先考虑封装系列兼容(如 STM32G431 与 G474 可做 drop-in 替换)

(6)实战选型建议模板(按项目场景)

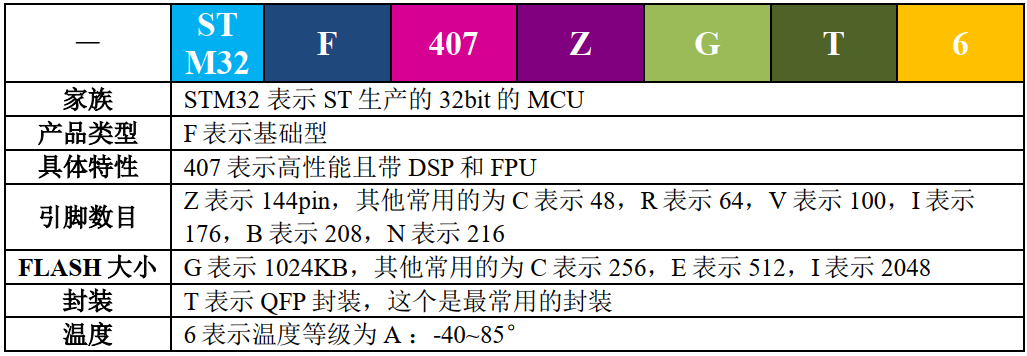

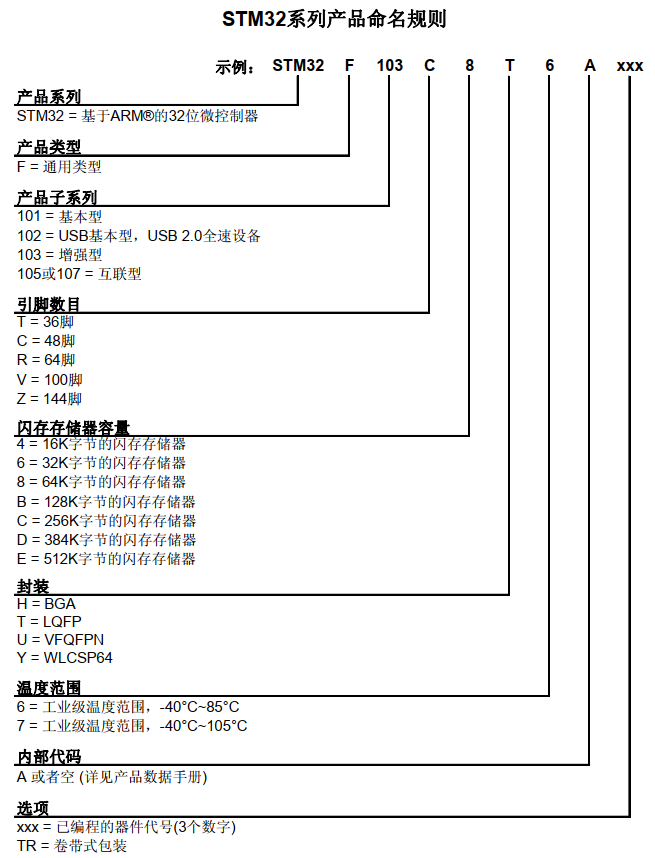

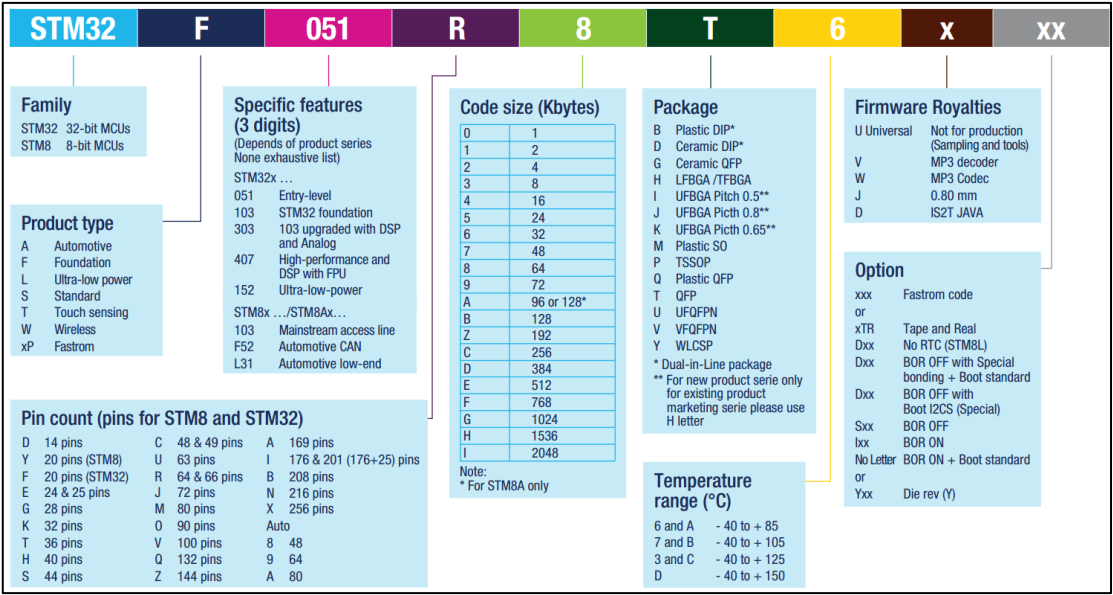

2、STM32的命名规则

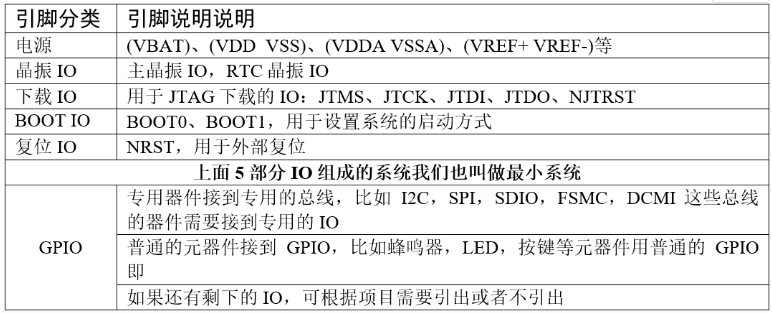

3、引脚分类

4、芯片内部架构

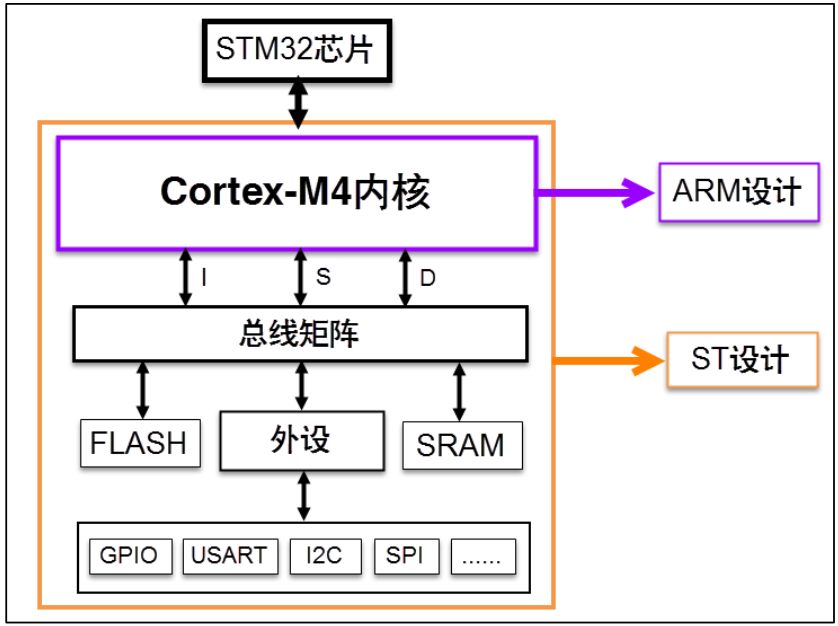

我们看到的 STM32 芯片已经是已经封装好的成品,主要由内核和片上外设组成。若与电脑类比,内核与外设就如同电脑上的 CPU 与主板、内存、显卡、硬盘的关系。

STM32F407 采用的是 Cortex-M4 内核,内核即 CPU,由 ARM 公司设计。 ARM 公司并不生产芯片,而是出售其芯片技术授权。芯片生产厂商(SOC)如 ST、 TI、 Freescale,负责在内核之外设计部件并生产整个芯片,这些内核之外的部件被称为核外外设或片上外设。如 GPIO、 USART(串口)、 I2C、 SPI 等都叫做片上外设。具体见下图:

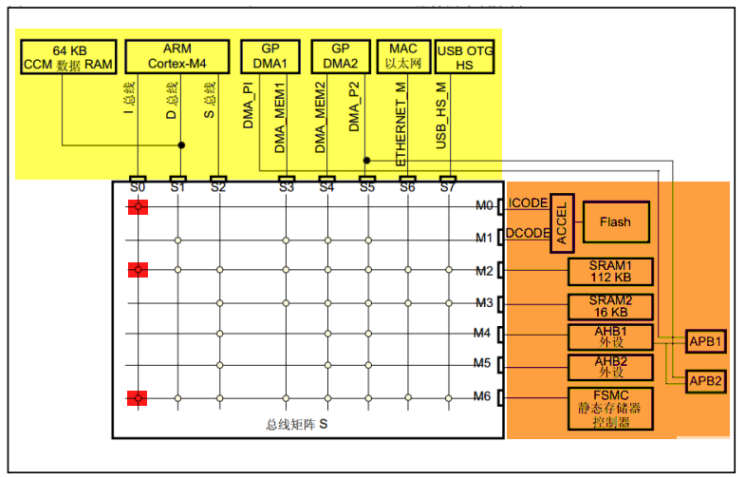

芯片内核和外设之间通过各种总线连接,其中主控总线有 8 条,被控总线有 7 条,具体见图 6-4。主控总线通过一个总线矩阵来连接被控总线, 总线矩阵用于主控总线之间的访问仲裁管理,仲裁采用循环调度算法。总线之间交叉的时候如果有个圆圈则表示可以通信,没有圆圈则表示不可以通信。比如 S0: I 总线只有跟 M0、 M2 和 M6 这三根被控总线交叉的时候才有圆圈,就表示 S0 只能跟这三根被控总线通信。从功能上来理解, I 总线是指令总线,用来取指,指令指的是编译好的程序指令。我们知道 STM32 有三种启动方式,从 FLASH 启动(包含系统存储器),从内部 SRAM 启动,从外部 RAM 启动,这三种存储器刚好对应的就是 M0、M2 和 M6 这三条总线。

图 6-4 STM32F05xx 和 STM32F407xx 器件的总线接口

5、存储器映射

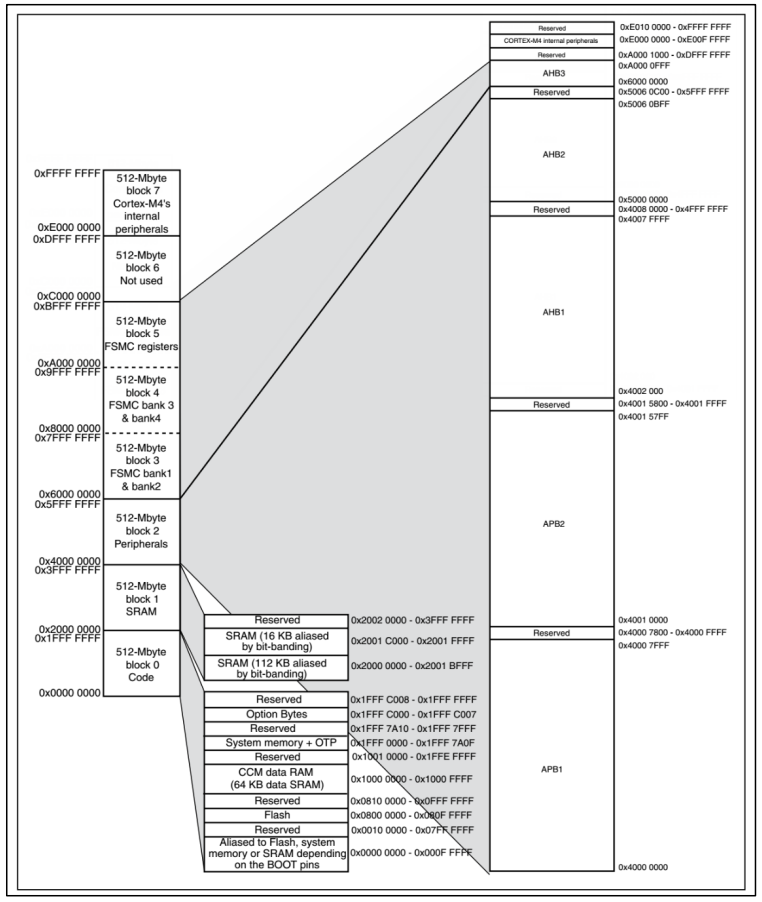

在图 6-4 中,连接被控总线的是 FLASH, RAM 和片上外设,这些功能部件共同排列在一个 4GB 的地址空间内。我们在编程的时候,操作的也正是这些功能部件。

存储器本身不具有地址信息,它的地址是由芯片厂商或用户分配,给存储器分配地址的过程就称为存储器映射,具体见图 6-5。 如果给存储器再分配一个地址就叫存储器重映射。

图 6-5 STM32F407 存储器映射

5.1、 存储器区域功能划分

在这 4GB 的地址空间中, ARM 已经粗线条的平均分成了 8 个块,每块 512MB,每个块也都规定了用途,具体分类见表格 6-1。每个块的大小都有 512MB,显然这是非常大的,芯片厂商在每个块的范围内设计各具特色的外设时并不一定都用得完,都是只用了其中的一部分而已。

表格 6-1 存储器功能分类

在这 8 个 Block 里面,有 3 个块非常重要,也是我们最关心的三个块。 Boock0 用来设计成内部 FLASH, Block1 用来设计成内部 RAM, Block2 用来设计成片上的外设,下面我们简单的介绍下这三个 Block 里面的具体区域的功能划分。

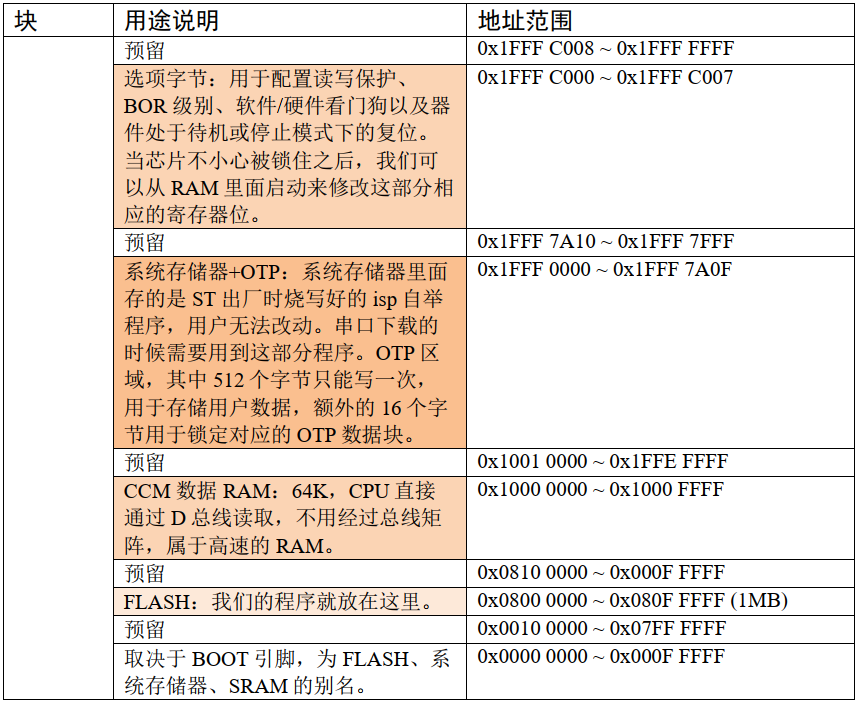

(1)存储器 Block0 内部区域功能划分

Block0 主要用于设计片内的 FLASH, F407 系列片内部 FLASH 最大是 1MB,我们使用的 STM32F407ZGT6 的 FLASH 就是 1MB。要在芯片内部集成更大的 FLASH 或者SRAM 都意味着芯片成本的增加,往往片内集成的 FLASH 都不会太大, ST 能在追求性价比的同时做到 1MB 以上,实乃良心之举。 Block0 内部区域的功能划分具体见表格 6-2。

表格 6-2 存储器 Block0 内部区域功能划分

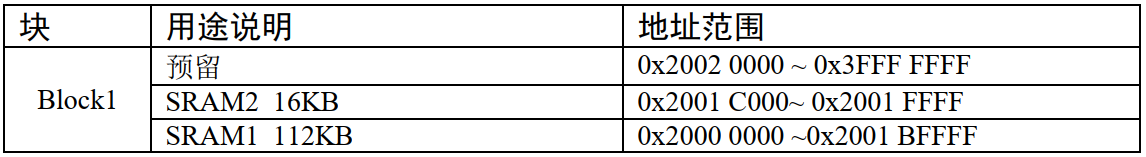

(2)储存器 Block1 内部区域功能划分

Block1 用于设计片内的 SRAM。 F407 内部 SRAM 的大小为 128KB,其中 SRAM1 为112KB, SRAM2 为 16KB。 Block1 内部区域的功能划分具体见表格 6-3。

表格 6-3 存储器 Block1 内部区域功能划分

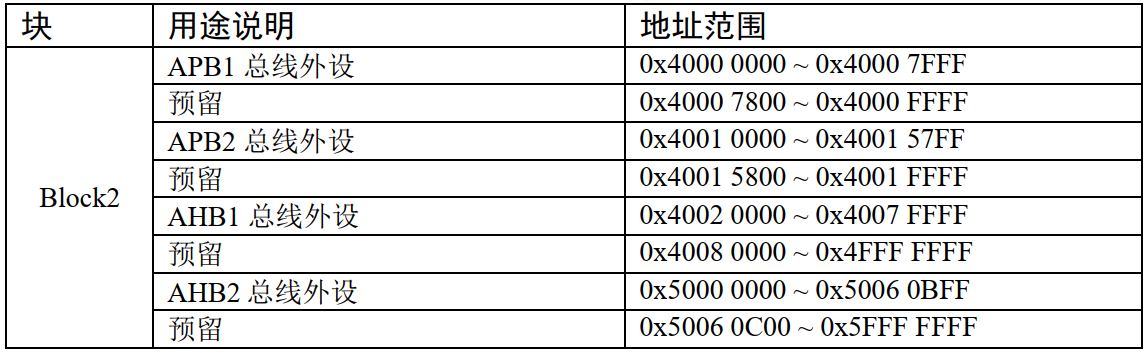

(3)储存器 Block2 内部区域功能划分

Block2 用于设计片内的外设,根据外设的总线速度不同, Block 被分成了 APB 和 AHB两部分,其中 APB 又被分为 APB1 和 APB2, AHB 分为 AHB1 和 AHB2,具体见表格 6-4。还有一个 AHB3 包含了 Block3/4/5, AHB3 包含的 3 个 Block 用于扩展外部存储器,如SRAM, NORFLASH 和 NANDFLASH 等。

表格 6-4 存储器 Block2 内部区域功能划分

6、寄存器映射

我们知道,存储器本身没有地址,给存储器分配地址的过程叫存储器映射,那什么叫寄存器映射?寄存器到底是什么?

在存储器 Block2 这块区域,设计的是片上外设,它们以四个字节为一个单元,共32bit,每一个单元对应不同的功能,当我们控制这些单元时就可以驱动外设工作。我们可以找到每个单元的起始地址,然后通过 C 语言指针的操作方式来访问这些单元,如果每次都是通过这种地址的方式来访问,不仅不好记忆还容易出错,这时我们可以根据每个单元功能的不同,以功能为名给这个内存单元取一个别名,这个别名就是我们经常说的寄存器,这个给已经分配好地址的有特定功能的内存单元取别名的过程就叫寄存器映射。

比如,我们找到 GPIOF 端口的输出数据寄存器 ODR 的地址是 0x4002 1414(至于这个地址如何找到可以先跳过,后面我们会有详细的讲解), ODR 寄存器是 32bit,低 16bit 有效,对应着 16 个外部 IO,写 0/1 对应的的 IO 则输出低/高电平。现在我们通过 C 语言指针的操作方式,让 GPIOF 的 16 个 IO 都输出高电平,具体见代码 6-1。

代码 6-1 通过绝对地址访问内存单元

// GPIOF 端口全部输出 高电平 *(unsigned int*)(0x4002 1414) = 0xFFFF;

0x4002 1414 在我们看来是 GPIOF 端口数据输出寄存器 ODR 的地址,但是在编译器看来,这只是一个普通的变量,是一个立即数,要想让编译器也认为是指针,我们得进行强制类型转换,把它转换成指针,即(unsigned int *)0x4002 1414,然后再对这个指针进行 *操作。

刚刚我们说了,通过绝对地址访问内存单元不好记忆且容易出错,我们可以通过寄存器的方式来操作,具体见代码 6-2。

代码 6-2 通过寄存器别名方式访问内存单元

// GPIOF 端口全部输出 高电平 #define GPIOF_BASE 0x40021400 #define GPIOF_ODR (unsigned int*)(GPIOF_BASE+0x14) *GPIOF_ODR = 0xFF;

为了方便操作,我们干脆把指针操作“*”也定义到寄存器别名里面,具体见代码 6-3。

代码 6-3 通过寄存器别名访问内存单元

// GPIOF 端口全部输出 高电平 #define GPIOF_BASE 0x40021400 #define GPIOF_ODR *(unsigned int*)(GPIOF_BASE+0x14) GPIOF_ODR = 0xFF;

浙公网安备 33010602011771号

浙公网安备 33010602011771号