- 前言

- 专有名词中英文对照表

- Chapter 6: Platform Management Unit 平台测量单元

- 6.3 Operation 操作

- 6.3.1 Power Down 断电

- 6.3.2 Power Up 上电

- 6.3.3 APU Power Down APU断电

- 6.3.4 APU Core Power Up APU核心上电

- 6.3.4 PMU Operation After a Wake-up

- 6.3.5 Wake-up Through MIO 使用MIO唤醒

- 6.3.6 Wake-up on USB 使用USB唤醒

- 6.3.7 Wake-up on Ethernet 使用以太网唤醒

- 6.3.8 Wake on Real-time Clock 使用实时时钟唤醒

- 6.3.8 Wake through DAP 使用DAP唤醒

- 6.3.9 Direct Wake by the APU or Cortex-R5F

- 6.3.10 Wake through GIC Proxy 使用GIC代理唤醒

- 6.3.10 Deep-sleep Mode

- 6.3.11 Deep-sleep Mode Programming Model/Example

- 6.3.12 Isolation Request 隔离请求

- 6.3.13 Reset Services 复位服务

- 6.3.14 Programming Model 编程模型

- 本章总结

- 6.3 Operation 操作

前言

上一篇笔记讲了ug1085MPSOC技术参考手册的第六章PMU的上半,也就是有关PMU内部结构的内容,这次我们来讲第六章的下半,PMU的相关操作,主要是上电断电和唤醒的PMU相关操作,由于我没有实际进行操作过,在描述的时候可能会大量的贴原文档的翻译。同样这里再次事先声明,由于我对PMU的理解还不够,所以我用了AI工具来理解这些内容,所以解释可能有问题也欢迎指出。。

专有名词中英文对照表

| 英文 | 简称 | 中文翻译 |

|---|---|---|

| platform measurement unit | (PMU) | 平台管理单元 |

| software test library | (STL) | 软件测试库 |

| configuration and security unit | (CSU) | 配置与安全单元 |

| Battery-backed RAM | (BBRAM) | 电池后备RAM |

| Real-time clock | (RTC) | 实时时钟 |

| IO peripherals | (IOP) | IO外设 |

| Inter-Processor Interrupt | (IPI) | 处理器间中断 |

| memory built-in self test | (MBIST) | 内存内置自测试 |

| Advanced Interrupt Bus | (AIB) | 先进中断总线 |

| Triple Modular Redundancy | (TRM) | 三模冗余 |

| power-on reset | (POR) | 上电复位 |

| system reset | (SRST) | 系统复位 |

| built-in self-repair | (BISR) | 内建自修复 |

| programmable interval timers | (PITs) | 间隔可编程定时器 |

Chapter 6: Platform Management Unit 平台测量单元

6.3 Operation 操作

这一节主要是在描述PMU三种操作的流程,即PMU控制PS端各个模块的上电(Power Up),断电(Power Down)以及唤醒(Wake-up),还有一些和这些操作相关的特性。在第六章的上半提到过,PMU的核心功能之一就是控制PS各模块的电源,这一节就是要讲PMU是如何控制各模块电源的(这里其实主要介绍了APU和RPU的电源管理)。

在讲子章节之前需要补一下其他的特性,在MPSOC中,被PMU进行电源管理的模块主要可以分为两类,电源主模块和电源从模块,其中电源主模块可以对包括自身以及其他的电源从模块进行上电断电,例如APU和RPU,而电源从模块只能被电源主模块进行上断电管理,例如USB,PL,GPU以及内存。这章节没有介绍PMU管理其他模块的电源估计是因为其只负责管理电源主模块,电源从模块似乎并不归PMU管(但是PMU又可以管理LPD域)。

这里还要解释下用户的软件与PMU进行交换的主要过程,用户编写的软件(这里应该指的是在APU,RPU中执行的软件,而不是PMU RAM中的软件)通过与PMU_GLOBAL寄存器进行交互,也就是置位操作(例如置某个APU的断电触发寄存器为1),使得PMU处理器产生对应中断,PMU处理器更加对应中断并依据PMU ROM中的优先级进行中断服务程序的执行,执行完后清除状态标志位。如果执行失败,则PMU_GLOBAL.ERROR_STATUS寄存器会被断言并产生错误事件,当然这些错误事件又回诱发PMU进行错误事件的处理操作(详见第六章(上)PMU Error Handling and Propagation Logic的内容)。总而言之,用户程序和PMU的操作大部分是通过PMU_GLOBAL寄存器来进行的,PMU的处理器也同样依赖PMU_GLOBAL寄存器进行中断控制和操作。

6.3.1 Power Down 断电

这小节简要介绍了外部模块如何通过PMU来断电对应模块的,具体做法是向REQ_PWRDWN_TRIG寄存器的对应位写入1并且对应的REQ_PWRDWN_INT_MASK寄存器也为1,也就是不进行屏蔽,此时PMU处理器会被中断然后检查对应的中断寄存器以确定是否有中断(二次确认的原因应该是寄存器中断是对应整个寄存器的变化,需要再次检查以确定到底是哪个位),然后执行对应的中断服务程序(ISR)。

6.3.2 Power Up 上电

这小节类似于上一小节,也是讲外部通过PMU实施对某个模块上电的过程,也还是通过对REQ_PWRUP_TRIG对应位写1并且对应的REQ_PWRUP_INT_MASK寄存器也为1是进行中断触发,后面的内容不赘述了。

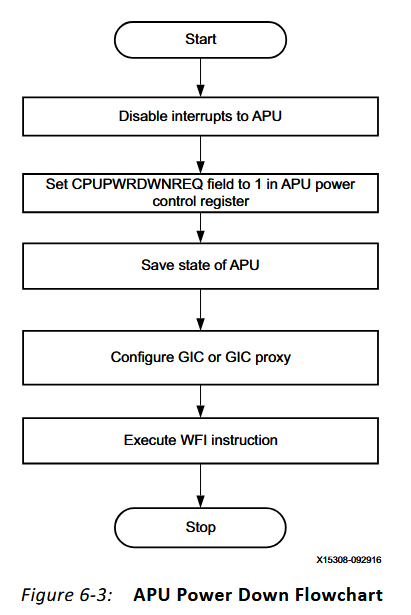

6.3.3 APU Power Down APU断电

这小节讲的是APU断电的方法以及具体流程。APU断电主要有两者种方法,直接断电和请求式断电。

6.3.3.1 Direct Power Down

直接断电和我们上面说到的写寄存器式断电的方式不太一样,我这里贴下源文档并注释一下以表明这个过程:

作为断电准备,APU的准备过程必须有以下步骤:

- 禁用核心中断。

- 通过将1写入与该pu核心相对应的字段,在APU中的PWRCTL寄存器的CPUPWRDWNREQ字段中记录关闭中央处理器的意图。

- 保存APU核心的状态

- 为唤醒源配置GIC或GIC代理(如果APU断电后准备FPD断电则配置GIC代理)。

- 执行等待中断(WFI)指令

其实直接断电的核心原理就是写入CPUPWRDWNREQ为1以表示处理器准备断电了,此时在让处理器进入WFI的低功耗模式,则会直接让处理器触发发送到PMU GPI2的断电请求,从而实现处理器的断电,这里还有一张流程图,如下:

6.3.3.2 Requested Power Down

请求断电模式就没什么好说的了,就如前面在6.3.1 Power Down里面说的,向对应的断电触发寄存器写1 就能够正常实现请求式断电。

6.3.4 APU Core Power Up APU核心上电

APU核心的上电主要由两类器件控制,一类是其他CPU向PMU发送的上电请求,一类是与该核心相关联的外设发出的中断,具体的上电步骤如下:

- 为了为APU核心供电,请求设备必须设置REQ_PWRUP_TRIG全局寄存器中的特定位。

- 如果GIC的直接加电或唤醒已经对一个APU核心实施,则PMU将遵循PMU ROM代码指定的步骤并为APU加电。直接加电是指由发往APU核心的中断触发的加电事件,而不是软件通过写入PMU_GLOBAL模块中的请求寄存器来触发事件

- 如果在通电完成后发生直接唤醒或GIC唤醒,则也会自动释放对APU核心的复位。

- 如果加电请求是由另一个处理器发出的,则同一个处理器必须明确请求通过PMU重置请求寄存器释放对APU核心的重置。

- 检查是否将PMU_PWRUP_STATUS全局寄存器中的适当位位置设置为0,以指示上电请求由PMU提供服务

总结来说,对APU核心的唤醒也遵循最基础的向全局寄存器写入的操作,而且同样有和APU直接断电类似的直接上电操作,只是对于外设和其他寄存器而言,在上电后处理器核心的复位的释放不同,对于外设的上电请求会直接释放核心复位,而对于其他CPU的上电请求则会根据其他CPU的设置而释放复位。

6.3.4 PMU Operation After a Wake-up

这节将PMU的wake-up操作,也就是将处理器从低功耗或者休眠模式中唤醒的操作,这节有点复杂,我自己也没有完全看懂,这里就说一下AI总结的内容。PMU总共有三种唤醒处理器的方式:

-

Fixed:直接唤醒处理器,例如处于断电中的R5F处理器在接受外设或者定时器中断后进行上电的请求,具体主要有两步,第一,中断被路由到PMU以触发唤醒处理器的请求,第二,当处理器唤醒后,释放其复位使其处理被挂起的中断。

-

On-demand:在处理器进行休眠状态前,规定在处理器被唤醒后需要同时打开的模块,具体步骤如下:

- 软件写REQ_PWRUP_TRIG寄存器,请求唤醒后开启某些电源域;同时在REQ_PWRUP_INT_DIS中屏蔽这些请求的中断。这样就能实现即时这些电源域已被要求上电,但在处理器被唤醒前这些电源域都不会被真正上电。

- 软件发起正常睡眠请求。

- 系统被外部事件唤醒,PMU检查REQ_PWRUP_STATUS,发现有被屏蔽但未执行的上电请求,然后一并执行上电。

- 如果还需要释放某些模块的复位,软件在睡眠前也需写REQ_SWRST_TRIG并且屏蔽其中断。

- PMU 完成上电后,释放对应模块的复位,使其开始工作。

6.3.5 Wake-up Through MIO 使用MIO唤醒

介绍PMU结构时提到过,PMU可以使用6根MIO线作为输入,实现外部唤醒(GPI1[15:10]对应MIO[31:26]),这样就可以使用MIO基于三种方式实现唤醒,分别是外部事件,以太网PHY和CAN PHY

根据机制的不同,上述接口引发的任何中断都会被发送给PMU,以唤醒将该接口设置为其唤醒源的设备。

这里还讲了好几种通过特殊方式唤醒设备的方式,内容比较多而且偏介绍性,我就只简单翻译一下了。

6.3.6 Wake-up on USB 使用USB唤醒

USB规范定义了链路层挂起模式,其中USB主机和设备都进入无活动阶段以节省电力。将USB主机置于挂起模式的决定仅由软件决定。一旦主机进入挂起模式,所有连接到该主机的设备都需要在3ms内进入挂起模式。USB设备无法自行进入挂起模式;但是,当支持链路电源管理(LPM)扩展时,USB设备可以请求USB主机进入挂起模式。当USB主机进入挂起模式时,所有USB设备都会跟随。

USB主机可以通过计时器等中断或通过具有特殊USB信号均衡的设备发出的远程唤醒请求退出暂停模式(原文signal leveling我觉得是不是指的是信号电平)。USB设备也可以通过来自主机的中断或远程唤醒信号或额外通过主机重置信号来唤醒。

当USB处于挂起模式时,USB ULPI链路协议为实体物理层在D+/D-信号被定向到USB链路期间掉电提供了标准方法。在这种情况下,始终处于打开状态的USB IP的子部分检测唤醒信号并向PMU生成唤醒中断,以继续为USB块和负责其设备驱动程序的处理器通电。

6.3.7 Wake-up on Ethernet 使用以太网唤醒

以太网唤醒可以通过两种方式执行。

PHY唤醒:此唤醒过程可以使用从MIO引脚路由的GPI输入信号来实现。

MAC唤醒:此唤醒过程广泛称为LAN唤醒。此过程是使用称为magic packet的特殊网络消息实现的。magic packet是一个广播帧,其有效负载内的任何位置包含全部255个字节中的6个字节(FF FF FF FF FF FF FF FF FF),后面是目标计算机48位MAC地址的十六次重复,总共102个字节。检测到magic packet将对正在运行设备驱动程序的处理器产生中断,从而导致处理器直接唤醒。

6.3.8 Wake on Real-time Clock 使用实时时钟唤醒

此功能允许系统使用内部实时时钟(RTC)在预定时间唤醒。配置RTC以在到达特定时间和日期时生成中断。(这个实时是指真实时间)

6.3.8 Wake through DAP 使用DAP唤醒

此功能通过调试器唤醒处于睡眠模式的系统。调试器可以通过DAP请求两种可能的直接加电场景。一种选项可以唤醒FP域,其中包括MPSoC调试。另一个唤醒选项启动双Cortex-R5F子系统的通电。

6.3.9 Direct Wake by the APU or Cortex-R5F

当任何应用程序处理器或实时处理器断电时,如果外围设备试图中断(interrupt)断电的处理器,则该中断将被路由到PMU以触发该特定处理器的通电。

6.3.10 Wake through GIC Proxy 使用GIC代理唤醒

如果应用程序处理器的断电与整个FPD的断电同时发生,则与该处理器关联的LPD设备仍然可以通过首先触发FPD的通电来触发对该处理器的直接唤醒。这是通过在LPD中设置一个GIC代理块来实现的,该块可以选择路由到PMU的外围中断作为直接唤醒以外的中断(也就是上面的APU上电的关联外设上电请求的方法)。收到来自GIC代理块的中断后:

- PMU为FPD供电。

- 释放FPD和APU的复位。

- 取消屏蔽触发该应用程序处理器的直接唤醒的中断。

直接唤醒将生效,从而导致应用处理器上电。

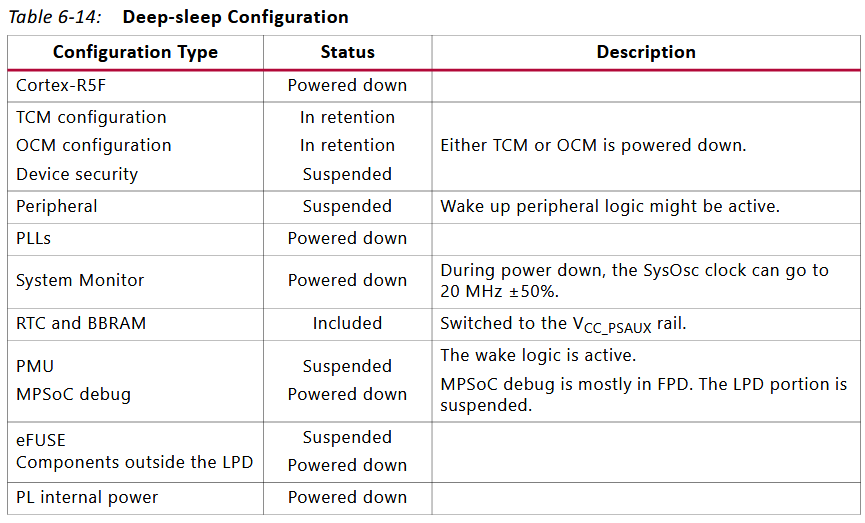

6.3.10 Deep-sleep Mode

在讲PMU结构部分时讲到过PMU管理系统的电源模式,有低功耗和全功耗模式两种,这里由额外提到了深度睡眠模式。深度睡眠模式相比于低功耗模式还有更加节省功耗,他直接关闭了几乎所有的外设,只保留几个设备以供系统唤醒使用。这个模式下,系统只能由PMU的GPI(应该就是GPI的MIO)和RTC唤醒。这个模式相比直接把系统关了有一个显著的好处,其不需要再进行boot process并且系统安全相关的状态被保留了,从而显著的减少了系统的启动时间。在这个模式下只保留了维持boot状态和安全状态的最低功耗,连PMU都进入睡眠或者挂起了。这里有一张介绍系统各部件在深度睡眠模式下的状态:

这里可以看到除了TCM,OCM被保留(但是也被断电我不太理解),RTC和BBRAM(用来存储安全信息)正常工作外别的部件都被断电或者挂起了,其电源域也被切到了VCC_PSAUX这条电源轨上。

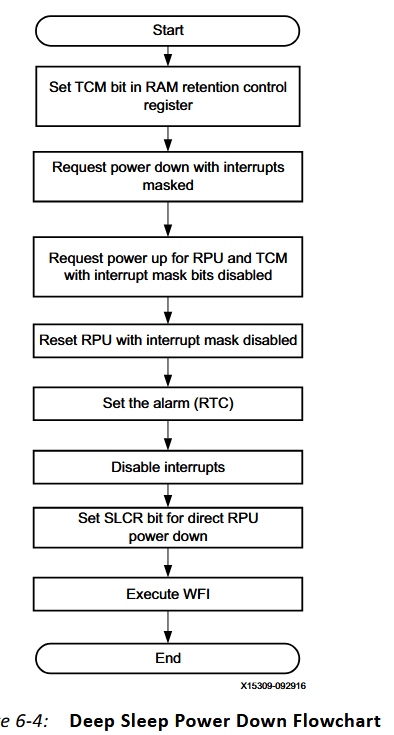

6.3.11 Deep-sleep Mode Programming Model/Example

这小节要讲系统具体讲深度睡眠模式的模型或例程,内容比较繁杂,在进入深度睡眠模式前需要进行一些的配置,例如R5F要进入锁步模式,TCM和RTC要进行配置(这里我也不知道对不对,原文比较奇怪),而进行睡眠模式后又需要将FPD,RPU,USB,PLLs,OCM和系统监视器断电,TCM保留,RTC被设置且正常工作。下面有关例程的内容我就不解释了,原文翻译如下:

6.3.11.1 Power Down Procedure

断电由Cortex-R5F启动。当TCM处于保留状态时,Cortex-R5F需要执行以下操作。

- 设置RAM_RET_CATRL寄存器中的TCM位。

- 在设置REQ_PWRDWN_TRIG寄存器的TCM位的同时设置REQ_PWRDWN_INT_MASK寄存器TCM位的中断屏蔽

- 设置REQ_PWRUP_TRIG寄存器中的RPU和TCM位,同时禁用这些字段的中断屏蔽位。

- 设置REQ_SWRST_TRIG中的RPU位,同时禁用其中断屏蔽位。

- 设置闹钟。

- 禁用中断。

- 设置SLCR位以请求直接RPU断电并执行WFI指令。

这些操作会中断PMU,从而关闭RPU。

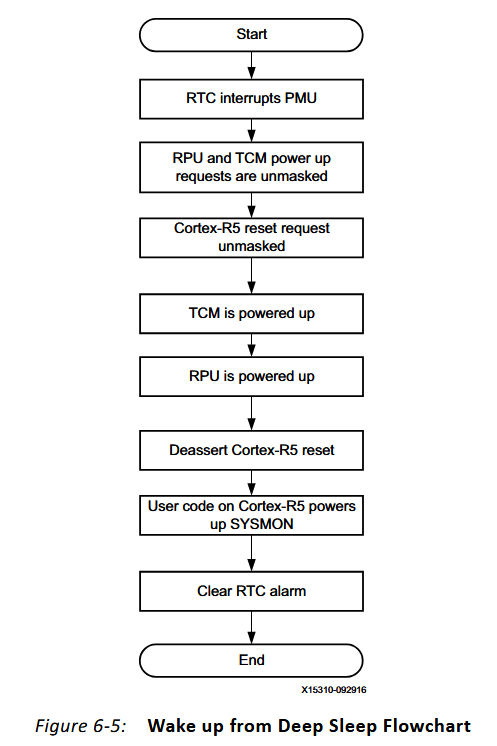

6.3.11.2 Wake Procedure

一旦RTC闹钟对PMU产生中断,RTC唤醒的处理程序就会检测是否为此目的加载了固件。如果没有,处理程序会检查on-demand程序是否在PMU中队列。在断电之前,Cortex-R5F请求RPU和TCM通电,同时屏蔽通电请求的中断。它请求释放Cortex-R5F复位,同时再次屏蔽该请求的中断。从RTC醒来后,PMU继续启动RPU并发出Cortex-R5F复位。

.1. RPU和TCM加电请求作为TTC唤醒的一部分被解除屏蔽。

.2. Cortex-R5F复位请求作为TTC唤醒的一部分被解除屏蔽。

.3. 由于TCM加电中断,TCM首先加电。

.4. 由于RPU加电中断,RPU加电。

.5. 由于Cortex-R5F复位请求中断,Cortex-R5F的复位释放。

.6. Cortex-R5F上的代码会将系统监视器从断电状态中释放。

.7. Cortex-R5F上的代码会清除RTC警报。由于RTC具有中断状态寄存器,因此将警报位设置为1会清除中断。

6.3.12 Isolation Request 隔离请求

隔离指的是在某个电源域断电前,将该电源域与其他域连接的信号强制设置为某个特定值的操作。这个操作的目的是为了防止断电过程中产生的错误电平影响其他模块的电路。这种错误是由于Crowbar Current(直通电流/穿通电流)产生的。具体的什么是直通电流太偏模电了我也不太懂。具体操作来看原文:

PMU使能各个电源域的隔离。这可以通过在REQ_ISO_TRIG全局寄存器中设置适当的位来完成。低功耗、全功率和PL域之间由三个bit位进行隔离控制。有不同的隔离组合可用。通过写入RST_ISO_TRIG寄存器和REQ_ISO_INT_MASK寄存器的bit0,全功率域可以与低功率域和PL域隔离;通过写入这些寄存器的bit1,PS与PL隔离;通过写入bit2,PS和PL被隔离,不包括PCAP接口;最后,要锁定全功率域上的隔离,请写入bit4。

6.3.13 Reset Services 复位服务

这小节主要讲了REQ_SWRST_TRIG寄存器不同位对应的复位服务,前提是这些其这些服务对应的REQ_SWRST_INT_MASK没有被写0,也就是被屏蔽。表太长了这里就不展示了,具体看第139页的图6-15。

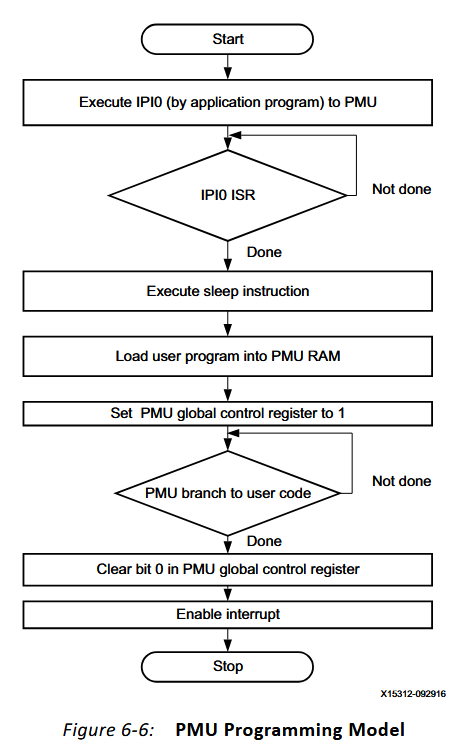

6.3.14 Programming Model 编程模型

我们之前提到过,PMU可以通过用户编程,在PMU RAM中执行程序来实现PMU的功能扩展,这些程序也被称为PMU Firmware。这节的内容就是指导用户如何进行具体的编程,我这里就就只翻译一下了:

除了AMD提供的固件之外,PMU还可以执行实施高级系统监控和系统关键功能的用户程序。通常,PMU代码加载可以在引导时通过CSU ROM代码或通过第一阶段引导加载程序(FSBL)进行。在此期间,PMU要么处于已加载的维护模式,要么处于睡眠模式。为了确保PMU处于睡眠模式,IPI0用于中断PMU。为了响应IPI0中断,该IPI的中断服务例程禁用中断并执行睡眠指令,随后转移到加载到RAM中的用户代码。这保证了处理器保持在睡眠模式,并且不会被中断执行任何服务,直到另一个主机通过使用PMU全局控制寄存器中的唤醒位显式唤醒它。主处理器将用户程序复制到PMU RAM中后,利用PMU全局控制寄存器中的处理器唤醒功能来指示PMU处理器执行新加载的维护代码。

此处列出了加载用户级程序并开始执行其所需的步骤。

- 另一个处理器上的应用程序(APU或RPU)对PMU执行IPI0。

- IPI0中断服务程序。

- 禁用所有中断。

- 执行睡眠指令。睡眠指令之后的指令必须是RAM中用户代码地址的分支。

- 应用程序将PMU用户程序加载到RAM中。

- 应用程序将1写入PMU全局控制寄存器的位[0]以唤醒处理器。

- PMU在睡眠指令之后开始执行指令,并返回代码中的main()函数。

- PMU分支到用户代码。

- 用户代码将清除PMU全局控制寄存器中的位[0]并使能中断。

上级程序可以检查PMU全局控制寄存器以确定硬件加载和执行的状态。

本章总结

PMU的内容实在是太多太多了,50页的内容就算是精简的讲也非常多,当然内容多收获也多。我们下篇随笔再见。********

浙公网安备 33010602011771号

浙公网安备 33010602011771号