- 前言

- 专有名词中英文对照表

- Chapter 6: Platform Management Unit 平台测量单元

- 6.1 Introduction 介绍

- 6.2 Functional Description 功能性描述

- 6.2.1 PMU Processor PMU处理器

- 6.2.2 PMU Processor Interfaces PMU处理器接口

- 6.2.3 PMU Clocking PMU时钟

- 6.2.4 PMU Reset PMU复位

- 6.2.5 PMU RAM

- 6.2.6 PMU ROM

- 6.2.6 MBIST Functionality 内存内建自测功能

- 6.2.7 Scan Clear Functionality 扫描清除功能

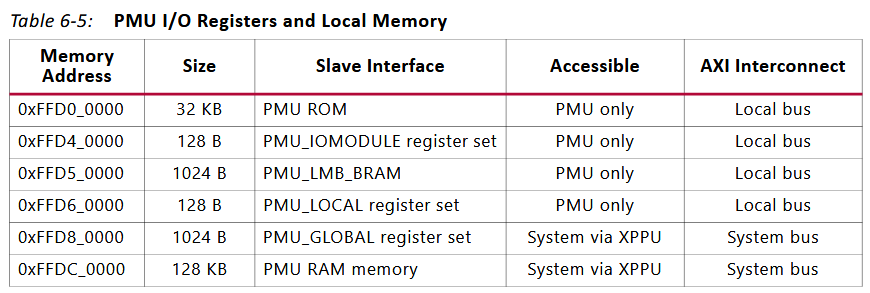

- 6.2.8 PMU I/O Registers PMUI/O寄存器

- 6.2.8 PMU Global Registers PMU全局寄存器

- 6.2.8 PMU GPIs and GPOs

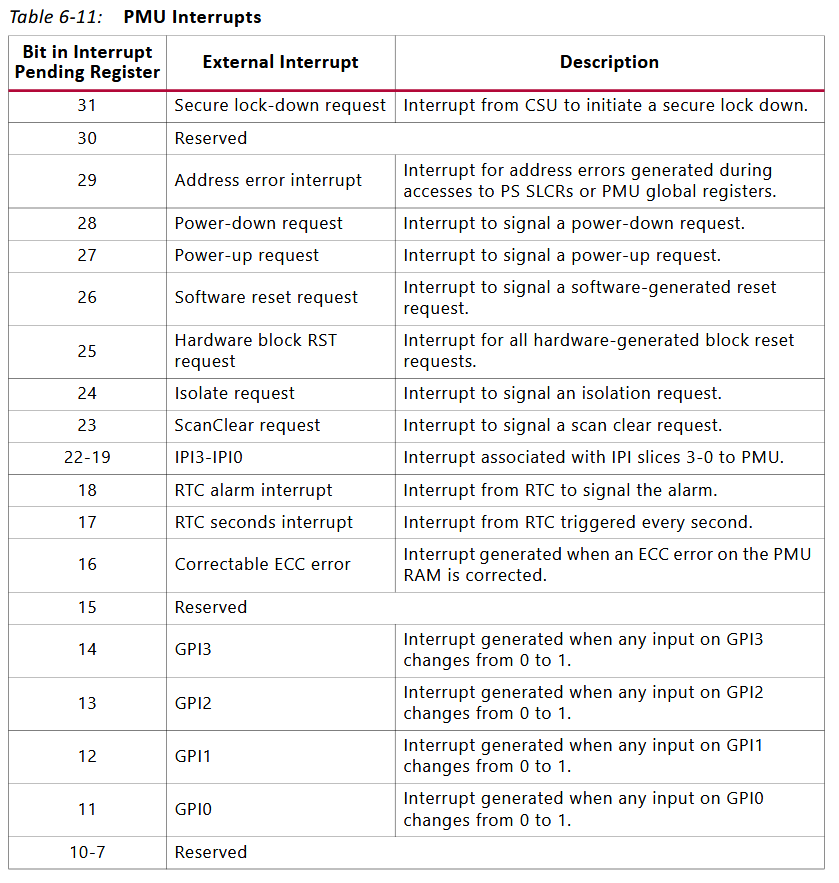

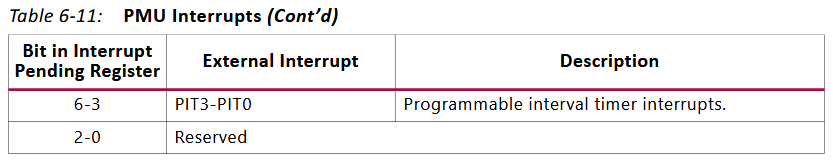

- 6.2.9 PMU Interrupts

- 6.2.10 PMU Error Handling and Propagation Logic PMU错误处理与传播逻辑

- 小节

前言

上一章讲了ug1085MPSOC技术参考手册的第四章,讲了有关MPSOC RPU的相关内容,这次我们来讲第六章,可以说是MPSOC中最复杂核心器件的PMU(第五章GPU我就跳过了主要我还没打算用),这部分内容由于非常多而且非常复杂,在描述的时候我可能会大量的贴原文档的翻译。同样这里再次事先声明,由于我对PMU的理解还不够,所以我用了AI工具来理解这些内容,所以解释可能有问题也欢迎指出。。

专有名词中英文对照表

| 英文 | 简称 | 中文翻译 |

|---|---|---|

| platform measurement unit | (PMU) | 平台管理单元 |

| software test library | (STL) | 软件测试库 |

| configuration and security unit | (CSU) | 配置与安全单元 |

| Battery-backed RAM | (BBRAM) | 电池后备RAM |

| Real-time clock | (RTC) | 实时时钟 |

| IO peripherals | (IOP) | IO外设 |

| Inter-Processor Interrupt | (IPI) | 处理器间中断 |

| memory built-in self test | (MBIST) | 内存内置自测试 |

| Advanced Interrupt Bus | (AIB) | 先进中断总线 |

| Triple Modular Redundancy | (TRM) | 三模冗余 |

| power-on reset | (POR) | 上电复位 |

| system reset | (SRST) | 系统复位 |

| built-in self-repair | (BISR) | 内建自修复 |

| programmable interval timers | (PITs) | 间隔可编程定时器 |

Chapter 6: Platform Management Unit 平台测量单元

6.1 Introduction 介绍

PMU即platform measurement unit平台测量单元(我之前一直以为是平台管理单元,不够我感觉都不足以描述其功能)是MPSOC系统中一个非常重要的部件,我们之前讲的APU,RPU这些部件在系统中负责一些应用层面的任务,例如数值运算,内存控制,外设控制,而PMU单元则不太一样,虽然PMU的本质仍然是类似于APU,RPU一样的处理器模块,但是其负责MPSOC系统中绝大部分的底层管理工作,如BOOT,电源管理,复位管理,系统测试,系统错误管理等等。这一章节主要就要介绍PMU的主要构成以及功能,我这里翻译如下:

PMU执行以下的任务。

- 根据启动优先级初始化系统

- 电源管理

- 软件测试库(STL)的执行(可选)

- 系统错误处理

这里还提到CSU模块会监测系统温度传感器,不过后续讲到CSU时再详说。

6.1.1 Power Modes电源模式

由于PMU涉及电源管理的内容,这一小节主要就介绍了一下MPSOC的电源模式与电源域。电池模式主要有电池供电模式,低功耗工作模式以及全功耗工作模式,下面就稍微介绍一下,因为源文档也只是大致提了一下。

6.1.1.1 Battery Powered Mode

电池供电模式就是当主供电断开时,为了保留一些安全性和实时时钟的设置而对其进行供电的模式,在这个模式下只有两个模块会被电池电源域供电:

- Battery-backed RAM (BBRAM)电池后备RAM,用来存储一些安全配置的关键信息

- RTC以及其晶振,这个应该是用来做根据实际时间唤醒或者关机任务的

6.1.1.2 Low-Power Operation Mode

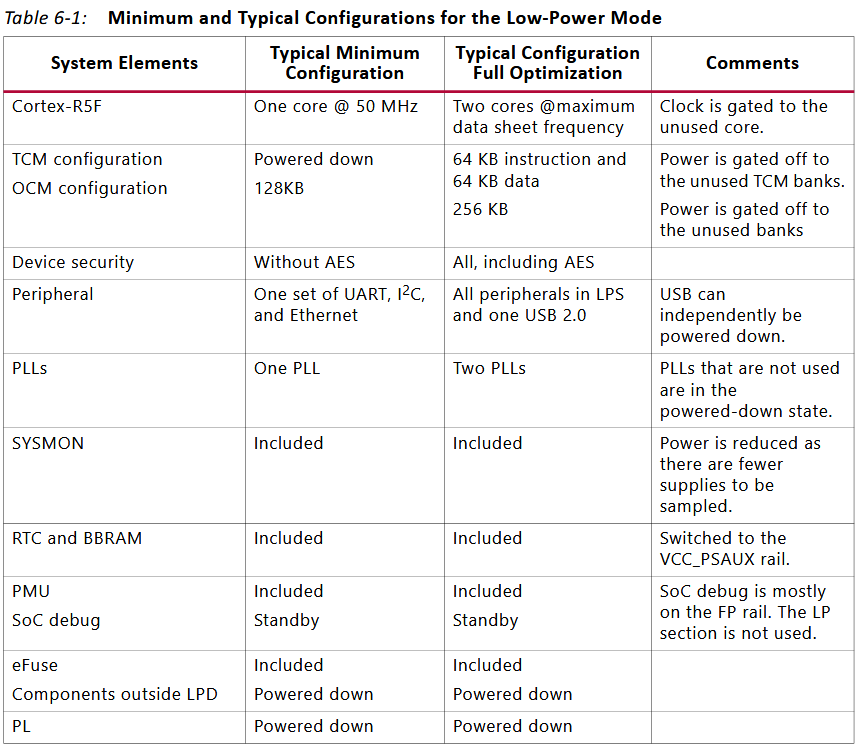

低功耗模式下除了SATA和DP口外的外设都会工作,(这里的原文说的是在低功耗电源轨上的PS模块都会工作,包括PMU,RPU,CSU,IOP)同时列出了一个表格来展示在低功耗模式下其可配置的最少和最多的模块:

注意低功耗模式下APU和PL都是不能使用的。

6.1.1.3 Full-Power Operation Mode

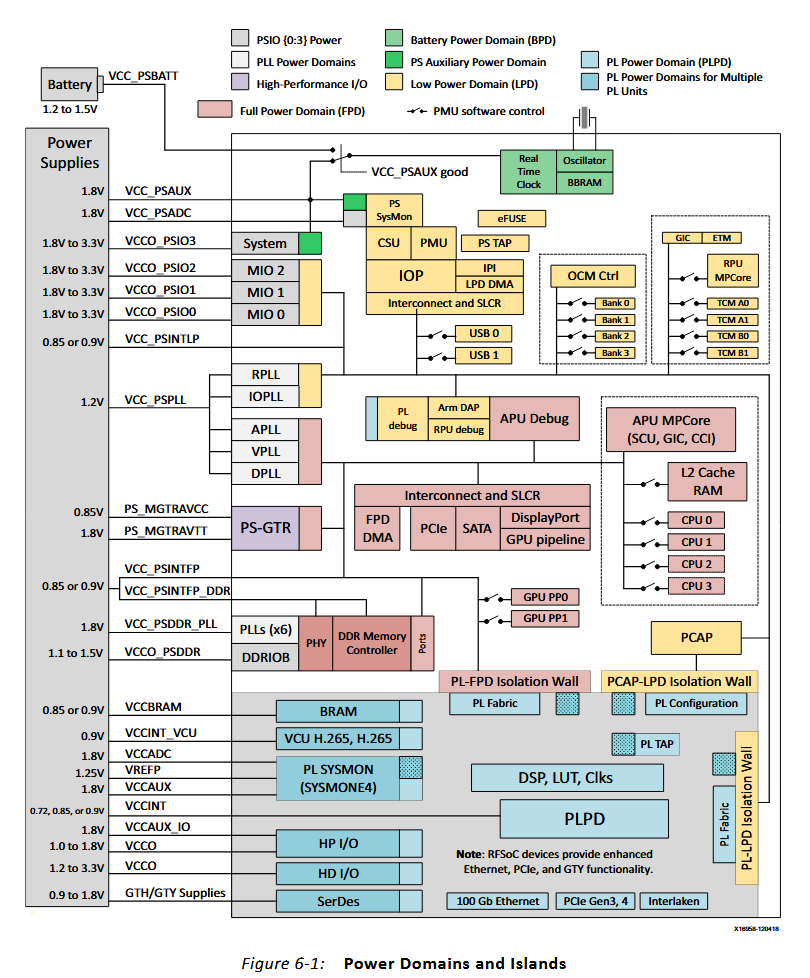

全功耗模式就是所有电源域都供电的电源模式,这节内容主要是一张电源域的总览图:

图中比较明显的就是黄红蓝的三片区域对应着LPD,FPD和PLPD三个电源域,最上方还有一小部分绿色代表电池电源域,我觉得还有一个比较重要的地方是VCC_PSINTLP,VCC_PSINTFP以及VCCINT这三根电源线,分别连接了LPD,FPD和PLPD的主要部件上,其余很多的电源线是专门给一些特殊部件供电的,这三根则是负责每个电源域的核心供电。

6.1.2 PMU System-level View PMU系统级总览

这一节主要是给下一节介绍PMU的具体功能做铺垫,大体介绍了一下PMU中的部件,我这里以贴翻译为主:

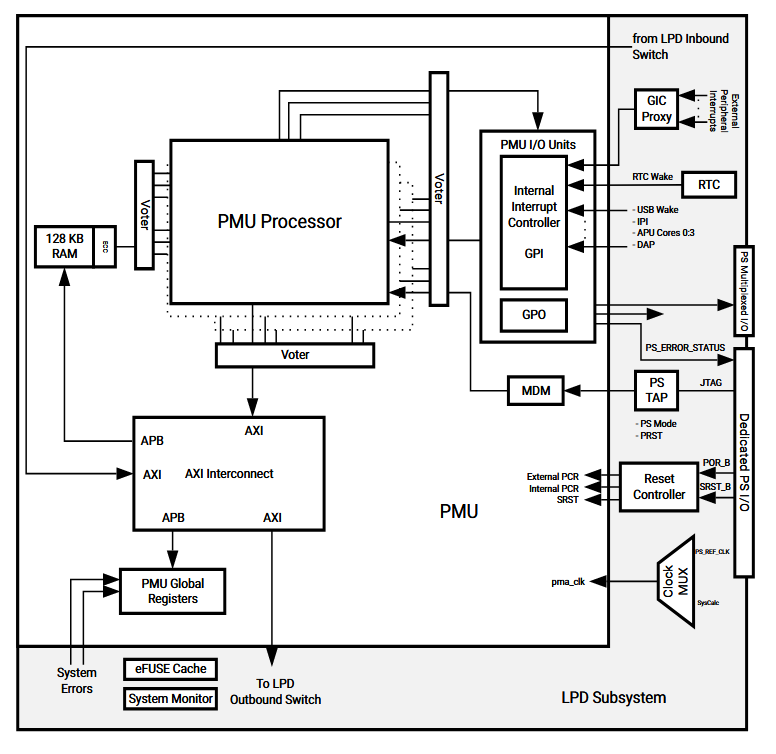

PMU块位于低功耗域中。图6-2显示了PMU的方框图。它包括以下子组件:

- 专用的、故障容忍的三冗余处理器。

- 用于保存PMU代码的PMU ROM,其中包括PMU启动序列、处理上电,断电请求或中断的例程。

- 128KB用于存储代码和数据ECC RAM。

- 仅由PMU访问的PMU本地寄存器。

- PMU全局寄存器,可由PMU处理器以及系统内的其他总线主设备访问。其中包括所有电源、隔离和重置请求寄存器,还包括错误捕获寄存器和系统电源状态寄存器。

- 32位AXI从机接口,允许PMU外部的主机访问PMU RAM和全局寄存器。

- PMU中断控制器管理PMU的23个中断。其中四个中断来自处理器间互连(IPI)。

- GPI和GPO寄存器,用于PMU与PMU、MIO、PL和PS内的其他资源进行信号交流。

- 六个输出和六个输入。(对于MIO)

- 从PMU到PL的32个GPO输出和从PL到PMU的32个GPI输入。

- 47个输入PMU的系统错误标识线。

- CSU错误代码。

- 32个存储器内建自测试(MBIST)状态信号和32个MBIST完成信号。

- 三个直接复位控制信号。

- 四个AIB状态信号和四个AIB控制信号。

- 11个逻辑清除状态信号(后面会讲到是进行系统清零时使用的)。

- DDR retention控制。

- PL对CSU的三个可编程设置。

最后这部分讲GPI和GPO部件描述可能比较奇怪,总的来说GPO和GPI相当于PMU的IO口,是连接到其他器件上的接口,这些接口大部分都有固定用途,例如连接到别的处理器去接收其服务请求,上电请求等等功能,我们后面会讲这部分。最后还有一张PMU的整体结构框图:

实际上PMU的核心部件都放在这张图上了,我稍微解析一下:首先PMU的核心是三重冗余处理器,图中处理器那里有两个虚框就代表着三重处理器。而三重处理器连接外部都需要通过Voter表决权来实现,这也是三重冗余的实现核心。其次来看左半部分,有128KB RAM,AXI互联模块,PMU全局寄存,这部分是PMU处理器对外部器件和PMU RAM访问的核心,也是外部访问PMU RAM和PMU全局寄存器的核心。最后则是右半部分,包括PMU IO单元,里面有GPI和GPO以及中断控制器,从外部来的中断,电源请求以及PMU对外部的系统级控制信号都是走的这部分。还要一部分专用PS IO会走别的线进入PMU就不说了,主要我没看到是用在什么地方的。

6.2 Functional Description 功能性描述

这一节就要紧接着上一节对PMU的介绍来详细描述PMU的各部件功能了,这里首先描述了PMU的核心功能:

- 本节概述了PMU内的功能

- 在POR后和CSU复位释放之前执行事件序列。包括以下功能。

- 使用系统监视器检查电源水平,以确保CSU和LP域的其余部分正常运行。

- 初始化PLL的默认配置及其潜在旁路。

- 触发并排序必要的扫描和MBIST。

- 此阶段的捕获和信号错误。错误ID可以通过TAG读取。

- 释放CSU复位。

- 在应用程序和实时处理器的睡眠状态期间充当其代表,并在其唤醒请求后启动其通电和重新启动。

- 始终保持系统电源状态。

- 处理不同块的通电、断电、重置、内存内置自修复(MBISR)、MBIST和扫描归零所需的一系列低等级事件。

- 在睡眠模式期间管理系统并基于各种触发机制唤醒系统。

- PS级错误捕获和传播逻辑。

6.2.1 PMU Processor PMU处理器

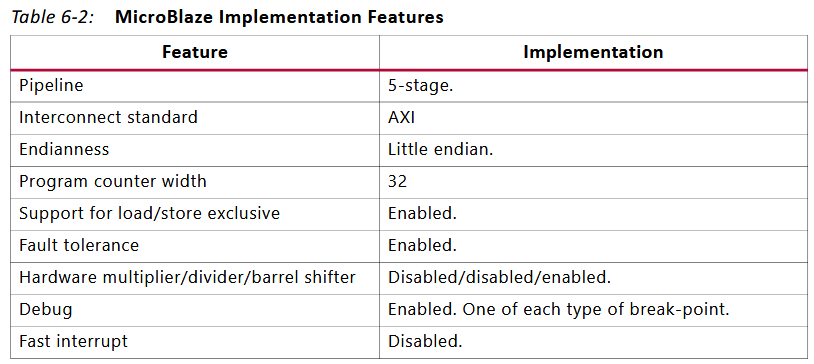

我们之前提到过PMU的三重冗余处理器,这里只是稍微详细说了一下,比较重要的有两点,首先PMU的处理器是没有Cache的,只能直接访问PMU RAM。其次,尽管PMU RAM可以被外部器件访问,但是该访问必须在PMU的处理器处于休眠状态时进行,否则访问可能得不到回应或者导致系统错误。这里同时给出了PMU处理器的特性表,不过意义不怎么大:

6.2.2 PMU Processor Interfaces PMU处理器接口

由于PMU本身就可算作一个单独处理器模块,那么就必须有供给该处理器使用的数据接口,用来满足其数据和指令的读写以及与外部器件的交流。这一节大致总结了PMU处理器的接口,可以对应PMU框图中除了处理器外的部分,我这里翻译如下:

PMU提供输入/输出信号,这些信号按功能分组到以下接口中。

- 32-位AXI主接口,连接到低功耗域(LPD)互连,允许PMU访问其他PS资源,包括SL CR寄存器和IPI块

- 32-位AXI从机接口,允许外部处理器访问PMU全局寄存器和PMU RAM。

- PMU时钟和重置信号

- 电源控制接口连接到PS内的所有电源岛

- L2, OCM, and TCM RAMs

- APU_Cores [3:0].

- Dual-core Cortex-R5F® real-time processor.

- USB0 and USB1.

- GPU pixel-processor (PP) PP0 and PP1.

- Full-power and PL domain crossing bridges FPD和PL的互联桥

来自GPIO, RTC, APU GIC, RPU GIC,和USBs的唤醒接口

- 中断接口

- 设备复位控制接口

- 内存BIST(内建自测)和BISR(内建自修复)控制接口

- 其他杂项接口,包括电源监视器接口

- 错误捕获和传播接口

这里着重说了GPI1和GPO1寄存器中连接MIO的几个引脚,GPI和GPO是PMU的输入输出寄存器组,后面还会着重讲这部分,这里就不说了。

6.2.3 PMU Clocking PMU时钟

这一小节讲了PMU的时钟是来源于位于PS SYSMON中的内部环形晶振(IRO),工作在180MHz,而且该时钟在VCC-PSAUX电源达到规定电压后就会开始工作。

6.2.4 PMU Reset PMU复位

这节讲了PMU的两种复位方式,一种是上电复位POR,这种复位方式会复位PMU中的所有部件,在POR后PMU会执行SCAN和BIST来清除LPD和FPD。另一种系统复位SRST则只会复位PMU的处理器,互联模块以及小部分的本地和全局寄存器,会保留系统的供电状态。

6.2.5 PMU RAM

PMU RAM是为了扩展PMU功能而设计的,可以用来存放用户代码和数据的128KB带有ECC的RAM,由于PMU ROM是被固化在PMU中的,不能够进行调整,想要PMU实现更复杂的功能就需要使用PMU RAM。而使用PMU RAM也有一定限制,就是PMU RAM只能字访问,使用4个字节进行读写,还有的限制就是外部访问PMU RAM时需要使PMU处理器处于休眠状态,本节还描述了PMU RAM的访问优先级,如下:

- PMU处理器数据读写

- PMU处理器指令获取

- 外部访问

6.2.6 PMU ROM

PMU ROM是存放有关PMU最基础数据以及代码的部件,不能进行更改,其中的代码是整个MPSOC系统启动的关键,我这里把原文翻译来了解其作用:

PMU包括一个ROM,其中保存了PMU的引导代码、其中断向量以及PMU可以根据请求执行的服务例程。PMU ROM负责PMU内的各种功能。以下是由ROM代码执行的任务列表。

- 引导前任务

- 清除PMU RAM

- 启用系统监视器并检查LPD供电。

- 使用初始设置配置PLL。

- 触发和排序必要的扫描和BIST来清空PS(应该指PS的内存和触发器)。

- 释放CSU复位。

- 启动后任务

- PS内的上电和掉电域。

- 启用和控制内置自我修复(BISR)。

- 根据请求或作主电源设备上电时使复位部分模块。

- 根据请求执行固件代码。(指的就是用户编写的代码PMU firmware)

6.2.6 MBIST Functionality 内存内建自测功能

内存内建自测功能是用来测试MPSOC的PS端各个部件的内存是否正常工作的一种测试技术,实际上说是测试MBIST还有清空内存的功能,这些测试单元由PMU进行控制,主要的测试或清空的内存有这几个:

- APU和RPU核心

- CAN,USB和GEM控制器

- GPU,PCIe,SIOU

- PS-PL的互联桥RAM

这四个部分都有对应的MBIST控制和状态寄存器:

- MBIST_RST rw

- MBIST_PG_EN rw

- MBIST_SETPU rw

- MBIST_DONE ro

- MBIST_GOOD ro

6.2.7 Scan Clear Functionality 扫描清除功能

扫描清除功能这部分内容我有点没太看懂,这里就结合AI分析来说一下。总的来说,SCAN Clear这个功能是用来和MBIST一起实现归零化任务的,也就是使得整个MPSOC中的数据都归零,内存的归零是使用MBIST实现的,而触发器中实际上也含有数据,这些数据的清零就是SCAN Clear实现的。MPSOC系统中只有PMU和CSU能够控制扫描清除引擎,而其中只有PMU能监测扫描过程,CSU则只能启动,且在每个功耗域都有各自的扫描引擎存在。此外,这里还有一部分有关实施LP域清除扫描的复位指南,比较复杂,这里不再描述了,具体在第116页。

6.2.8 PMU I/O Registers PMUI/O寄存器

这一节以及下面的几节实际上都在讲PMU的输入输出功能,这小节算是个总览,主要是给出了PMU中所有寄存器的地址映射以及大小,还要访问权限,全在下面这张图中了:

PMU_IOMODULE寄存器组里有很多关键部件,如中断控制器控制寄存器,GPI{0:3}, GPO{0-3}, 以及PIT0-PIT3。而PMU_GLOBAL寄存器赋予了PMU进行中断控制和触发PMU服务的功能。

6.2.8 PMU Global Registers PMU全局寄存器

PMU全局寄存包含了一大堆PMU控制外界部件的寄存器,由于数量实在太多不可能一个一个解析,我大致看了下有这么几个种类:电源控制类(上电请求,使能,失能,屏蔽,状态),错误控制类(错误状态,使能,失能,屏蔽),电源分离类(使能,失能,屏蔽,状态),复位控制类,以及一些其他杂七杂八的寄存器,详细的可以查看这一章最后的Register Overview的部分。

6.2.8 PMU GPIs and GPOs

我们前面说过GPI和GPO是PMU用来与外界部件进行数据沟通的寄存器,GPI和GPO都各有4组。我感觉这里把GPO,GPI和全局寄存器分开的原因主要是GPO和GPI针对的是MPSOC中别的模块的请求或者控制,例如APU,RPU的上电,复位,又或者直接连接到MIO,都是针对SOC上的别的模块的;而全局寄存器则主要保存一些全局的错误中断状态,又或者控制和监控各个电源域,大部分不是针对单个模块的,所以把他们分开成了两组。GPO和GPI的部件也非常的多,各4个总共8个寄存器都有不同的功能,这里我也稍微归纳一下:GPI0和GPO0为PMU处理器专用的,具体用来干什么我没看到。GPI1用来监控PS中各部件的苏醒请求,还有6个脚连接到MIO用来捕获外部苏醒事件。GPO1这用来配置PMU的PIT以及标示PMU处理器的一些状态。GPI2主要用来监控电源控制请求,例如APU和RPU的断电请求和热复位请求,还有一些和DEBUG相关的寄存器。GPO2大部分的位都被保留了,只有五个被使用的位我也没太理解是干嘛的,这里就不谈了。最后的GPI3和GPO3都是连接到PL的,也不说了。

6.2.9 PMU Interrupts

PMU在PMU ROM中固化了中断向量表以及中断优先级,而PMU处理器共有23个中断源(应该是一个32位的中断状态寄存器,有9位被保留了),这些中断的优先级和对应的服务程序被PMU ROM所默认设置,但是也可以通过PMU Firmware来更改,从而更改优先级和向量的指向(例如指向PMU RAM),由于比较重要,我这里还是把表贴一下:

6.2.10 PMU Error Handling and Propagation Logic PMU错误处理与传播逻辑

这一节内容有关PMU处理系统运行中的错误,我也没有完全看懂,所以这一节也只是大致说一下。PMU负责捕获,报告并处理系统中的所有错误,为了实现对这些错误的捕获,控制以及处理,PMU中有两组寄存器来负责管理这些错误,一组后缀是ERROR_XXXX_1另一组是ERROR_XXXX_2,例如ERROR_STATUS_1,ERROR_STATUS_2,或者ERROR_POR_MASK_1,ERROR_POR_MASK_2,都是PMU全局寄存器的一部分。一旦这些错误发生就会产生中断(但是我没看到中断表里面有写),通过配置这些全局寄存器并读取对应寄存器的值就能够实现对错误的发现和控制,而且还要注意的是一旦错误产生必须显式的去给对应的error status寄存器写1才能清除该错误状态,否则即使是系统复位和内部POR都不能清除错误状态。这里还有一部分内容我不太好归纳了就偷懒贴下翻译:

对于错误处理逻辑处理的每个错误,您可以决定在错误发生时应采取什么操作。可能的情况是以下选择之一或组合

- 在设备上断言PS_ERROR_OUT信号。

- 生成对SAL处理器的中断(PMU_Int)。

- 生成系统重置(SRST)。

- 生成通电重置(POR)

每个ERROR_STATUS寄存器都有四个掩码寄存器(ERROR_STATUS_1 and ERROR_STATUS_2)。这些屏蔽寄存器可用于启用POR, SRST, PMU中断(如果安装了Firmware),或发送PS_ERROR_OUT信号。要设置屏蔽,请将1写入ERROR_INT_EN寄存器(ERROR_INT_EN_1 or ERROR_INT_EN_2)的适当位。要清除屏蔽,请将1写入ERROR_INT_DIS寄存器((ERROR_INT_DIS_1 or ERROR_INT_DIS_2))的适当位。当选择在发生特定错误时中断PMU的选项时,应该有用户Firmware来处理错误。否则,将发生无实体错误。信号状态可以根据需要解除屏蔽。表6-12列出了PS_ERROR_OUT器件引脚信号的所有可能的错误源以及ERROR_SIG_MASK_n掩码寄存器的相应复位状态。所有其他错误掩码寄存器均设置为1(已屏蔽)。

图我就不贴了因为实在太长了,详情请看第123页。

小节

PMU的内容实在太多了,这一次只是讲完了PMU的构成以及刚刚部件的作用,具体的PMU到达该如何运行和使用还没有讲,我看下篇幅感觉还是留在下次讲了,我们系一篇随笔再见。

浙公网安备 33010602011771号

浙公网安备 33010602011771号