存储器(4)动态RAM DRAM

动态RAM

利用电容存储0,1:有电荷为1,无电荷为0

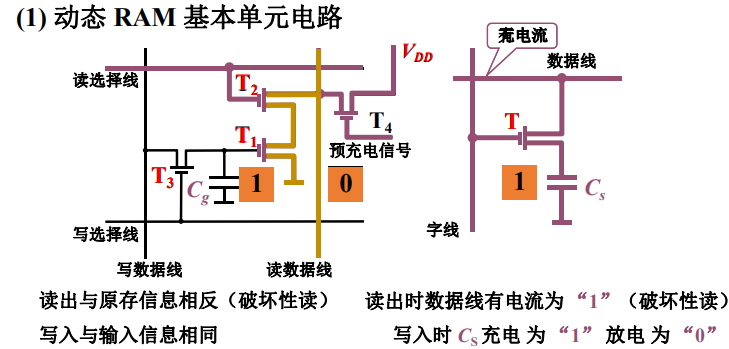

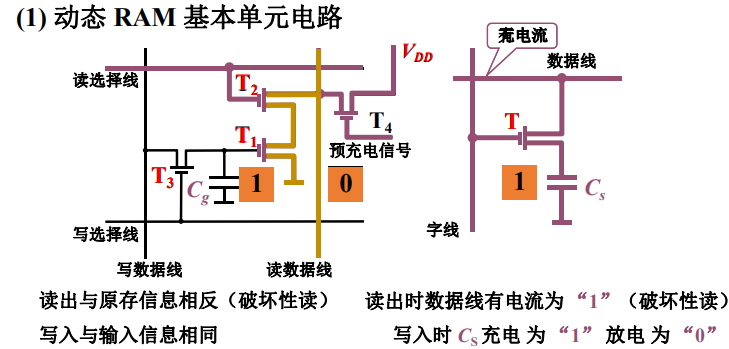

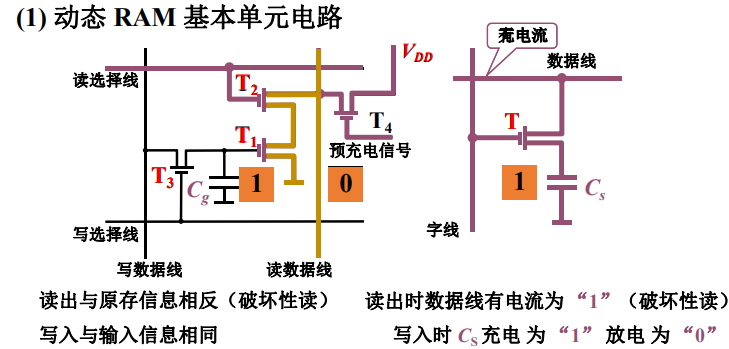

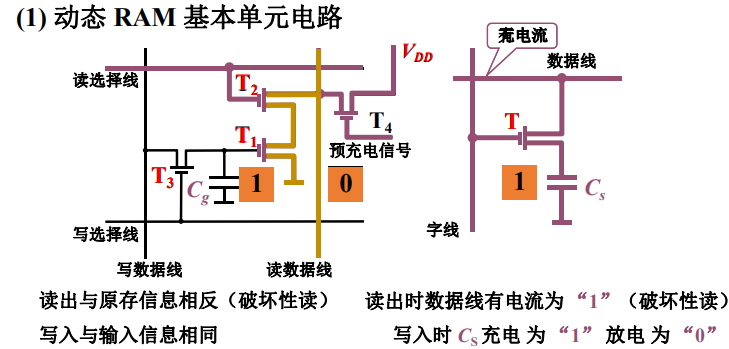

三管动态RAM:

读操作:

预充电信号使得T4开关导通,使得读数据线的信号为1,高电平,读选择线为高电平使得T2开关导通

- 假设Cg中无电荷(存储的为0,低电平),则T1开关不导通,读数据线上的数据始终是1,与原存信息相反

- 假设Cg中有电荷(存储的为1,高电平),则T1开关导通,由于T1接地,读数据线上的数据是0,与原存信息相反

写操作:

写选择线为高电平,激活T3,这个时候写数据线上的数据就会被传到到Cg里面(充电或放电),实现数据的写入,写入和输入信息相同。

单管动态RAM

字线(选择线,相当于x或y译码选择线)为高电平,则T开关被激活,此时是否对该存储单元读写还需要看数据线是否导通

- 若Cs中存储的是1,则数据线上有电流;如果存储的是0,则没有电流.,以此完成读操作

- 写入时,若数据线为1,则相当于充电,数据线为0,则相当于放电,以此完成写操作

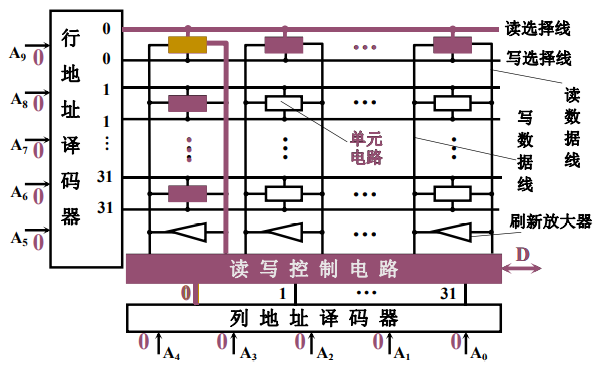

动态RAM举例

三管动态RAM :Intel 1103

原理和重合法基本差不多,即行地址译码器和列地址译码器同时选中的时候存储单元被导通。但是在行地址译码里,每一条地址线都分了读选择线和写选择线,并且添加了刷新放大器,避免电容漏电导致数据失效

有什么不对或不懂的可以提出来一起讨论呀

浙公网安备 33010602011771号

浙公网安备 33010602011771号