存储器(3):静态RAM SRAM

静态RAM

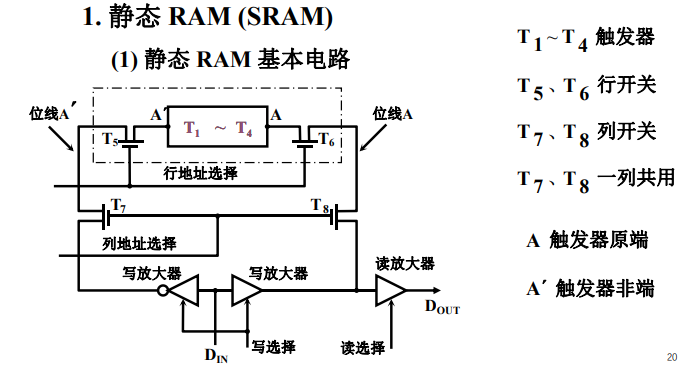

基本单元电路结构介绍:

- T1~T4 实现存放0,1,双稳态触发器,两端的数据是相反的,即一端为0,另一端为1

- T5,T6由行地址给出,如果行地址给出,则T5,T6开关打开(但是还没有导通)

- T7,T8由列地址给出,只有当行,列地址都给出的时候,才能实现读写操作

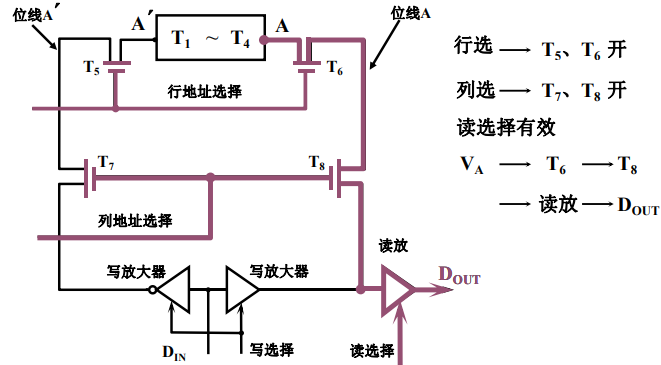

读操作实现:

当T6,T8打开后,A端信号通过T6,T8传输到读选择三态门实现输出

同时,对A'信号而言,T5,T7开关也打开 ,但是由于到写放大器处无法传输通过,因此无法传输

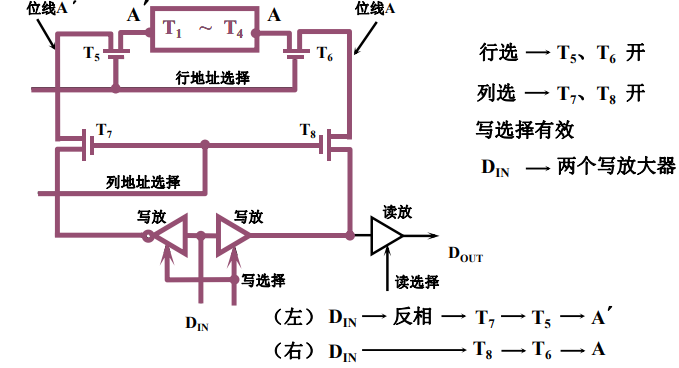

写操作实现:

数据从Din 输入,经过两个三态门,向A'和A中分别写入相反的数据

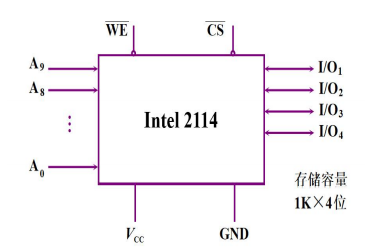

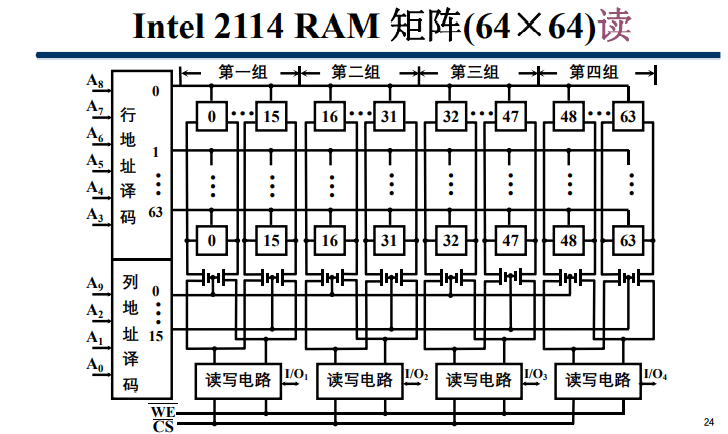

静态RAM芯片举例:Intel 2114

IO接口为4位,则每一次需要进行4位的读写操作

对于行地址译码器而言,其共有64根导线,每一次译码后只激活一根导线,

对于列地址译码器而言,其共有16根导线,每一次译码后,需要激活4根导线

因此,将64*64矩阵,在列方向上分为4组,每一次译码后,激活每一组的对应位置上的相同导线

例如,行地址译码为0,则第0行所有存储单元被选中,列地址译码为0,则每一组第0列所有单元被选中,共4位,然后根据WE和CS信号,完成读写操作

有什么不对或不懂的可以提出来一起讨论呀

浙公网安备 33010602011771号

浙公网安备 33010602011771号