存储器(2):主存储器简介

主存储器

技术指标:

(1)存储容量 存储器的带宽 主存 存放二进制代码的总位数

(2)存储速度

- 存取时间:从存储器给出地址直到得到稳定的数据(输入或者输出)分为读入时间和写入时间

- 存取周期:连续两次独立的存储器操作所需要的最小的时间间隔

(3)存储器的带宽:位/秒

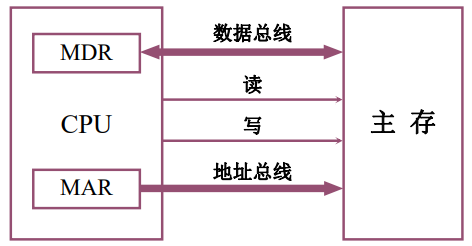

主存和CPU的联系:

MDR:Memory Data Regisiter(数据寄存器)

MAR:Memory Address Regisiter(地址寄存器)

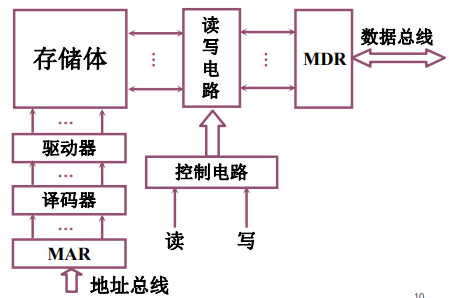

主存的基本组成:

主存中存储单元地址的分配

- 大端模式:低地址存放高位

- 小端模式:低地址存放低位

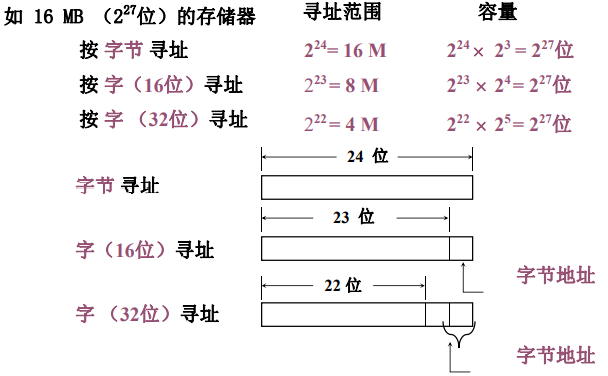

寻址方式:

- 按字节寻址:1字节 = 8位

- 按字(16位)寻址: 1字 = 16位

- 按字(32位)寻址: 1字 = 32位

(字节地址理解为在一个字内定位字节地址)

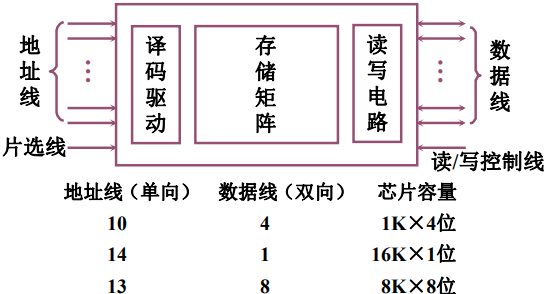

半导体存储芯片简介:

(1)片选线:指出访问是不是在这个芯片中

- CS:芯片选择信号,低电平有效

- CE:芯片使能信号,低电平有效

(2)地址线:单向(写入),给出操作对应芯片内存储单元地址

(3)数据线:双向(读出,写入)

(4)读写控制线:控制数据写入,读出

- 一根信号线:WE(低电平写,高电平读)

- 两根信号线:OE(允许读),WE(允许写),均为低电平有效

(5)芯片容量计算方式:

- 设地址线位10位,数据线为4位,则芯片容量为1K*4 位

- 设地址线位14位,数据线为1位,则芯片容量为16K*1位

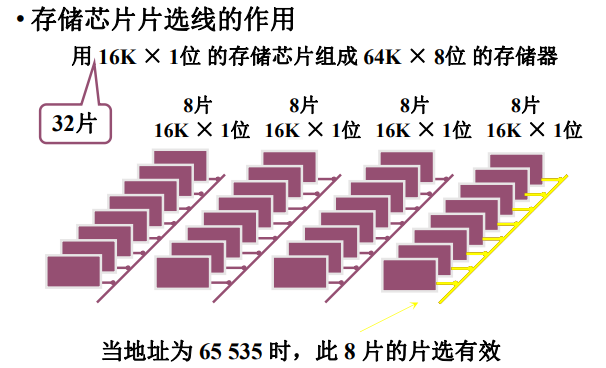

芯片片选线的作用:

如图,每8个芯片作为一组,每次访问的时候访问同一组8个芯片的同一个位置,从而实现8位的数据读取和写入

要组成64K的数量,需要四组共32个16K*1位的芯片,对于这四组芯片,对应的地址分别为

- 第一组:0 ~ 16K-1

- 第二组:16K ~ 32K-1

- 第三组:32K ~ 48K-1

- 第四组:48K ~ 64K-1

当给出的地址信号在其中的某一区间时,相应的那一组数据的片选信号就会被激活,其它三组的片选无效

半导体存储芯片的译码驱动方式:

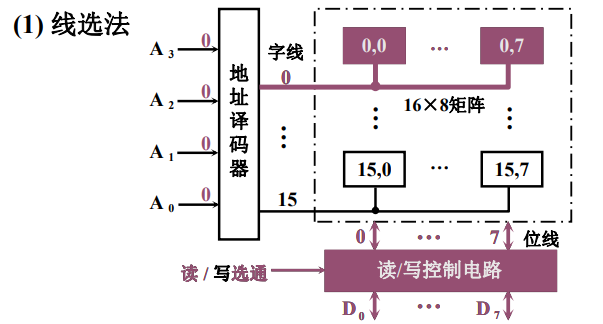

一、线选法:

利用译码器(例如2-4译码器),输入地址后经过地址译码器,激活唯一的字线,并找到相应的存储单元(一条字线对应一个存储单元)

问题:每一个存储单元需要一条字线,不利于大容量存储。

二、重合法:

将地址分为二维,即行地址和列地址,分别进行译码,行地址和列地址都只能同时一条有效

行地址经过移码后只有一条线有效(该条线上所有的存储单元被选中)

列地址经过译码后也只有一条线有效,两条线重合的存储单元被导通,数据传到数据线上完成传输

实际上,(0,31)的数据也会输出,但是由于该存储单元未被同时选中,所以数据不会送到数据线上来

有什么不对或不懂的可以提出来一起讨论呀

浙公网安备 33010602011771号

浙公网安备 33010602011771号