总线与输入输出子系统

总线:一种用来连接各功能部件并承当部件之间信息传送任务的信息公共通路。

接口的功能与类型

I/O接口:主机和外设的衔接部分,位于总线和外部设备之间。

I/O接口的基本功能:

设备寻址:接收CPU送来的地址码,选择接口中的寄存器供CPU访问。

数据缓冲:实现主机和外设的匹配速度,缓冲深度和传送的数据量有关。

预处理功能:串 —并格式转换(串口);数据通路宽度转换(并口);高—低电平转换

控制逻辑功能:接收主机CPU的控制命令、保存状态信息,协助主机实现对I/O传送操作的控制。

对接口中寄存器编址:

单独编址:为接口中的每个寄存器(I/O端口)分配独立的端口地址(可与主存地址重叠)

与主存统一编址:把接口中的寄存器(I/O端口)当成特殊的主存单元,并与其他主存单元统一编址。I/O端口地址将占据主存的部分地址空间。

I/O接口的分类:

按数据传送格式划分:

并行接口:接口两侧均并行传输数据;

串行接口:接口与外设一侧串行传送;

按时序控制方式划分:

同步接口:接口与系统总线的信息传送采用同步方式控制;

异步接口:接口与系统总线的信息传送采用异步方式控制;

按I/O操作的控制方式:

PIO 接口,程控方式;

中断接口,可采用查询方式;

DMA接口,可插入中断做DMA善后处理;

IOP/PPU接口,专用处理器/机方式。

总线

总线的特性:

物理特性:几何尺寸、形状、引脚数、排列等;

功能特性:规定信号线的功能;

电气特性:信号方向,电平范围;

时间特性:何时有效,持续时间、时序约定。

总线的逻辑连接及作用:

单总线结构:它是部件之间信息交互的唯一通路;竞争激烈、响应慢。

多总线结构:有多组总线,分摊负载,传输效率高;

总线的分类:

按功能分类:内总线(芯片内)、局部总线(板卡内)、系统总线(计算机内)、外总线(多机集群)

按数据传送格式分类: 并行总线、串行总线;

按时序控制方式分类:同步总线、异步总线;

总线的标准

为何要制定总线标准?

为了使不同部件都连接到总线上并与之交互通信,就必须制定公共的技术规范。

便于灵活组成计算机系统。

采用总线结构的好处:

技术工程角度:简化硬件设计,易于扩充;

从用户的角度:具有“易获得性”;

从厂商的角度:易于批量生产、降低成本;

总线标准包括哪些方面?

机械结构规范、功能规范、电器规范

总线的设计要素

总线宽度与频率:

总线的宽度:总线各功能组中的信号线数量,32或64;

总线的频率:每秒数据传输的次数,33M、66M、133M等;

带宽:![]()

f -总线频率、w-总线位宽、d-工作模式、L-通道数、E-编码方式

总线周期与操作过程:

总线周期:通过总线完成一次完整数据传输的时间;

主设备:申请并掌握总线权限的设备;

从设备:与主设备对应的设备。

总线操作的基本步骤:

主设备申请总线,仲裁器裁决并批准;

主设备掌握总线,启动总线周期,初始化;

从设备响应,主从设备之间的数据传输;

主设备释放总线,结束总线周期。

总线上的数据传输模式:

单周期模式:

传输特点:申请 1 次,只分配 1 个总线周期,只传送 1 次数据。

突发模式:

传输特点:申请 1 次,分配多个总线周期,可传输多个数据字。

总线的时序和控制

同步总线:由统一的时序信号控制总线上的传送操作。在固定时钟周期内完成传送,由同步脉冲定时打入。

异步总线:无固定的时钟周期划分;总线周期由传送的实际需要决定;以异步应答方式控制总线传送操作。

扩展的同步总线:以时钟周期为时序基础,允许总线周期中时钟数可变。

时钟周期:CPU一步操作(1 次内部数据通路传送)时间。

总线周期:经过总线的一次数据传送(访存)时间,通常包含若干时钟周期。

工作周期:指令周期中的一个操作阶段。可包含多个总线周期。

总线的仲裁

总线上可能连接多个设备,为了解决总线控制权的竞争问题,必须有总线仲裁部件,以某种规则裁决、分配总线的控制权。

多个主设备提出总线控制请求时,一般采用优先级或公平策略进行仲裁。

按照总线仲裁电路的位置不同,仲裁方式分为:集中式仲裁;分布(散)式仲裁;

集中式仲裁:

集中式仲裁中每个模块有两条线连到中央仲裁器:一条是送往仲裁器的总线请求(BR)信号线;一条是仲裁器公司送出的总线授权(BG)信号线。

常用的三种集中式仲裁方式:

链式查询集中式总线仲裁:

总线授权信号被依次串行地送到所连接的外围设备上进行比较。

离总线控制器的逻辑距离决定,越近优先级越高。

计数器定时查询方式总线仲裁:

当查询计数器计数值与请求的设备编号一致时,中止查询,该设备获总线控制权。

优先级灵活:计数器初值、设备编号可通过程序设定,优先次序可用程序设定,优先次序可用程序控制。

独立请求方式总线仲裁:

各设备均通过专用请求信号线与仲裁器连接,且通过独立的授权信号线接收总线批准信号。

分布式仲裁:

设备需要控制总线时,发请求信号,并监听其他请求信号,各设备等判别自己的优先级、以及能否在下一个周期控制总线。

缺点:信号线复杂; 优先:防止总线时间浪费;

PCI(Peripheral Component Interconnect,外围组件互连)总线:一种高性能32/64位同步总线,地址信号和数据信号复用,可扩展至64位。Intel公司于1991年底提出,受到许多微处理器和外围设备产商的支持。

PCI总线可以在主板上和其它总线(如 ISA、USB等)相连(桥接器、芯片组),以适应高、低速外围设备。

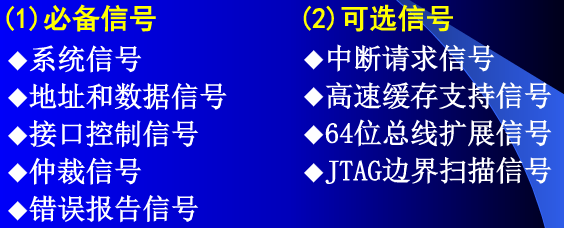

PCI总线的信号组成:

中断方式与接口

中断基本概念:

在程序运行过程中,如果发生某种随机事态,CPU暂停当前程序(被中断),转而执行该事态对应的服务程序,结束后再恢复源程序的执行。 特征:程序切换 + 随机性;

中断的实质:

程序切换:方法:保存断点,保护现场;恢复现场,返回断点。时间:一条指令结束时切换。保存程序的完整性。

中断的特点:

随机性:随即发生的事态(按键、故障); 有意调用,随机请求与处理的事态(调用打印机);随机插入的事态(软中断指令插入程序任何位置)。

中断和子程序调用的区别:

子程序的执行由程序员事先安排,而中断服务程序的执行则由随机中断事件触发。

子程序的执行受主程序或上层程序控制,而中断服务程序一般与被中断的现行程序无关。

一般不存在同时调用多个子程序,但可能发生多个外设同时向CPU发出中断服务请求的情况。

DMA基本概念:

定义:直接依靠硬件系统来控制主存与外设之间的数据传送,传送期间无需CPU干预,传送结束后通常用中断方式通知CPU

浙公网安备 33010602011771号

浙公网安备 33010602011771号