Verilog语言学习(自用

HDR:硬件描述语言

高级程序语言,通不过对数字电路和系统描述,可以对数字集成电路进行设计和验证

主要功能:数字集成电路设计工程师可以根据电路的特点,采用层次化的设计结构,将抽象的逻辑功能用电路的方式进行实现。

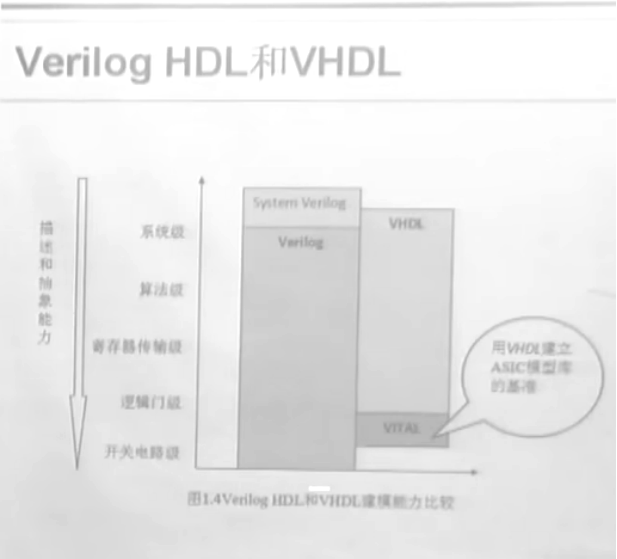

VerilogHDL(美):思维开放-->语法形式比较灵活,宽松度高(不适合大规模集成设计,容易出问题):开关级强,系统级弱,要辅助

VHDL(欧洲 ):思维严谨-->语法要求严格(合适):不具备开关级别,但是系统级有优势

目前主要的两种HDL语言,均被采纳为ieee国际标准

目前基本上都是联合设计,高层次和关键部分用VHDL

中规模用VERILOG HDL,联合两方的优势

VerilogHDL:

2001:语言的一个固定过程

2005:提出的东西,解决集成电路的系统级的问题:

数学问题变成数字和模型的问题:数字仿真,集合算法和硬件

两个重要标准:1995/2001标准

集成电路的生命周期18个月

verilog:

Verilog的30%语言用于设计,其余的语言基本都是在功能仿真阶段

不是跟C语言一样可以用所有的语法

设计过程中对语法风格有要求,不同分支对语法集有区别

语言正式学习:

- 出身来源于C语言,设计方法与C完全不一样

- 语法形态和C语言很相似,设计方法在根本上与C完全不一样

语言要素:

- 空白符(空格符\b,制表符\t,换行符和换页符):程序易读性

- 注释符:同C语言 //单行注释 /*多行注释*/:eda所有的注释和命名方式全部写成英文:保证兼容性

- 标识符:用来命名信号名,模块名和参数名等,只能用字母,数字,$和下划线:对字母的大小写敏感,第一个字符必须是字母和下划线

- 转移标识符:\后面可以加非法字符,来通过系统的识别

- 关键字:always等(存留):所有的关键字是小写的

- 不同颜色的提示为不同的关键字:保留or自定义

- 信号线:基本逻辑数值状态

高于0.7v:1 低于0.7v:0

两个逻辑灯对其驱动:不定状态x

只有总线形式,对外呈现高阻状态:高阻态z

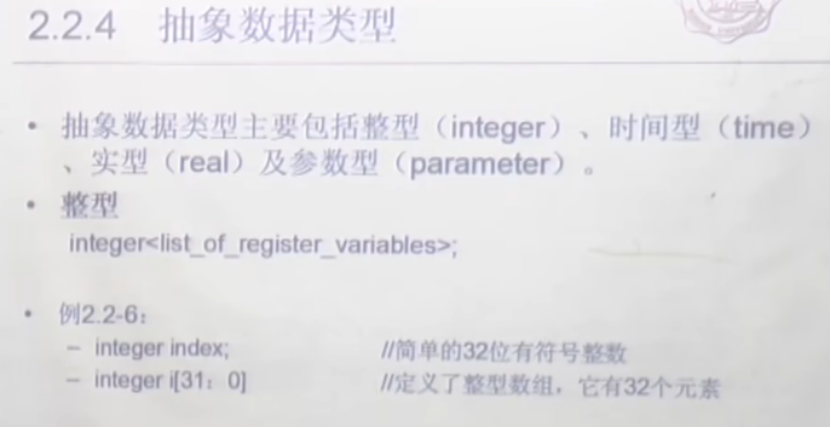

整型:

Size:表示有多少位,几根线,2的几次方,规模:要写,确立具体形态

用的最多:二进制和十六进制(忽略八进制和十进制):十六进制集成度高

<位宽>`<几进制数><数值本身>

整数和小数部分分开:二进制表示法:2** n.2**-n

小数点:定点和浮点两种表示法

实数及其表示:十进制表示法/科学计数法7.5e10

非法形式:小数点左边或者右边没有数

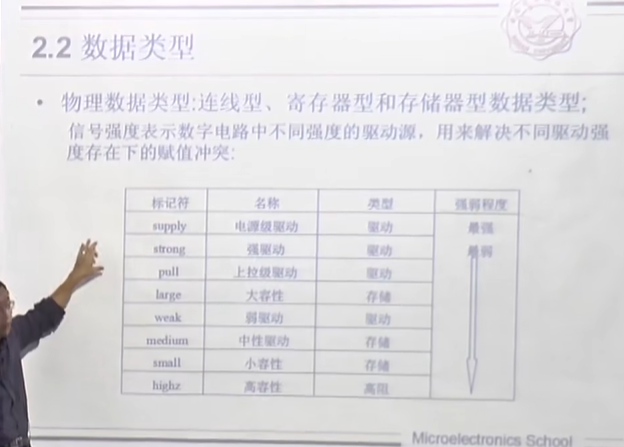

驱动能力不同,连接的器件不同(本科阶段可省)

物理数据类型:wor/ tri

Range1:存储位宽

Range2:存储深度

Range[7:0]mem1[255:0]:定义了一个有256个8位存储器mem1;

-----------------------------------------------------------------------------------------------------------------------------------------------------------------------

浙公网安备 33010602011771号

浙公网安备 33010602011771号