verilog学习笔记1

第一课的学习任务是:

①搞清楚常用语法,重点是赋值方式这部分,对应实际电路和实现的思路

②能够写出ppt里的简单程序

③会使用modelsim软件、编写testbench,验证自己的代码

一、数据流建模

1、连续赋值语句

格式是assign a = xxx;被赋值的变量必须是wire类型

语句定义了逻辑关系,可以实现所有的组合逻辑

语句之间是并行关系,结果不受位置影响

只能在语句块之外使用,不能在语句块之内使用

二、行为级建模

1、过程语句

过程语句是always 和 initial语句块中的语句

一般是用begin-end,是串行运行的,并行语句块一般不用,因为不能综合

语句块中赋值的对象必须是reg类型的

2、过程赋值语句

指在过程语句中(或者说语句块中)使用的赋值语法

分为阻塞型和非阻塞型

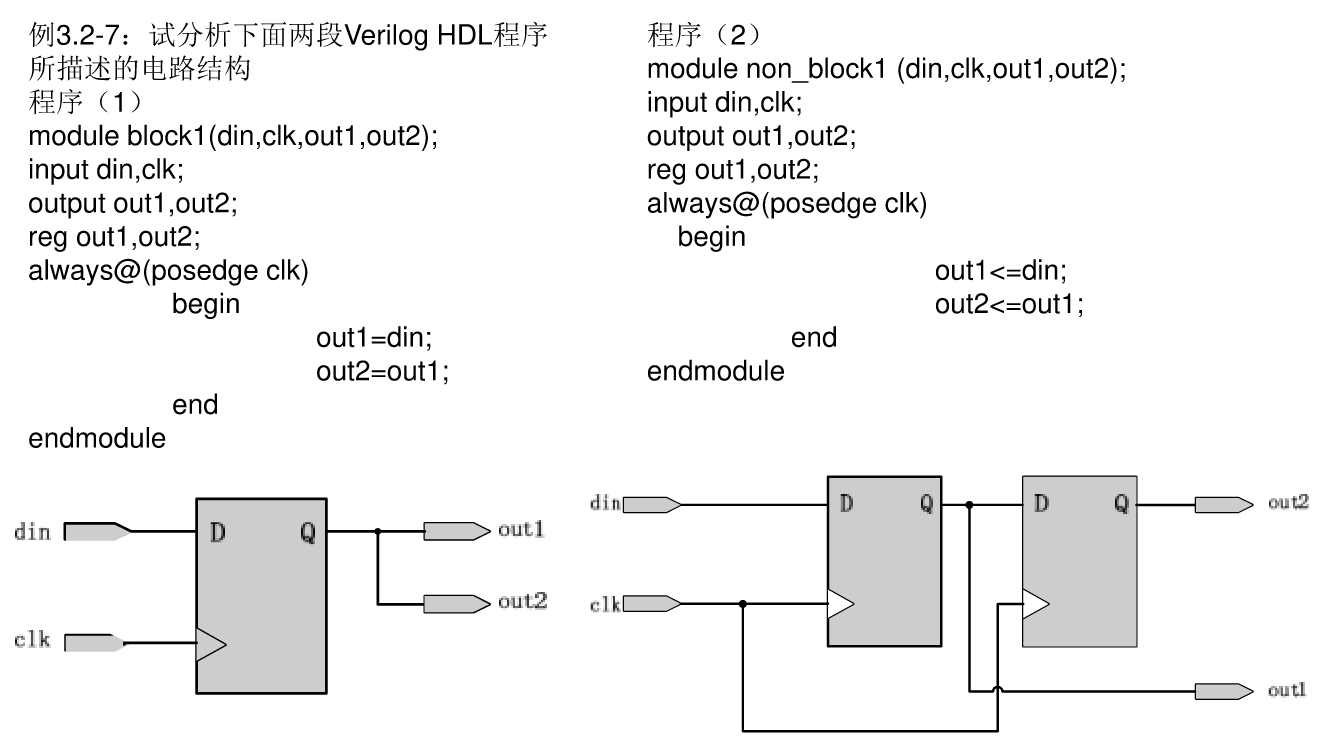

①阻塞型赋值语句 使用“=”

b = a;

是最简单的串行运行规则

②非阻塞型赋值语句 使用“<=”

b <= a;

区别:

3、过程连续赋值语句

不可综合,大部分时候应该也不会用,测试的时候估计会用

语句块中的语法,区别于语句块外的连续赋值语句。

assign a = xxx;

和最开始的连续赋值语句差不多

可以在语句块内规定一个组合电路,实在没办法再这样用,因为完全可以在语句块外规定组合电路。

三、结构化建模

这部分似乎没有像前面一样强调变量类型的规则,但为了概念清晰,还是需要总结一下

一般来说,例化模块的输出需要是wire类型。在testbench里,需要将连接输出的端口定义为wire,而不能是reg。

如果不在testbench里面,模块有自己的输入和输出,那么output不需要定义类型,也可以作为例化模块的输出

也就是说,如果不是定义为输出的端口,即需要单独声明的变量,如果需要作为例化模块的输出,那么必须设置为wire类型

----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

最后就是整理一下modelsim的用法

1、一般来说要先给project新建一个文件夹

2、新建project,选择位置,为新建的文件夹

3、新建文件,选择verilog,一般来说,需要建一个模块文件和testbench文件

4、写好代码,compile all

5、开始仿真,注意取消勾选仿真优化

6、把信号放到wave里面,然后点击run all即可

*library不知道是什么意思,一般来说不需要新建library

默认work

在这个基础上,就可以去做一些练习题了

浙公网安备 33010602011771号

浙公网安备 33010602011771号