dc综合学习笔记3

dc在综合的时候,可以将属性和约束加到电路上:

一、设计的组成

设计、单元、连线的概念容易理解,端口port和引脚pin的概念需要区分一下。端口port一般只指设计的输入输出,引脚pin可以指设计中所有cell的引脚

具体的可以参考下图:

二、TCL介绍

本节介绍了一些tcl语法,可以用来搜索、查看、更改、设置 一些object的属性

包括指明对象,指明对象集合,进行更改、赋值,等等

只能混个脸熟,用到再查看和学习

三、层次结构和模块划分

1、模块层次的概念

soc由多个组成部分,其中数字模块,也有内在的层次

这里还提到了软核和硬核的差别。

软核一般以代码的形式存在,可以加入设计流程中,进行后续的综合,同时也可以对设计进行修改,也可以适用于多种工艺

硬核通常是DSP、内存等(其实大部分处理器也是),往往这类模块的功能固定,并且已经经过优化和验证,与某种固定的工艺绑定,不可迁移到其他工艺

2、模块划分在综合环节的意义

即使是一个数字模块,如果功能很复杂,规模很庞大,也需要划分成不同的部分,来进行设计和后续综合

这种划分在设计时就已经做好了,当然书上也提到在dc中可以进行划分,但估计我用不到

在verilog中,例化会产生新的层次,这一点很容易理解,例化一个模块,这个模块就是更低层次。

这里提到,一些符号也会产生新的层次,这一点学习verilog的时候可以注意一下原因。

下面说一个模块划分的例子:

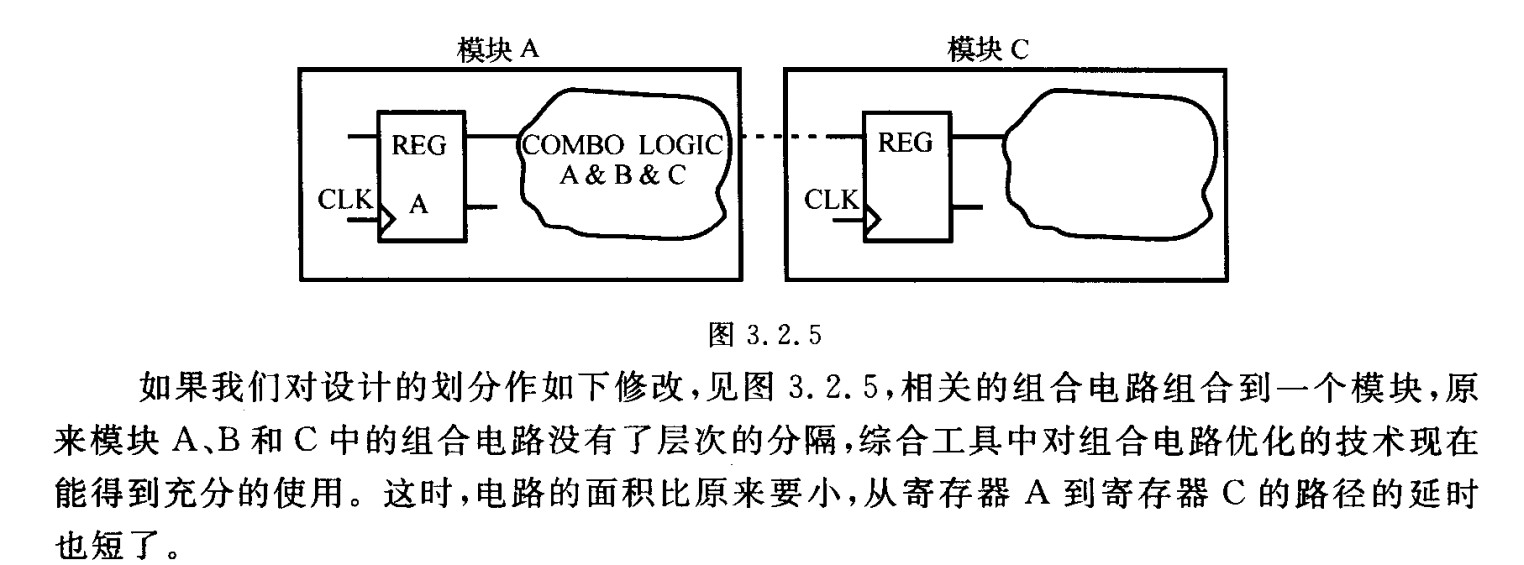

这三个模块分开综合,会导致合并后的效果变差,同时施加约束也会比较麻烦

但如果改成上图,那么优点就是,把组合逻辑放在一起能够充分发挥综合的优化功能

同时时序约束也更简单

进一步,还可以优化成下图:

这样看起来和前面那个的区别只是把寄存器放在模块的输出位置。

优点就在于,寄存器的组合逻辑部分也可以跟前面的组合逻辑模块一起综合,实现更进一步的优化

虽然理论上是这样,但是优化可想而知不会很大。这样的意义还在于有一个可以依照的规范,从而对时序约束的制定更统一

因为这样一来,每个端口的输入延时都相同了,都为前一个模块寄存器的延时

同时,分块应该避免胶合逻辑,具体就不说了,解决方式也很简单,把连接的逻辑随便并到其他模块的组合逻辑中

3、修改模块划分

这节先介绍了一般的逻辑划分方式,由于不会用到所以就不整理了,原则一般是按功能、工艺、工作类型划分,同时一个较大的模块也需要划分

不能划分成太多快,因为会影响综合的最优化,也不能分的太大块,这样增加了设计难度和时间

模块划分的命令主要通过group和ungroup实现

但估计用不到,所以也不具体展开了

浙公网安备 33010602011771号

浙公网安备 33010602011771号