dc综合学习笔记2

书的第二章讲的是RTL设计语言和逻辑综合。仍然是涉及到概念比较多的一章,具体的内容可能比较少。这一张其实也表明想要进行dc综合,对数字程序设计要有一定的理解,本书整理完后希望能继续学习一下verilog程序设计,锻炼一下编程能力。

一、程序设计语言

程序设计语言有三种不同级别的设计,分别是行为级、寄存器传输级和门级。

1、行为级描述

行为级描述是比较简单的一种建模方式,只需要将行为按照语法表现出来即可

对于行为级描述,很难直接对应具体的电路,可以认为是一种高级语言或者高级建模方式

而对应到具体的电路,是需要通过 综合 这一过程实现的,由计算机自动完成

2、寄存器传输级

寄存机传输级就是常说的RTL

RTL代码仍然不能很直观的对应实际电路,但有经验的设计者也能一下看出电路有几个寄存器,大概是什么结构

而具体的电路实现,主要是寄存器之间的组合电路部分,会根据约束有不同的结构

3、结构化建模

也叫 门级描述语言 或者 门级网表

结构化建模可以很直观地对应到实际的电路,因为它的建模方式就是以逻辑门为单位,利用引脚节点来描述逻辑门的连接关系

二、逻辑综合

数字电路的设计流程:

这里注意到一个点:行为级描述虽然在建模过程中更加简单,但是行为级代码不可以直接综合,需要RTL级代码才能进行综合

这部分需要在verilog学习中深入理解一下

1、逻辑综合的基本步骤

这是老生常谈的内容了,但需要去实际的走一遍综合流程,才能更好地理解这几个步骤。比如,如果综合时使用的库中,逻辑单元不全,那么综合过程仍然是可以完成的,但会用gtech库中的逻辑单元替代,程序会提示存在未映射的单元。

书上还提到了利用HDL语言和逻辑综合进行设计的优点:

①提高设计效率

综合工具的运用加上ip核的复用

②抽象设计

设计的层次更高,庞大的门级网表交给程序生成

③设计诀窍

对逻辑单元的优化、约束,计算机也能更好地实现

④重复使用

同样的设计,即RTL代码,可以方便地用不同工艺进行实现,直接更换库即可

⑤验证方便

验证和设计用的是同一种语言(?)

⑥便携性强

设计时可以不考虑工艺,综合时通过约束来对综合结果控制

同时dc会做静态时序分析(STA),来确保时序满足约束

2、综合工具

没看懂在说什么

3、目标库和初始环境设置

映射环节,dc需要知道我们使用的是什么工艺库。这里就需要详细梳理一下dc启动文件里的指令内容。

首先会有一个set search_path ""指令,告诉dc软件,去哪里找库文件

一个重要的概念是,set link_library和set target_library指令的区别,一搜会发现有不少文章讲这个,大概看了一下

target_library一般是放标准单元库文件

link_library一般放RAM、ROM、IP等宏单元,也就是在rtl代码中例化,却不存在于标准单元库中的模块

在使用中,如果一个设计没有使用这些宏单元,只需要基础的逻辑单元进行综合,那么只需要set target_library即可,不需要设置link_library

等需要使用link_library的时候再细看功能。

----------------------------------------------

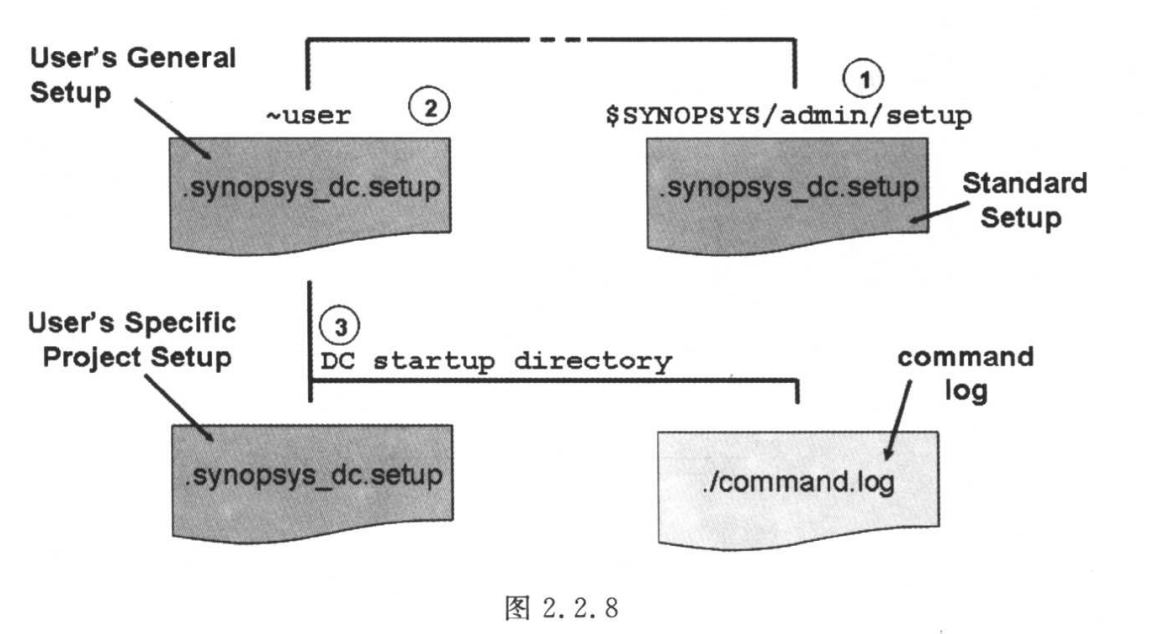

还有一个比较重要的是dc的启动文件,启动文件包含上述的set xxlibrary等内容

原本在使用中,只使用一个setup文件,就是在dc安装目录下的那个,每次需要修改都要进去改

而书中提到,setup文件不只放在一个地方,可以自己在启动目录下定义:

这里暂时不清楚用户目录这个东西是怎么定义的

所以暂时先只使用dc安装目录和启动目录的setup文件

浙公网安备 33010602011771号

浙公网安备 33010602011771号